Изобретение относится к измерительной технике и может быть использовано в системах контроля и регулирования параметров промышленных установок.

Известен фазовый компаратор, содержащий два формирователя, пять элементов ИЛИ, четыре элемента НЕ, четыре элемента И и элемент задержки [1].

Недостатками указанного устройства являются низкие точность и надежность.

Известен фазовый компаратор, содержащий JK-триггер, два элемента И-НЕ и интегратор [2].

Недостатком указанного устройства является низкая точность.

Наиболее близким по технической сущности и достигаемому результату к предлагаемому изобретению является фазовый компаратор, который содержит два Д-триггера, три интегратора, формирователь импульсов, источник опорного напряжения, два формирователя временных интервалов и два формирователя прямоугольных импульсов [3].

Недостатками указанного фазового компаратора являются низкая точность, обусловленная влиянием неидентичности формы входных сигналов, и низкая надежность.

Заявляемое изобретение решает задачу создания фазового компаратора, лишенного перечисленных недостатков. Техническим результатом, достигаемым при использовании заявляемого изобретения, является повышение точности и надежности сравнения фаз за счет исключения влияния неидентичности формы сравниваемых сигналов.

Поставленная цель достигается тем, что в фазовый компаратор, содержащий два Д-триггера и интегратор, выход которого является выходом фазового компаратора, введены логический элемент ИЛИ, выход которого подсоединен к С-входу первого Д-триггера, два JK-триггера, третий Д-триггер и логический элемент И, причем первый и второй входы логического элемента ИЛИ являются первым и вторым входами фазового компаратора и подключены соответственно к С-входам первого и второго JK-триггеров, Д-входы первого, второго и третьего Д-триггеров подсоединены к источнику сигнала логической единицы, выход логического элемента И подключен одновременно к R-входам первого и второго JK-триггеров и первого Д-триггера, прямой выход которого подсоединен одновременно к С-входам второго и третьего Д-триггеров и к J-входам первого и второго JK-триггеров, К-входы которых подключены к инверсному выходу первого Д-триггера, прямой выход первого JK-триггера подсоединен одновременно к R-входу второго Д-триггера и к первому входу логического элемента И, прямой выход второго JK-триггера подключен одновременно к R-входу третьего Д-триггера и к второму входу логического элемента И, прямые выходы второго и третьего Д-триггеров подсоединены соответственно к первому и второму входам интегратора.

Сопоставительный анализ с прототипом показывает, что заявляемый фазовый компаратор отличается тем, что в него введены логический элемент ИЛИ, выход которого подсоединен к С-входу первого Д-триггера, два JK-триггера, третий Д-триггер и логический элемент И, причем первый и второй входы логического элемента ИЛИ являются первым и вторым входами фазового компаратора и подключены соответственно к С-входам первого и второго JK-триггеров, Д-входы первого, второго и третьего Д-триггеров подсоединены к источнику сигнала логической единицы, выход логического элемента И подключен одновременно к R-входам первого и второго ЛС-триггеров и первого Д-триггера, прямой выход которого подсоединен одновременно к С-входам второго и третьего Д-триггеров и к J-входам первого и второго JK-триггеров, К-входы которых подключены к инверсному выходу первого Д-триггера, прямой выход первого JK-триггера подсоединен одновременно к R-входу второго Д-триггера и к первому входу логического элемента И, прямой выход второго JK-триггера подключен одновременно к R-входу третьего Д-триггера и к второму входу логического элемента И, прямые выходы второго и третьего Д-триггеров подсоединены соответственно к первому и второму входам интегратора.

Таким образом, заявляемый фазовый компаратор соответствует критерию «новизна».

Сравнение заявляемого технического решения не только с прототипом, но и с другими техническими решениями в данной области техники не позволило выявить в них признаки, отличающие заявляемое техническое решение от прототипа. Это позволяет сделать вывод о соответствии критерию «Изобретательский уровень».

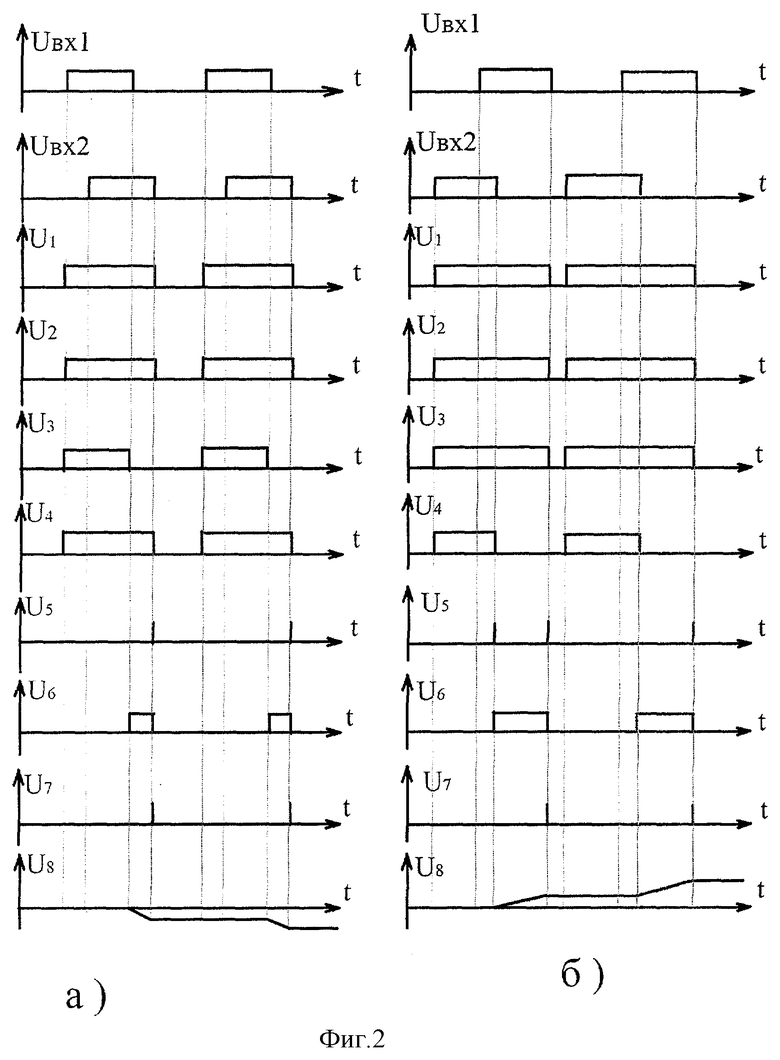

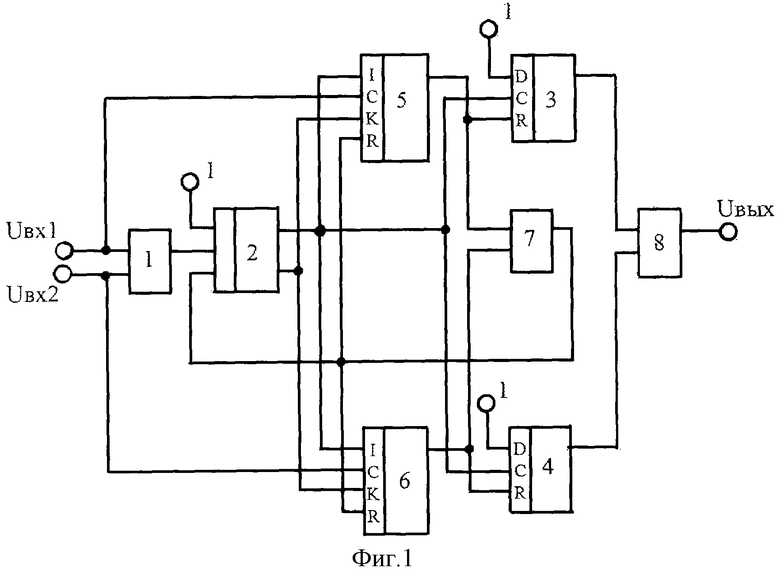

На фиг.1 приведена структурная электрическая схема фазового компаратора, а на фиг.2а, б - временные диаграммы, поясняющие его работу, причем диаграмма фиг.2а соответствует случаю, когда фаза первого сравниваемого сигнала меньше фазы второго сравниваемого сигнала, а диаграмма фиг.2б - случаю, когда фаза первого сравниваемого сигнала больше фазы второго сравниваемого сигнала.

Фазовый компаратор содержит логический элемент ИЛИ 1, три Д-триггера 2, 3, 4, два JK-триггера 5, 6, логический элемент И 7 и интегратор 8.

Первый и второй входы элемента ИЛИ 1 являются первым и вторым входами фазового компаратора и подключены соответственно к С-входам первого 5 и второго 6 JK-триггеров. Выход логического элемента ИЛИ 1 подсоединен к С-входу первого Д-триггера 2, прямой выход которого подключен одновременно к C-входам второго 3 и третьего 4 Д-триггеров и J-входам первого 5 и второго 6 JK-триггеров. Прямой выход первого JK-триггера 5 подсоединен одновременно к R-входу второго Д-триггера 3 и к первому входу логического элемента И 7. Прямой выход второго JK-триггера 6 подключен одновременно к R-входу третьего Д-триггера 4 и к второму входу логического элемента И 7. Выход логического элемента И 7 подсоединен одновременно к R-входам первого Д-триггера 2 и первого и второго JK-триггеров 5 и 6. Инверсный выход первого Д-триггера 2 подключен одновременно к К-входам первого и второго JK-триггеров 5 и 6. Д-входы первого, второго и третьего Д-триггеров 2, 3, 4 подсоединены к источнику сигнала логической единицы. Прямые выходы второго и третьего Д-триггеров 5 и 6 подключены соответственно к первому и второму входам интегратора 8, выход которого является выходом фазового компаратора.

Фазовый компаратор работает следующим образом.

В исходном состоянии на выходах элемента ИЛИ 1, Д-триггеров 2, 3, 4, JK-триггеров 5, 6 и элемента И 7 уровни напряжений соответствуют логическому нулю, на инверсном выходе Д-триггера 2 уровень напряжения соответствует логической единице. Д-триггеры 2, 3, 4 и JK-триггеры 5, 6 работают в режиме приема информации.

На первый и второй входы элемента ИЛИ 1 поступают входные импульсные сигналы Uвх1 и Uвх2, фазы которых сравниваются и равны соответственно ϕ1 и ϕ2.

Рассмотрим первый случай. Пусть ϕ1<ϕ2(ϕ1-ϕ2=Δϕ<0) (фиг.2а). На выходе логического элемента ИЛИ 1 формируются импульсы, полученные логическим сложением. Выходной сигнал элемента ИЛИ 1 подается на С-вход первого Д-триггера 2, который по переднему фронту первого импульса устанавливается в единичное состояние. Сигнал с прямого выхода Д-триггера 2 поступает одновременно на С-входы второго и третьего Д-триггеров 3, 4, которые по переднему фронту входного импульсного сигнала устанавливаются в единичное состояние, и на J-входы JK-триггеров 5 и 6. Кроме того, с инверсного выхода Д-триггера 2 сигнал подается на К-входы JK-триггеров 5 и 6, то есть имеем на входах JK-триггеров 5 и 6 комбинации сигналов: J=0; K=1.

Входные сигналы Uвх1 и Uвх2 еще поступают на С-входы первого и второго JK-триггеров 5 и 6 соответственно, которые при указанной комбинации сигналов по спаду входных импульсов устанавливаются в единичное состояние [4]. Д-триггеры 2, 3, 4 и JK-триггеры 5, 6 после переключения становятся нечувствительными к последующим импульсам, а также и к входным помехам до подачи сигнала сброса на их R-входы. Благодаря этому повышается помехозащищенность фазового компаратора.

Выходной сигнал JK-триггера 5 подается одновременно на первый вход элемента И 7 и на R-вход Д-триггера 3, который устанавливается в состояние логического нуля. Выходной сигнал Д-триггера 4 поступает одновременно на второй вход элемента И 7 и на R-вход Д-триггера 4, который устанавливается в состояние логического нуля. Выходной сигнал элемента И 7 перебрасывает Д-триггер 2 и JK-триггеры 5, 6 в состояние логического нуля, то есть в исходное состояние. Выходные импульсы Д-триггеров 3 и 4 подаются соответственно на первый и второй входы интегратора 8, на выходе которого снимается однозначная информация о фазовом соотношении сигналов Uвх1 и Uвх2.

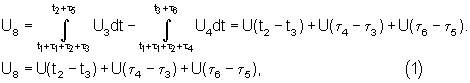

Поэтому имеем

где: t1 - момент перехода сигнала меньшей фазы через нуль с низкого уровня на высокий уровень; t2 - момент перехода через нуль сигнала меньшей фазы с высокого уровня на низкий уровень; t3 - момент перехода через нуль сигнала большей фазы с высокого уровня на низкий уровень; τ1, τ2, τ3, τ4, τ5, τ6 - постоянные времени соответствующих блоков по описанию изобретения.

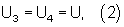

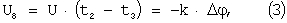

Постоянные времени (время задержки включения) Д-триггеров τ3 и τ4 и JK-триггеров τ5 и τ6 по величине теоретически равны между собой. Поэтому разностью (τ4-τ3) и (τ6-τ5) можно пренебречь. Тогда выражение (1) запишем в следующем виде:

где: U - напряжение, соответствующее уровню логической единицы; k - коэффициент передачи фазового компаратора; t2<t3.

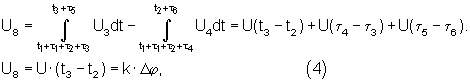

На фиг.2б приведена временная диаграмма, поясняющая работу фазового компаратора для второго случая, когда Δϕ>0.

На первый и второй входы элемента ИЛИ 1 поступают входные импульсные сигналы Uвх1 и Uвх2 соответственно. На выходе элемента ИЛИ 1 формируются импульсы, полученные логическим сложением. Выходной сигнал элемента ИЛИ 1 подается на С-вход первого Д-триггера 2, который по переднему фронту первого импульса устанавливается в единичное состояние. Прямой выходной сигнал Д-триггера 2 поступает одновременно на С-входы второго и третьего Д-триггеров 3 и 4, которые устанавливаются в единичное состояние, и на J-входы JK-триггеров 5, 6. Инверсный выходной сигнал Д-триггера 2 подается одновременно на К-входы JK-триггеров 5, 6. Таким образом, на входах JK-триггеров 5 и 6 образуется комбинация сигналов: J=0; K=1.

Входные сигналы Uвх1 и Uвх2 еще поступают на С-входы первого и второго JK-триггеров 5 и 6 соответственно, которые по спаду этих импульсов при комбинации сигналов на входах J=0; K=1 устанавливаются в единичное состояние. Выходной сигнал JK-триггера 5 подается одновременно на первый вход элемента И 7 и на R-вход Д-триггера 3, который переключается в состояние логического нуля. Выходной сигнал JK-триггера 6 поступает одновременно на второй вход элемента И 7 и на R-вход Д-триггера 4, который устанавливается в состояние логического нуля. Выходные импульсы элемента И 7 перебрасывают Д-триггер 2 и JK-триггеры 5, 6 в состояние логического нуля, то есть в исходное состояние. Выходные импульсы Д-триггеров 3 и 4 подаются соответственно на первый и второй входы интегратора 8, на выходе которого снимается однозначная информация о фазовом соотношении входных сигналов Uвх1 и Uвх2.

t3<t2.

Описание работы фазового компаратора, когда фазы первого и второго входных сигналов равны, не приводится ввиду идентичности с описанием для первого и второго случаев.

Введение новой совокупности признаков позволяет повысить помехозащищенность и точность работы фазового компаратора. Повышение помехозащищенности было обосновано выше по ходу описания работы устройства.

Повышение точности работы фазового компаратора достигается тем, что исключено влияние неидентичности формы входных сигналов Uвх1 и Uвх2 на точность работы. Для этого в схеме производится двойное улучшение формы входных сигналов, используя три перехода через нуль. Для первого улучшения входные сигналы Uвх1 и Uвх2 проходят через логический элемент ИЛИ 1 и первый Д-триггер 2, то есть оба сигнала подвергаются идентичному преобразованию. Далее выходной сигнал первого Д-триггера 2 одновременно переключает Д-триггеры 3 и 4, которые формируют передние фронты интегрируемых сигналов U3 и U4. Второе улучшение состоит в том, что для формирования задних фронтов сигналов U3 и U4 используются не критичные к фронтам входных сигналов JK-триггеры 5 и 6, на С-входы которых поступают сравниваемые сигналы Uвх1 и Uвх2. Кроме того, точность работы фазового компаратора достигается за счет исключения температурной погрешности, так как температурные погрешности сигналов U3 и U4 взаимно компенсируют друг друга в интеграторе.

Источники информации

1. Авторское свидетельство СССР №525226, кл. Н 03 d 13/00.

2. Авторское свидетельство СССР №849418, кл. Н 03 d 13/00.

3. Патент на изобретение РФ №2240646, кл. Н 03 D 13/00 (прототип).

4. Гольденберг А.М. Импульсные устройства. М.: Радио и связь, 1981.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЧАСТОТНО-ФАЗОВЫЙ ДЕТЕКТОР | 2006 |

|

RU2300170C1 |

| ФАЗОВЫЙ КОМПАРАТОР | 2003 |

|

RU2240646C1 |

| ДИФФЕРЕНЦИРУЮЩЕЕ УСТРОЙСТВО | 2002 |

|

RU2222828C1 |

| Фазовый компаратор | 1982 |

|

SU1094141A2 |

| Частотный компаратор | 1978 |

|

SU830643A1 |

| ТЕЛЕВИЗИОННАЯ КАМЕРА ДЛЯ НАБЛЮДЕНИЯ В УСЛОВИЯХ СЛОЖНОГО ОСВЕЩЕНИЯ И/ИЛИ СЛОЖНОЙ ЯРКОСТИ ОБЪЕКТОВ | 2011 |

|

RU2472299C1 |

| Частотно-фазовый детектор | 1990 |

|

SU1775844A1 |

| Сравнивающее устройство | 1986 |

|

SU1370756A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ОТНОШЕНИЯ ДВУХ НАПРЯЖЕНИЙ | 1991 |

|

RU2019837C1 |

| Управляемый фазовращатель | 1980 |

|

SU995278A1 |

Изобретение относится к измерительной технике и может быть использовано в системах контроля и регулирования параметров промышленных установок. Достигаемый технический результат - повышение точности и надежности. Фазовый компаратор содержит три Д-триггера, логический элемент ИЛИ, два JK-триггера, логический элемент И и интегратор. 2 ил.

Фазовый компаратор, содержащий два Д-триггера и интегратор, выход которого является выходом фазового компаратора, отличающийся тем, что в него введены логический элемент ИЛИ, выход которого подсоединен к С-входу первого Д-триггера, два JK-триггера, третий Д-триггер и логический элемент И, причем первый и второй входы логического элемента ИЛИ являются первым и вторым входами фазового компаратора и подключены соответственно к С-входам первого и второго JK-триггеров, Д-входы первого, второго и третьего Д-триггеров подсоединены к источнику сигнала логической единицы, выход логического элемента И подключен одновременно к R-входам первого и второго JK-триггеров и первого Д-триггера, прямой выход которого подсоединен одновременно к С-входам второго и третьего Д-триггеров и к J-входам первого и второго JK-триггеров, К-входы которых подключены к инверсному выходу первого Д-триггера, прямой выход первого JK-триггера подсоединен одновременно к R-входу второго Д-триггера и к первому входу логического элемента И, прямой выход второго JK-триггера подключен к R-входу третьего Д-триггера и к второму входу логического элемента И, прямые выходы второго и третьего Д-триггеров подсоединены соответственно к первому и второму входам интегратора.

| ФАЗОВЫЙ КОМПАРАТОР | 2003 |

|

RU2240646C1 |

| ИМПУЛЬСНЫЙ ЧАСТОТНО-ФАЗОВЫЙ ДЕТЕКТОР | 1991 |

|

RU2012992C1 |

| Дорожная спиртовая кухня | 1918 |

|

SU98A1 |

| СТЕКАТЕЛЬ НЕПРЕРЫВНОГО ДЕЙСТВИЯ ДЛЯ ОТДЕЛЕНИЯ | 0 |

|

SU283160A1 |

| Мембранная муфта | 1973 |

|

SU475468A1 |

Авторы

Даты

2006-08-27—Публикация

2005-04-27—Подача