1

Изоб:ретение относится к вычислительной технике и может быть ианользовано в устройст1вах, в которых осуществляется преобразование аналого:вых сигналов В цифровую форму.

Известно устройство для лреобразования аналог-код с цифровой автокоррекцией нуля, содержащее входной коммутатор, схему сравнения, нервый вход которой нодключен к источнику -преобразуемого напряжения, а второй к выходу декодирующего преобразователя, входы которого через блок вентилей подключены ко входам первого регистра.

Выход первого регистра соединен с нервым входом сум1матора, второй вход которого соединен с выходом второго регистра, а выход соединен со входом второго регистра, управляющие входы iBTOporo регистра подключены к выходам блока формирования кода, первый вход которого соединен с третьим выходом блока нрограммы н синхронизации, первый вход которого соединен с управляющнми входами блока вентилей и первого регистра.

Однако известный нреобразователь имеет недостаточную точность, обусловленную применением одной .схемы сравнения и входного коммутатора в условиях повышеиных температурных полей.

Целью изобретения является повышение точности преобразователя.

2

Для этого в преобразователь введены дополнительная схема сравнения, второй вход которой нодключен к источнику преобразуемого напряжения, а первый - к декодирующему преобразователю, схема «ИЛИ, первый вход которой соединен с выходом схемы сравнения, а второй - с выходом дополнительной схемы сравнения, а выход соединен со вторым входом блока формирования кода, блок элементов коММутации, входы которого соединены с выходами второго регистра, управляющий вход соединен со вторым выходам блока (нрограММы и синхронизации, а выходы подключены «о входам декодирующего преобразователя, и делитель выходного кода, вход которого подключен к сумматору.

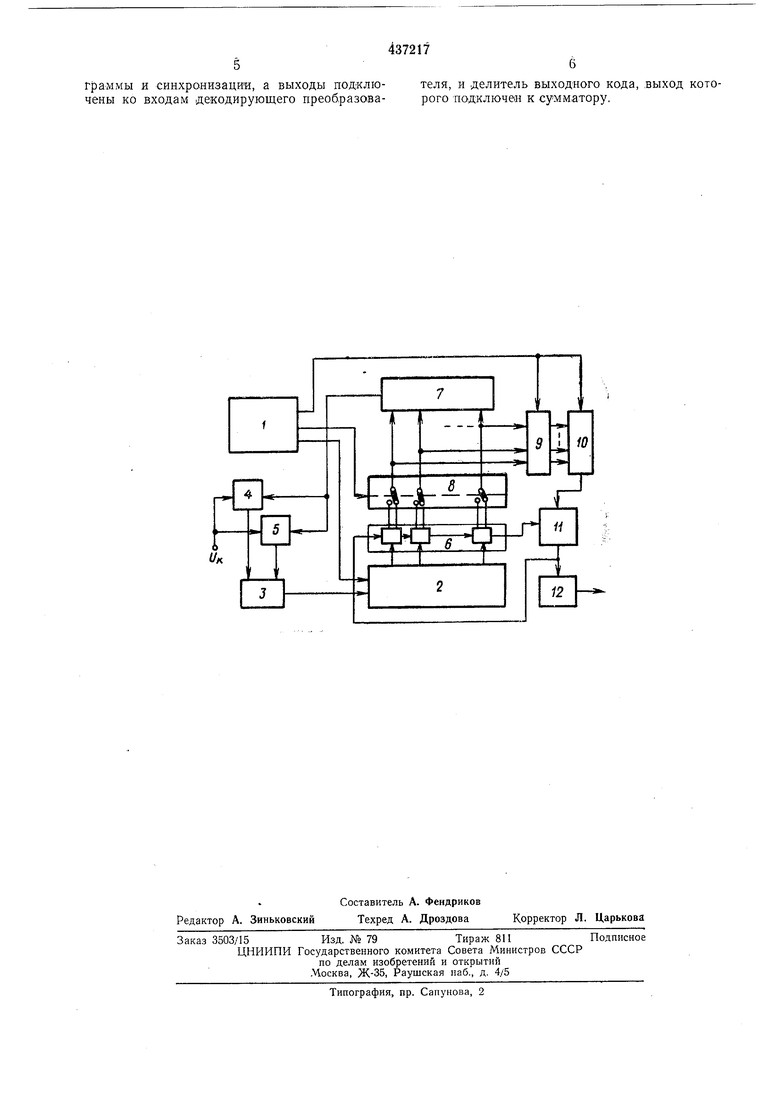

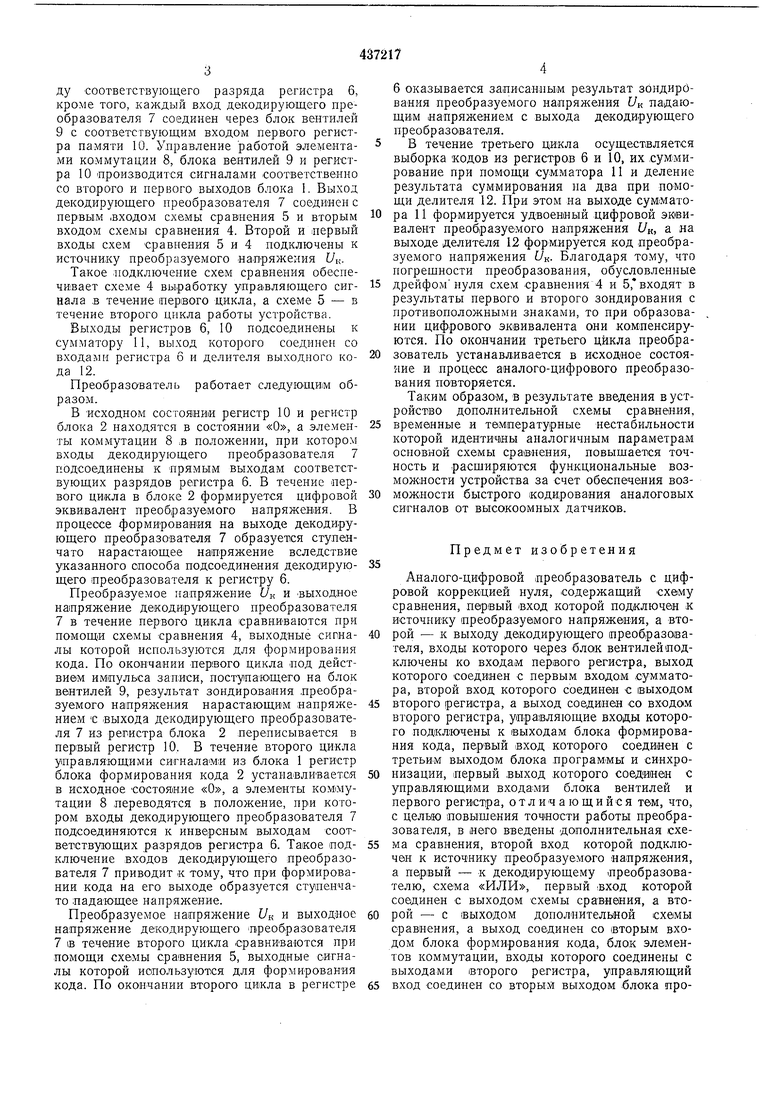

На чертеже приведена функциональная блок-схема преобразователя.

Аналого-цифровой преобразователь с цифровой коррекцией нуля содержит блок программы и синхронизации 1, блок формирования кода 2, на первый вход которого поступают сигналы управления от блока 1, а на второй - через схему «ИЛИ 3 сигналы с выходов основной и дополнительной схем сравнений 4, 5. Выходы блока формирования кода 2 присоединены ко второму регистру 6. Декодирующий преобразователь 7 каждым своим входом подсоединен через элемент коммутации 8 к прямому либо инверсному выходу соответствующего разряда регистра 6, кроме того, каждый вход декодирующего преобразователя 7 соединен через блок вентилей 9 с соответствующим входом первого регистра памяти 10. Управление работой элементами коммутации 8, блока вентилей 9 и регистра 10 производится сигналами соответственно со второго и первого выходов блока 1. Выход декодирующего преобразователя 7 соединен с первым .входом схемы сравнения 5 и вторым входом схемы сравнения 4. Второй и первый входы схем сравнения 5 и 4 подключены к источнику преобразуемого напряжения UK. Такое подключение схем сравнения обеспечивает схеме 4 выработку управляющего сигнала в течение первого цикла, а схеме 5 - в течение второго цикла работы устройства. Выходы регистров 6, 10 подсоединены к сумматору 11, выход которого соединен со входами регистра 6 и делителя выходного кода 12. Преобразователь работает следующим образом. В ИСХОДНОМ состоянии регистр 10 и регистр блока 2 находятся в состоянии «О, а элементы коммутации 8 в положении, при котором входы декодирующего преобразователя 7 подсоединены к прямым выходам соответствующих разрядов регистра 6. В течение первого цикла в блоке 2 формируется цифровой эквивалент преобразуемого напряжения. В процессе формирования на выходе декодирующего преобразователя 7 образуется ступенчато нарастающее напряжение вследствие указанного способа подсоединения декодирующего преобразователя к регистру 6. Преобразуемое напряжение UK и выходное напряжение декодирующего преобразователя 7 в течение первого цикла сравниваются при помощи схемы сравнения 4, выходные сигналы которой используются для формирования кода. По окончании первого цикла под действием импульса записи, поступающего на блок вентилей 9, результат зондирования преобразуемого напряжения нарастающим напряжением С -выхода декодирующего преобразователя 7 из регистра блока 2 переписывается в первый регистр 10. В течение второго цикла управляющими сигналами из блока 1 регистр блока формирования кода 2 устанавливается в исходное состояние «О, а элементы ком мутации 8 переводятся в положение, при котором входы декодирующего преобразователя 7 подсоединяются к инверсным выходам соответствующих разрядов регистра 6. Такое подключение входов декодирующего преобразователя 7 приводит к тому, что при формировании кода на его выходе образуется ступенчато падающее напрял ение. Преобразуемое напряжение UK и выходное напряжение декодирующего П1реобразователя 7 1В течение второго цикла сравниваются при помощи схемы сравнения 5, выходные сигналы которой используются для формирования кода. По окончании второго цикла в регистре 6 оказывается записанным результат зондирования преобразуемого напряжения UK падающим напряжением с выхода декодирующего преобразователя. В течение третьего цикла осуществляется выборка кодов из регистров 6 и 10, их .сум мирование при помощи сумматора И и деление результата суммироваиин па два при помощи делителя 12. При этом на выходе сумматоpall формируется удвоенный цифровой эквивалент преобразуемого напряжения UK, а на выходе делителя 12 формируется код преобразуемого напряжения UK- Благодаря тому, что погрещности преобразования, обусловленные дрейфомнуля схем сравнения 4 и 5,входят в результаты первого и второго зондирования с противоположными знаками, то при образовании цифрового эквивалента они компенсируются. По окончании третьего цикла преобразователь устанавливается в исходное состояние и нроцеос аналого-цифрового преобразования повторяется. Таким образом, в результате введения в устройство дополнительной схемы сравнения, временные и температурные нестабильности которой идентичны аналогичным параметрам основной схемы сравнения, повышается точность и расщиряются функциональные возможности устройства за счет обеспечения возможности быстрого кодирования аналоговых сигналов от высокоомных датчиков. Предмет изобретения Аналого-цифровой преобразователь с цифровой коррекцией нуля, содержащий схему сравнения, первый вход которой подключен к источнику преобразуемого напряжения, а второй - к выходу декодирующего преобразователя, входы которого через блок вентилей подключены ко входам первого регистра, выход которого соединен с первым входом сумматора, второй вход которого соединен с выходом второго регистра, а выход соединен со входам второго регистра, управляющие входы которого подключены к выходам блока фор1мирования кода, первый вход которого соединен с третьим выходом блока программы и синхронизации, первый выход которого соединен с унравляющими входа.ми блока вентилей и первого регистра, отличающийся тем, что, с целью повышения точности работы преобразователя, в него введены дополнительная схема сравнения, второй вход которой подключен к источнику преобразуемого напряжения, а первый - к декодирующему преобразователю, схема «ИЛИ, первый вход которой соединен с выходом схемы сравнения, а второй - с выходом дополнительной схемы сравнения, а выход соединен со вторым входом блока формирования кода, блок элементов коммутации, входы которого соединены с выходами второго регистра, управляющий вход соединен со вторым выходом блока программы и синхроиизации, а выходы подключены ко входам декодирующего преобразователя, и делитель выходного кода, выход которого подключен к cyMMiHTOpy.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой прибор для тензометрических весов | 1980 |

|

SU934233A1 |

| Устройство для измерения и контроля параметров аналого-цифровых преобразователей | 1981 |

|

SU1005297A1 |

| ПРЕОБРАЗОВАТЕЛЬ АНАЛОГОВЫХ ВЕЛИЧИ В ЦИФРОВОЙ КОД | 1971 |

|

SU318963A1 |

| Аналого-цифровой преобразователь | 1972 |

|

SU477538A1 |

| Преобразователь напряжения в код | 1977 |

|

SU728222A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

| Аналого-цифровой преобразователь | 1976 |

|

SU563713A1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1730722A2 |

| Аналого-цифровой преобразователь с плавающей запятой | 1975 |

|

SU750725A1 |

| МНОГОКАНАЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1973 |

|

SU400021A1 |

Авторы

Даты

1974-07-25—Публикация

1972-04-19—Подача