Изобретение относится к радиотехнике и может быть использовано для регистрации и анализа ошибок при приеме дискретных сигналов по высокоскоростным каналам связи.

Известны устройства для регистрации ошибок, содержащие блок фазирования и выделения ошибок, к выходу которого подключен распределитель, соединенный с разрядами анализатора смежных ошибок, и счетчики, подключенные к выходам этих разрядов. Однако известные устройства характеризуются ограниченным быстродействием.

Цель изобретения - повысить быстродействие устройства.

Для этого вводят высокочастотные элементы обработки дискретных сигналов, которые позволяют повысить быстродействие устройства для использования его в наносекундном диапазоне.

В предлагаемом устройстве распределитель содержит последовательно включенную цепочку каскадов запрета, подключенную к выходу каскада «ИЛИ блока фазирования и выделения ошибок и к входу первого разряда анализатора смежных ошибок. Выходы каскадов запрета поочередно соединены с входами остальных разрядов анализатора смежных ошибок, причем первый разряд состоит из линии задержки на один тактовый интервал и каскада запрета, запрещающий

вход которого подключен к выходу каскада «ИЛИ через линию задерж;ки. Второй вход каскада запрета первого разряда непосредственно подключен к выходу каскада «ИЛИ.

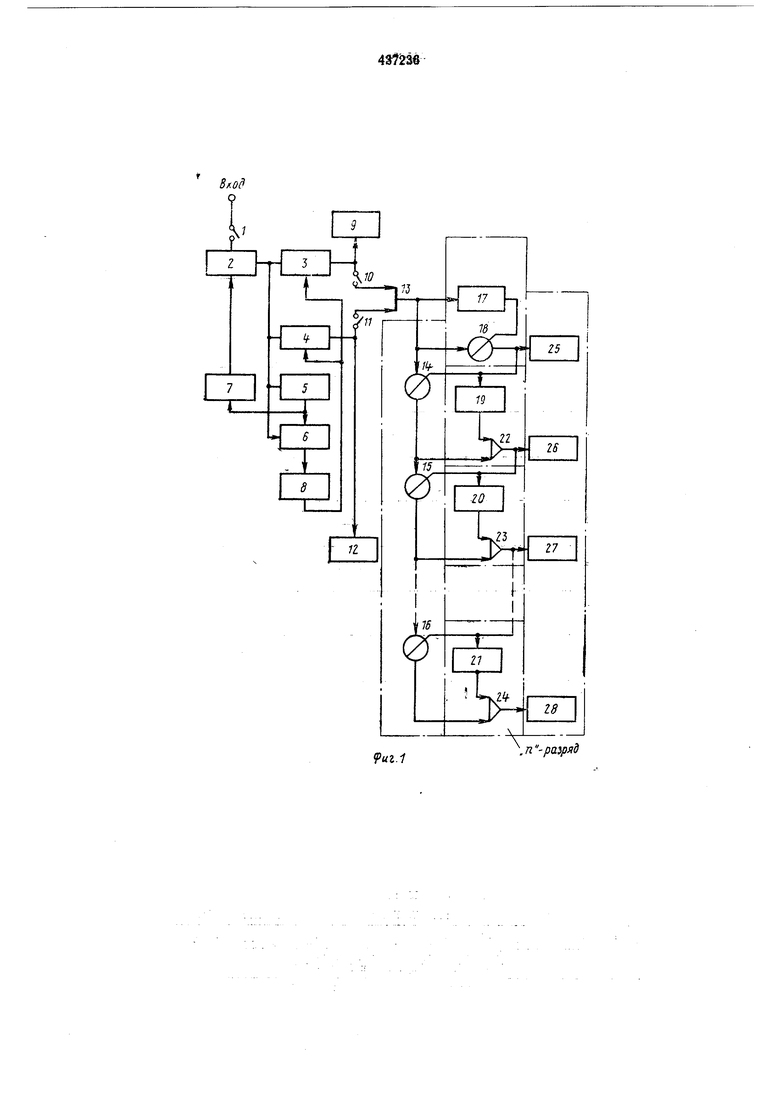

Выход каскада запрета первого разряда соединен с запрещающим входом каскада запрета распределителя, с входом линии задержки второго разряда анализатора и с входом счетчика. Каждый из остальных разрядов а-нализатора смежных ошибок состоит из лийии задержки на один тактовый интервал и каскада совпадения, один вход которого подключен через линию задержки к выходу предыдущего разряда, а другой соединен с выходом каскада запрета распределителя. Выход каскада совпадения подключен также к запрещающему входу следующего каскада запрета и к входу счетчика. Иа фиг. 1 приведена функциональная схема

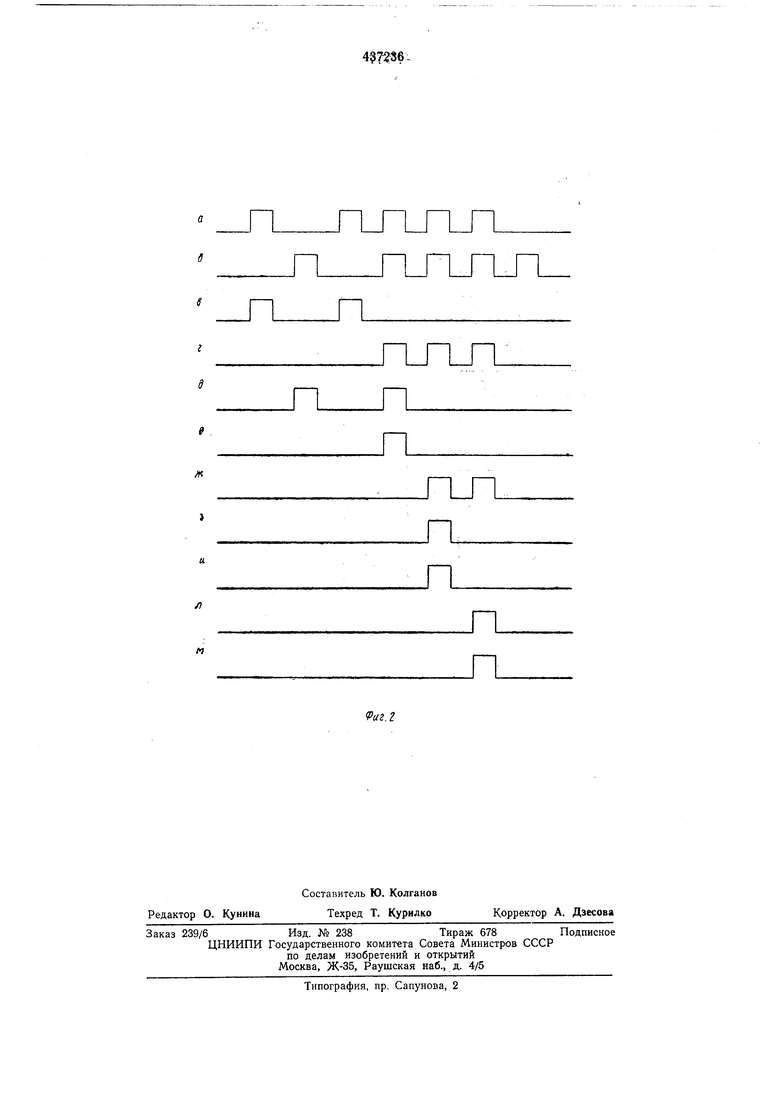

устройства; на фиг. 2 - временные диаграммы напряжений в отдельных точках схемы.

Устройство содержит блок фазирования и выделения ошибок, распределитель, анализатор смежных ошибок и счетчики. В состав

блока фазирования и выделения ошибок входят: тумблер 1 включения света, блок 2 авгь матической остановки счета, блок выделения ошибок типа () 3, блок выделения ошибок типа () 4, блок разрядной синхронизации

5, блок цикловой синхронизации 6, счетчик

тактовых импульсов 7, блок контрольных сигналов 8, счетчик ошибок типа () 9, тумблеры 10 и 11, обеспечивающие возможность исключить из анализа смежных ошибок ошибки типов () или (0-)-1), счетчик ошибок типа () 12, каскад «ИЛИ 13.

Распределитель состоит из цепочки каскадов запрета 14, 15, 16.

Анализатор смежных ошибок содержит п разрядов (на фиг. 1 показаны 1-ый, 2-ой, 3-ий и п-ый разряды), причем 1-й разряд состоит из линии задержки на один тактовый интервал 17 и каскада запрета 18, а каждый из остальных разрядов - из аналогичной линии задержки 19, 20, 21 и каскада совпадения 22, 23, 24.

Число счетчиков смежных ошибок 25-28 равно числу разрядов анализатора.

Устройство работает следуюшим образом.

Испытательные сигналы из линии поступают в блоки выделения ошибок 3 и 4 и поэлементно сравниваются с контрольными кодовыми комбинациями, формируемыми в блоке контрольных сигналов 8. Выделенные импульсы ошибок объединяются в общий поток в каскаде «ИЛИ 13.

На диаграмме «а (см. фиг. 2) показана последовательность импульсов ошибок на выходе каскада «ИЛИ 13, состоящая в данном примере из одиночной ошибки и смежной ошибки длиной , разделенных безошибочным интервалом в один такт. Импульсы ошибок поступают на оба входа каскада запрета 18, причем на запрещающий вход они приходят задержанными на один тактовый интервал (фиг. 2, б). На выход каскада запрета 18 и в счетчик первого разряда 25 пропускаются только одиночные ошибки и первые импульсы смежных ошибок (фиг. 2, в). На запрещающий вход каскада запрета 14 распределителя поступают импульсы с выхода первого разряда анализатора смежных ошибок, поэтому на ВХОД второго разряда анализатора не пропускаются одиночные ощибки, а длина смелшых ошибок уменьшается на одип тактовый интервал. С выхода каскада запрета 14 импульсы ошибок (фиг. 2, г) подаются на вход следующего каскада запрета 19 распределителя и на вход каскада совпадения 22, к второму входу которого подводятся импульсы одиночных ошибок и первые импульсы смежных ошибок, задержанные на одип тактовый интервал в линии задержки 19 (фиг. 2, д). Поэтому на вход счетчика второго

437236

разряда 26 пропускаются только вторичные импульсы смежных ошибок, в тех случаях, когда они существуют (фиг. 2, е). В остальных разрядах процессы аналогичны процессам: во втором разряде. Счетчик третьего разряда 27 служит для регистрации третьих импульсов смежных ошибок и так далее.

Таким образом, в предлагаемом устройстве происходит последовательное опробование

К- импульсов смежных ошибок (К-1)-ми импульсами, задержанными «а один тактовый интервал. В счетчике /С-го разряда регистрируются смежные ошибки длиной . Результаты, зафиксированные в счетчиках разрядов, представляют собой статистический ряд накопленных частот распределения длины смежных ошибок.

Предмет изобретения

Устройство для регистрации ошибок при приеме дискретных сигналов по высокоскоростным каналам связи, содержащее блок фазирования и выделения ошибок, к выходу которого подключен распределитель, соединенный с разрядами анализатора, и счетчики, подключенные к выходам этих разрядов, отличающееся тем, что, с целью повышения быстродействия, распределитель содержит последовательно включенную цепочку каскадов запрета, подключенную к выходу каскада «ИЛИ блока фазирования и выделения ошибок и к входу первого разряда анализатора, а выходы каскадов запрета поочередно соединены с входами остальных разрядов анализатора, причем первый разряд состоит из линии задержки на один тактовый интервал и каскада запрета, запрещающий вход которого подключен к выходу каскада «ИЛИ через линию задержки, второй непосредственно подключен к выходу каскада «ИЛИ, выход каскада запрета соединен с запрещающим входом каскада запрета распределителя, с входом линии задержки второго разряда анализатора и с входом счетчика, а каждый из остальных разрядов анализатора состоит из линии задержки на один тактовый интервал и каскада совпадения, один вход которого подключен через линию задержки к выходу предыдущего разряда, а другой соединен с выходом каскада запрета распределителя, причем выход каскада совпадения подключен также к запрещающему входу следующего каскада запрета и к входу счетчика.

, п -разряд

9иг.1

Авторы

Даты

1974-07-25—Публикация

1972-04-07—Подача