1

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных устройствах.

Известно устройство контроля последовательности импульсов, содержащее две схемы «ИЛИ, ВЫХОД одной из которых подключен к счетному входу триггера, а выход триггера соединен с одним из входов двухвходовой схемы «И, и элемент задержки импульсов и характеризующееся СЛОЖНОЙ конструкцией и низкой надежностью.

Цель изобретения - упрощение устройства контроля последовательности импульсов и повыщение его надежности.

Для этого ВЫХОД второй схемы «ИЛИ соединен непосредственно с другим входом двухвходовой схемы «И и через элемент задерл ки импульсов -с нулевым входом триггера.

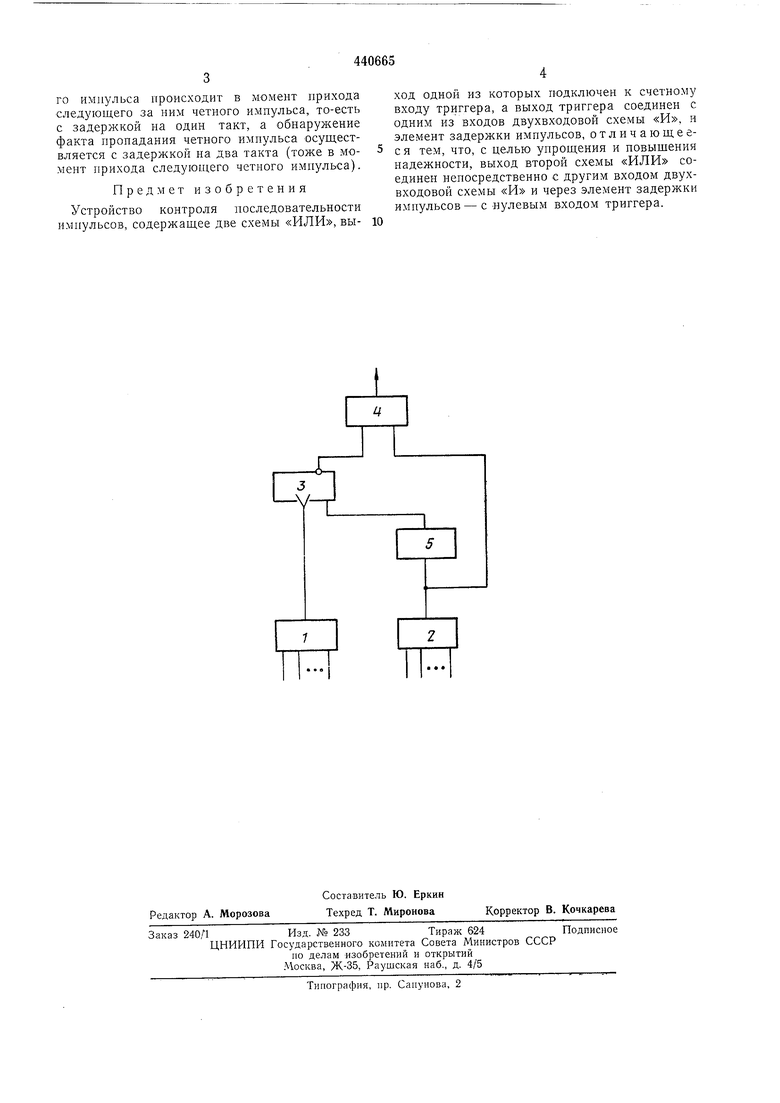

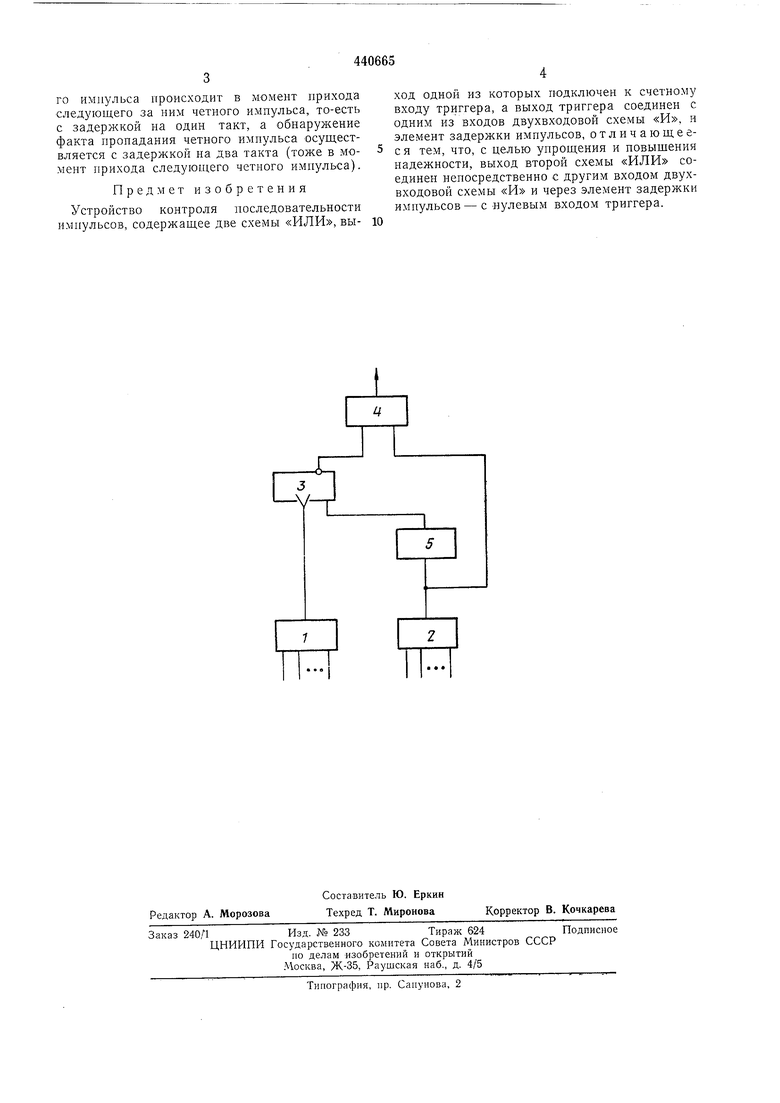

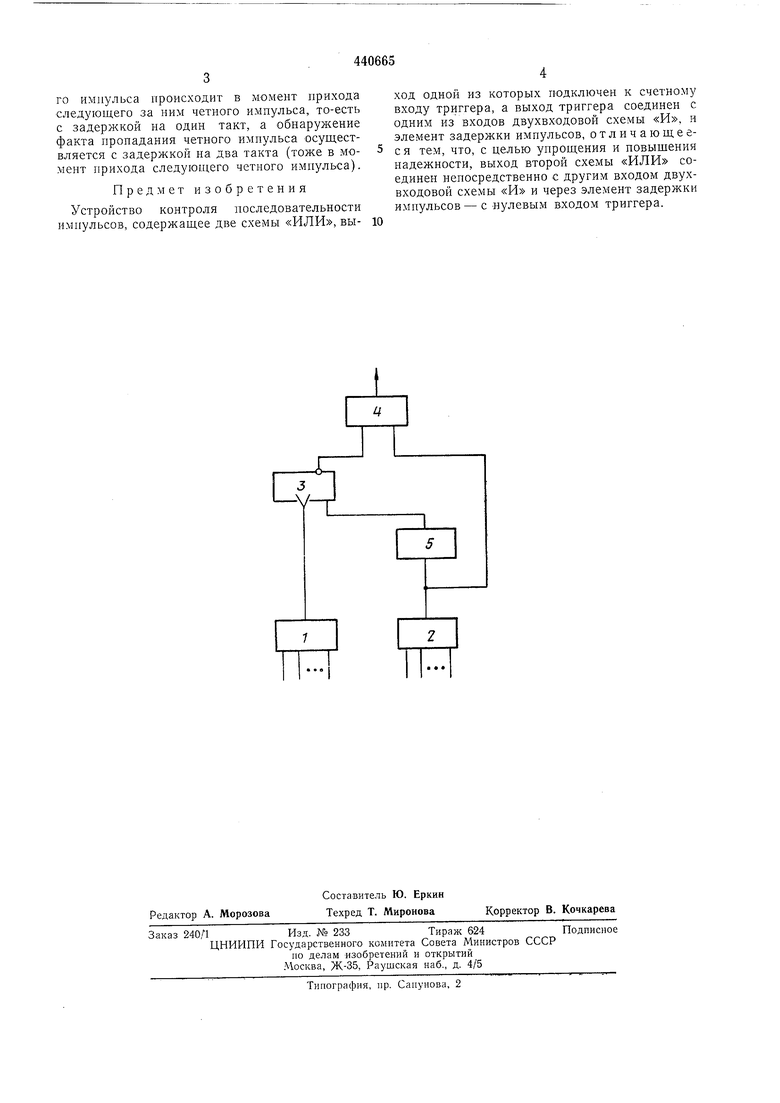

На чертеже приведена блок-схема предлагаемого устройства.

Устройство содержит схемы «ИЛИ I и 2. Выход схемы «ИЛИ 1 соединен со счетным ВХОДОМ триггера 3, выход которого подключен к одному из ВХОДОВ двухвходовой схемы «И 4.

Выход схемы «ИЛИ 2, соединен непосредственно со вторым ВХОДОМ схемы «И 4 и через элемент 5 задержки с нзлевым входом триггера 3.

Устройство работает следующим образом.

На выходесхемы «ИЛИ формируется

сигнал сборки нечетных контролируемых импульсов - С„, а на выходе схемы «ИЛИ 2,- сигнал сборки четных контролируемых импульсов - Са.

Сигнал Сн с выхода схемы «ИЛИ 1 поступает на счетный вход триггера 3, а сигнал С-2. с выхода схемы «ИЛИ 2 поступает на один из ВХОДОВ схемы «И и через элемент 5 задержки- на нулевой вход триггера 3. Потенциал с инверсного выхода триггера 3 нодается на другой ВХОД схемы «И 4.

При нормальном чередовании контролируемых импульсов сигнал С„ с выхода схемы «ИЛИ 1 устанавливает триггер 3 в единичное состояние, а задержанный сигнал Сд перебрасывает его В нулевое состояние.

Величина задержки элемента 5 определяется с таким расчетом, чтобы при правильной работе контролируемого устройства БЫПOv ияЛОСЬ условие:

,,,о,

где GZZ - задержанный сигнал Сг, Т - потенциал инверсного выхода триггера 3.

При выпадании какого-либо импульса из контролируемой последовательности происходит нарушение в чередовании имиульсов на счетном и нулевом входах триггера 3 и схема «И 4 вырабатывает сигнал ощибки. При

этом обнаружение факга пропада)П1я нечетного импульса происходит в момент прихода следующего за ним четного импульса, то-есть с задержкой на один такт, а обнаружение факта пропадания четного импульса осуществляется с задержкой на два такта (тоже в момент прихода следующего четного импульса).

Предмет изобретения

Устройство контроля последовательности импульсов, содержащее две схемы «ИЛИ, выход одной из которых подключен к счетному входу триггера, а выход триггера соединен с одним из входов двухвходовой схемы «И, и элемент задержки импульсов, отличающееся тем, что, с целью унрощения и повыщения надежности, выход второй схемы «ИЛИ соединен непосредственно с другим входом двухвходовой схемы «И и через элемент задержки импульсов - сНулевым входом триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВСЕСОЮЗНАЯ Iи1НТНО-ГЕ1йГ]Н;^?ДШE'-'!SJU^O':"tKA ^ | 1972 |

|

SU337782A1 |

| Устройство для управления реконфигурацией резервированной вычислительной системы | 1991 |

|

SU1837296A1 |

| Устройство для контроля последовательности импульсов | 1981 |

|

SU972513A2 |

| Устройство для контроля счетчика | 1980 |

|

SU884148A1 |

| Устройство для контроля работы @ -разрядного счетчика | 1982 |

|

SU1167727A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1978 |

|

SU746530A2 |

| Устройство для контроля -разрядного счетчика | 1977 |

|

SU664298A1 |

| Устройство для контроля последовательности чередования импульсов | 1986 |

|

SU1406757A1 |

| Устройство контроля временных интер-ВАлОВ КОдиРОВАННыХ пОСылОК | 1979 |

|

SU843211A2 |

| Устройство для контроля двухтактного двоичного счетчика | 1975 |

|

SU607221A1 |

Авторы

Даты

1974-08-25—Публикация

1972-06-01—Подача