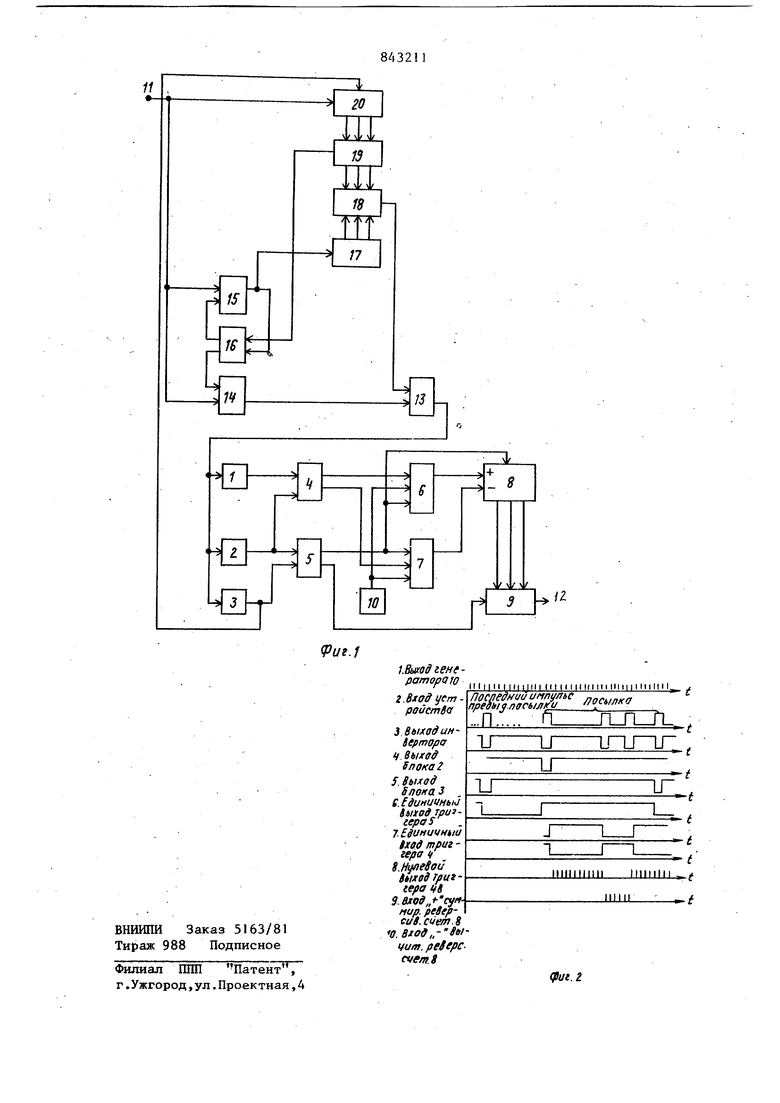

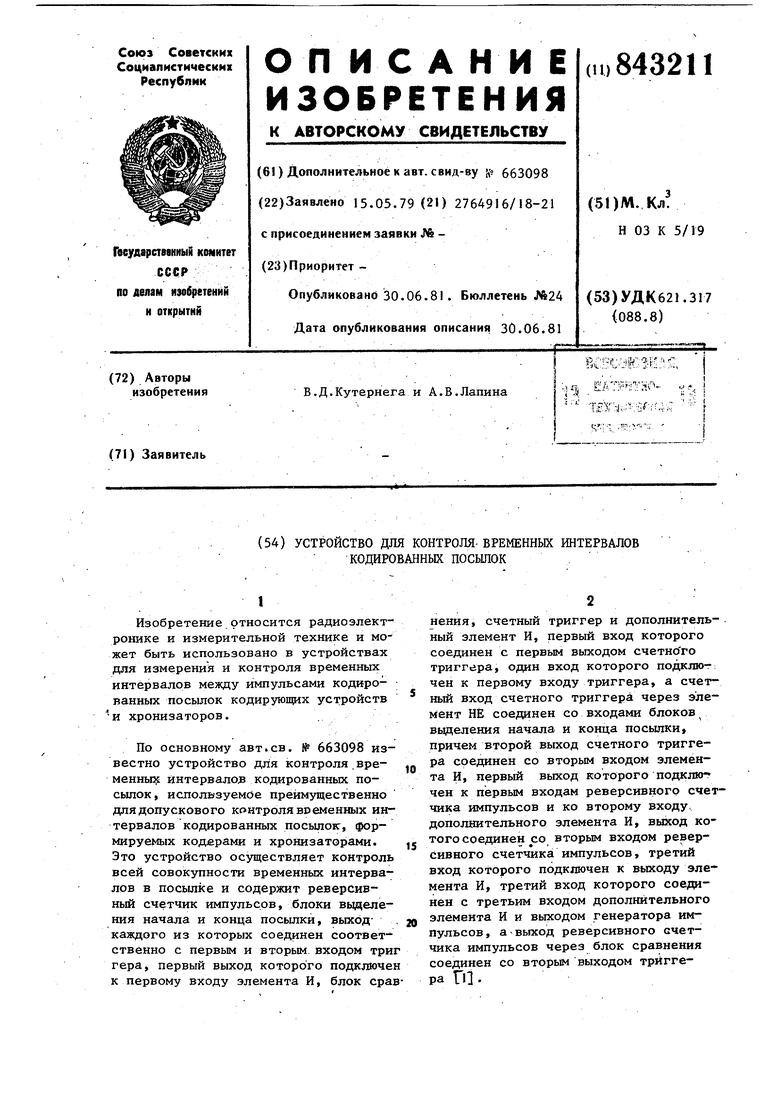

(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ-ВРЕМЕННЫХ ИНТЕРВАЛОВ КОДИРОВАННЫХ ПОСЫПОК , 3 Недостаток этого устройства заключается в том, что оно не позволяет осуществлять контроль с высокой точностью, кроме того, недостаточно надежно. Цель изобретения - повышение точности. Поставленная цель достигается тем что в устройство д-пя контроля,, содер жащее блоки выделения начала и конца посьшки, выход последнего из которых .соединен с одним входом триг.гера, другой вход которого соединен с выходом блока начала посылки и одн из входов второго триггера, второй вход которого подключен к.выходу эле мента НЕ, первый выход первого триггера подключен к управляющему входу блока сравнения, информационные входы которого соединены с выходами реверсивного счетчика, второй выход первого триггера подключен к первым входам элементов И и управляющему входу реверсивного счетчика, суммиру ющий и вычитающий входы которого под ключены соответственно к выходам пер вого h второго элементов И, вторые входы которых соединены с выходом генератора импульсов, первый и второ выходы второго триггера соединены с третьими входами первого и второго элементов И соответственно, введены счетчик, программируемый дешифратор коммутатор, линия задержки, два элемента И, элемент ИЛИ.и управляющий триггер, причем выходы счетчика через программируемый дешифратор подключены к первой группе входов коммутатора, вторая группа входов которого соединена с отводами линии . задержки, выход коммутатора подключен к первому входу элемента ИЛИ, выход которого соединен со входами элемента НЕ и блоков выделения начала и конца кодированной посылки, выход последнего соединен с установочным входом счетчика, счетный вход ко торого подключен к входной шине устройства и первым входам первого и второго элементов И, вторые входы которых соединены с первым и вторым выходами управляющего триггера соответственно, единичный вход которого подключен к дополнительному выходу дешифратора, выход первЬго элемента И соединен с нулевым входом триггер /правления и входом линии задержки. 14 выход второго элемента И подключен ко второму входу элемента ИЛИ. На фиг.1 представлена блок-схема устройства; на фиг.2 -.временные диаграммы его работы. Устройство для контроля временных интервалов кодированной посылки содержит элемент НЕ 1, блок 2 выделения начала посылки, блок 3 вьщеления конца посьшки, счетный триггер 4, триггер 5, элементы И 6 и 7, реверсивный счетчик 8, блок 9 сравнения (с узлом памяти), генератор 10 импульсов, входную шину II, выходную шину 12, элемент ИЛИ 13,элементы И 14 и 15, управляюшлй триггер 16, линию 17 задержки с коммутируемыми отводами, коммутатор 18, программируемый дешифратор 19 и счетчик 20. Входная шина 11 соединена со входами счетчика 20 элементов И 14 и 15, Установочный выход счетчика 20 соедий н с выходом блока 3 выделения конца посылки, а информапионные выходы его подключены к входам программируемого дешифратора 19, который может быть выполнен на основе многовходовых элементов И, выходы дешифратора подключены ко входам коммутатора 18. Коммутатор 18 может быть выполнен на двухвходовых элементах И. Дополнительный выход.программируемомо дешифратора, являющийся объедине нием выходов многовходовых элементов И подключен к одиночному входу триггера 16. Вторые входы коммутатора 18 присоединены к отводам линии 17 задержки, выход коммутатора 18, присоединен к первому входу элемента ИЛИ 13, второй вход .которого присоединен к выходу элемента И 14, второй вход которого присоединен к инверсному выходу триггера 16, единичный выход которого подключен ко второму входу элемента И 15. Выход элемента И 15 присоединен к входу линии 17 задержки и к нулевому входу управляющего триггера 16. Выход элемента ИЛИ 13 соединен со входами блоков 2 и 3 выделения начала и конца посьшки соответственно и через элемент НЕ 1 со входом счетного триггера 4. Выход блока 3 выделения конца посылки присоединен к нулевому входу триггера 5. Выход блока 2 выделения начала посылки соединен с единичным входом триггера 5 и с установочным входом счетного тпиггера 4. Один вы. 58432

ход счетного триггера 4 соединен с одним их выходов элемента И 6, а другой его выход соединен с одним из входов элемента И 7. Один выход триггера 5 соединен с одним из входов j элементов И 6 и 7 и входом реверсивного счетчика 8. Нулевой выход триггера 5 соединен со входом блока сравнения 9. Вторыевходы элементов И 6 и 7 присоединены к выходу генератора о 10. Выход элемента И 6 присоединен к входу суммирования, выход элемента И 7 к входу вычитания реверсивного счетчика 8. Информационные выходы счетчика 8 присоединены к входам бло- is ка сравнения 9.

Устройство работает следующим образом.

В исходное состояние узлы устройства устанавливаются импульсом с вы- 20 хода блока 3 выделения конца посылки, который подается на входы счетчика 20 и триггера 5, сигнал с его выхода устанавливает, запрещение по первым входам элементов И 6 и 7 и устанав- 25 ливает в исходное состояние реверсивный счетчик 8.

Состояние счетного триггера 4 во время отсутствия кодированной посылки не влияет на работу устройства, ЗО так как он устанавливается импульсом с выхода блока 2 в такое состояние (фиг.2), при котором на прямом выходе триггера 4 низкий потенциал, который устанавливает на входе эле- 35 мента И 6 запрещение.

Импульсы генератора 10 не проходят на выход элементов И 7 и 6, так как хотя бы на одном,из их входов имеется сигнал запрещения. .40

Предположим, что второй и седьмой временные интервалы посылки не кратны Периоду частоты генератора 10. В таком случае программируемый дешифратор 19 должен содержать, два много- 45 ходовых элемента И.

Шпульсы с выходов многовходовых элементов И программируемого дешиф атора 19 объединяются и устанавливают правляющий триггер 16 в такое сое - 50 тояние, при котором элемент И 15 ткрывается для импульса, определяюего второй интервал, а элемент И 14 акрывается для прохождения этого мпульса кодированной посылки. 55

Задним фронтом этого импульса с ыхода элемента Н 15 триггер 16 устаавливается в такое состояние, при

котором элемент И 15 закрыт, а элемент И 14 открыт и импульсы с выхода элемента И 14 поступают через элемент ИЛИ 13 на входы элемента НЕ 1 и блоков 2 и 3 выделения и конца посылки соответственно.

Импульсы с выхода элемента И 15 поступают на вход линии 17 задержки, .где задерживаются на величину, опредляемую выражением

Т|ин-г -гец- АЧ где Т- -7 временной интервал кодиVIHT

рованнои посылки;

Tpgj - период частоты генератора п - целое число периодов частоты генератора, укладывающихся в контролируемом интервале;

At - остаток Временного интервала менее , Коммутатор второго интервала открыт сигналами с выходов npo раммируемого дешифратора 19. Тогда задержанный импульс, определяющий второй временной интервал, становится задержанным на д t.j и с объединенного выхода- коммутатора 18 через элемент ИЛИ 13 поступает на входы элемента НЕ 1 и блоков 2 и 3 выделения начала и конца посылки.

Таким образом, импульсы, определяющие временные интервалы, которые кратны периоду частоты генер-атора поступают через элемент И 14 на входы упомянутых узлов устройства контроля незадержанными, а импульсы, Опрделяющие временные интервалы, которые не кратны периоду частоты генератора через элемент И 15 поступают на вход линии задержки.

Величина задержки каждого импульса устанавливается кратной Т посредством программируемого дешифратора 19 и коммутатора 18.

Распределение импульсов посылки на вход линии 17 задержки и без задержки на выход элемента И 14 осуществляет программируемый дешифратор 19 посредством триггера 16. .

Первый импульс кодированной посылки положительной полярност с выхода элемента ИЛИ I3 через элемент НЕ 1 поступает на счетный вход триггера 4. Импульс с выхода блока 2 воздейст1вует на вход триггера 5 с раздельным запуском.

84

Триррегы 4 и 5 устанавливаются передним фронтом первого импульса. На прямом выходе триггера 5 устанав ливается высокий потенциал, который является разрешающим для элементов И 6 и 7, и снимает запрещение с управляющего входа реверсивного счетчи ка 8.

Триггер 4 устанавливается передним фронтом первого импульса с выхода блока 2 в такое состояние, при котором на его прямом выходе устанавливается низкий потенциал - запрещение для элемента 6, которое снимается в момент поступления первого импульса посылки с выхода элемента НЕ 1 на счетный вход триггера 4.

Импульсы с выхода генератора 10 через открытый элемент И 6 поступают на вход суммирования реверсивного счетчика 8.

В момент поступления второго импульса посылки на счетный вход триггера 4, на одном выходе которого устанавливается низкий потенциал (запрещение для элемента 6), на другом его выходе - высокий потенциал (разрешение для элемента 7), импульсы с выхода генератора 10 поступают на вход вычитания реверсивного счетчика.

Таким образом, все импульсы определяющие нечетные временные интервалы кодированной посылки разрешают прохождение импульсов с выхода генератора 10 иа вход суммирования, а четные разрешают прохождение на вход вычитания реверсивного счетчика В. Импульс с выхода блока 3 устанавливает триггер 5 в такое состояние, при котором устанавливается запрещение на входах элементов 6 и 7 и разрешениь на дополнительном входе блока 9, который этого момента осуществляет сравнение числа (остатка) поперемениого сложения-вычитания импульсов

1В

с вькода генератора 10. При равенст-ве сравниваемых кодов блок 9 вырабатывает импульс на выходе 12. При превьппении разницы кодов допустимой величины блок 9 импульс не формирует. С приходом следующей посылки импульсов работа устройства повторяется.

Формула изобретения

Устройство для контроля временных интервалов кодированных посылок по авт.св. № 663098, отличающее с я тем, что, с целью повышения точности, в него введены счетчик, программируемый дешифратор, коммутатор, линия задержки, два элемента И, элемент ИЛИ и управляющий триггер, причем выходы счетчика через программируемый дешифратор подключены к пер вой группе входов коммутатора, вторая группа входов которого соединена с отводами линии задержки, выход коммутатора подключен к первому входу элемента ИЛИ, выход которого соединен со входами элемента НЕ и блоков вьщеления начала и конца посылки, выход последнего соединен с установоным входом счетчика, счетный вход которого подключен к входной шине устройства и первым входом первого и второго элементов И, вторые входы которых соединены с первым и вторым выходами управляющего триггера соответственно, единичный вход которого подключен к дополнительному выходу дешифратора, выход первого элемента И соединен с нулевым входом триггера управленияи входом линии задержки, выход второго элемента И подключеи ко второму входу элемента ИЛИ.

Источникиинформации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 663098, кл. И 03 К 5/18, 1977.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля временных интер-ВАлОВ КОдиРОВАННыХ пОСылОК | 1979 |

|

SU843210A2 |

| Устройство для контроля временных интервалов кодированных посылок | 1976 |

|

SU663095A1 |

| Селектор импульсов кодированной посылки | 1978 |

|

SU758507A1 |

| Шифратор-дешифратор | 1981 |

|

SU1005295A1 |

| Устройство определения временного положения импульсных сигналов | 1988 |

|

SU1596301A1 |

| Управляемая линия задержки | 1990 |

|

SU1725370A2 |

| Преобразователь интервалов времени в цифровой код | 1984 |

|

SU1255984A2 |

| Устройство для отображения однократных электрических сигналов | 1983 |

|

SU1141445A1 |

| Устройство для синхронизации последовательностей Д-кода | 1990 |

|

SU1786674A1 |

| Измеритель времени задержки импульсов | 1987 |

|

SU1420598A1 |

Авторы

Даты

1981-06-30—Публикация

1979-05-15—Подача