1

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для реализации технических средств дискретной, автоматики и цифровых вычислительных машин.

Известны устройства сравнения последовательных кодов, содержащие два элемента запрета с перекрестными связями, информациейный вход каждого из которых связан с входом управления другого элемента запрета и с соответствующей входной шиной, два элемента И, один из входов которых соединен с шиной тактовых импульсов, и элемент ИЛИ.

Однако из-за необходимости формирования дополнительных импульсов сброса такое устройство иыеет малое быстродействие.

Предложенное устройство отличается там,что в него введены третий элем . запрета и две динамические схемы памяти, каждая из которых

состоит из последовательно соединенных элемента запрета, элемента ИЛИ и элемента задержки. Выход элемента задержки связан с информационным входом элемента запрета, вход управления которого свя зан с другим входом элемента ИЖ другой динамической схемы памяти и с выходом соответствующего элемента запрета с перекрыстными связями. Выходы элементов ИЛИ динамических схем памяти через элемент ИЛИ связаны с входом управления третьего элемента запрета, информационный вход которого соединен с шиной тактовых импульсов, и с другими входами соответствующих элементов И.

Это позволяет повысить быстродействие устройства.

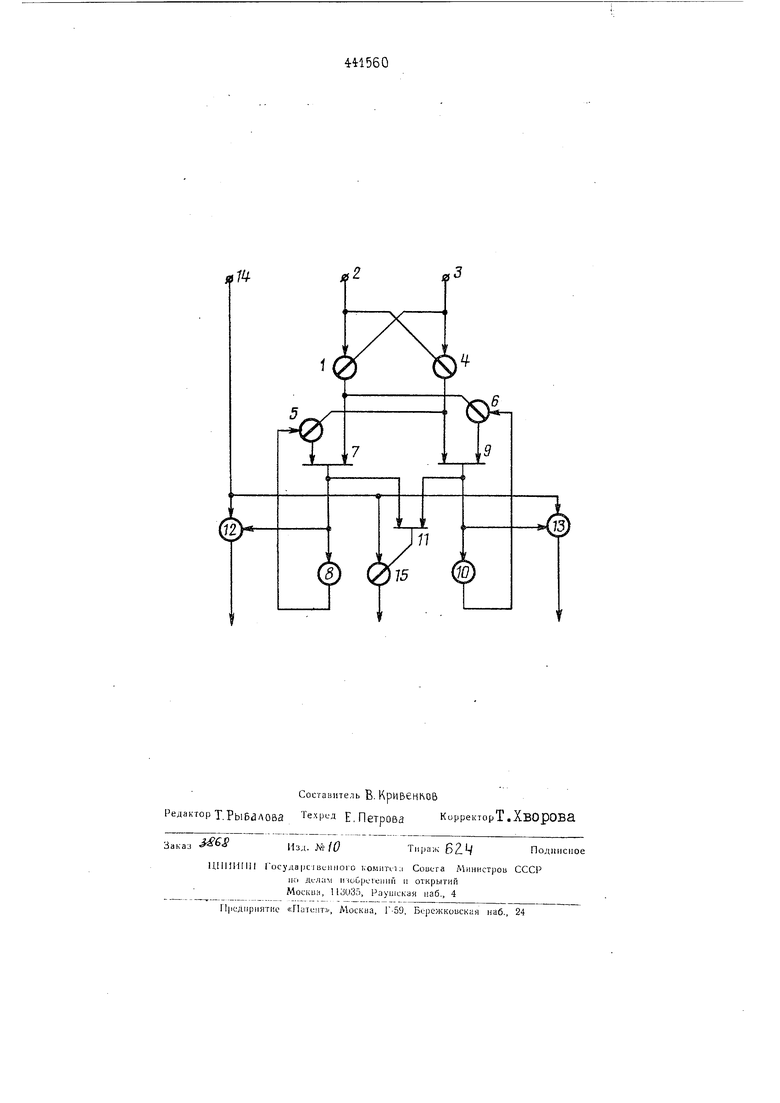

На чертеже показана схема устройства.

Устройство содержит элемент I запрета, информационный вход которого связан с первой входной

ШИНОЙ 2, а запрещающий вход - с второй входной шиной 3. элемент 4 запрета, информационный вход которого соединен с входной шиной 5, а запрещающий - с входной шиной 2. Выходы каждого элемента запрета подключены к управляющим входам элементов 5 и б запрета ооответственно. Выход элемента I запрета через последовательно соединенные элементы ИЛИ 7 и элемент 8 задержки связан с информационным входом элемента 5 запрета, а выход элемента 4 запрета через последовательно соединенные элементы ИЖ 9 и элемент 10 задержки с информационным входом элемента

6запрета.

Выходы элементов 5 и б подключены к входам элементов ИЛИ

7и 9 соответственно. Выходы элементов ИЛИ 7 и 9 соединены с входами элемента ИЖ 11 и с входами эдементов И 12 и 13 соответственно. Вторые входы элементов И 12 и 13 связаны с шиной

14 тактовых импульсов, которая подключена также к информационному входу элемента 15 запрета, управляющий вход которого соединен с выходом элемента ИЛИ II.

Предложенное устройство работает следующим образом.

Первый из сравниваемых кодов подается на шину 2, второй - на шину 3, Сравнение начинается с младших разрядов. Если в каком-то из тактов значение одного из кодо превышает значение другого, то сигнал рассогласования, вырабатываемый элементами I или 4 запрета запоминается в соответствующей динамической схеме памяти - в цепочке, состоящей из элемента задержки, элемента запрета и элемента ИЛИ, Например, если в произвольном такте первый код превышает второй код, то в соответствующей динамической цепочке начинается циркуляция сигнала рассогласования. Для правильной работы устройства элемент задержки должен осуществлять сдвиг импульсов ровно на один такт.

Циркуляция рассогласования в одной из динамических схем памяти продолжается до тех пор, пока рассогласование в более старших разрядах или подтвердит циркуляцию в данной цепочке, или переведет цир куляцию в дру гуюцепочку; предварительно запретив (при помощи элемента запрета) циркуляцию в первой, цепочке. Подтверждение циркуляции происходит в том случае, если рассогласование в старшем разряде имеет тот же знак, что и предыдущее запомненное цепочкой рассогласование; перевод циркуляции осуществляется при смене знака рассогласования,

На последнем и-ом такте ft-й тактовый импульс по шине 14 овраживает элементы 12 и 13, проверяя 5 тем самым состояние обеих динами, ческих цепочек. Если первый код , больше второго, то появляется импульс на выходе элемента ИЛИ 12, в противном случае оказывается 0 импульс на выходе элемента 13, Если же коды равны, то циркуляция рассогласований в любой -из динамических схем памяти отсутствует, в результате чего tL-й импульс поступает на выход элемента 15 запрета,

ПРЕДМЕТ ИЗОБРЕТЕНИЯ

Устройство для сравнения последовательных кодов, содержащее два элемента запрета с перекрестными связями, информационный вход каждого из которых связан с входом управления другого элемента запрета, и с соответствующей входной шиной, два элемента И, один из входов которых соединен с шиной тактовых импульсов, элемент ИЛИ отличающееся тем, что, с целью увеличения быстродействия, в него введены третий элемент запрета и две динамические схемы памяти, каждая из которых состоит из последовательно соединенных элемента запрета, элемента ИЛИ и элемента задержки, причем выход элемента задержки связан с информационным входом элемента запрета, вход управления которого связан с другим входом элемента ИЛИ другой динамической схемы памяти и с выходом соответствующего элемента запрета с перекрестными связями, выходы элементов ИЛИ динамических схем памяти через элемент ИЛИ связаны с входом управления третьего элемента запрета, информационный вход которого соединен с шиной тактовых импульсов, и с другими входами соответствующих элементов И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения чисел | 1978 |

|

SU763891A1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Устройство для управления замещением информации | 1975 |

|

SU651413A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1221757A1 |

| Устройство для сравнения чисел | 1977 |

|

SU734673A1 |

| ПРОГРАММНОЕ УСТРОЙСТВО | 1973 |

|

SU406185A1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2446454C1 |

| Цифровой регулятор | 1982 |

|

SU1056130A2 |

| Цифровой частотомер | 1975 |

|

SU783701A1 |

| Устройство для воспроизведения запаздывающих функций | 1985 |

|

SU1249546A1 |

Авторы

Даты

1974-08-30—Публикация

1972-05-31—Подача