1

Изобретение относится к области цифровых измерений и предназначено для измерения низких и инфранизких чаоаот с широким динамическим диапазоном изменения сигналов.

Известны цифровые частотомеры, реализующие способ обратно пропорционального преобразования периода измеряемого сигнала в каждсяч такте измерения с запоминанием результата преобразования до следующего такта 1 ,

Однако таким частотомерам свойственно запаздывание, равное текущему периоду входного сигнала, и ограниченная динамическая точность.

Наиболее близким к данному техническому решению является прямоотсчетннй цифровой частотомер, содержащий генератор опорной частоты, связанный с входами управляемого делителя частоты и неуправляемого делителя частоты, выход которого подключен ко входу суммирующего счетчика импульсов управляемого делителя, через первый элемент задержки ко входу обнуления счетчика выходных импульсов управляемого делителя и непосредственно ко входу элемента запрета, выход которого подключен

ко входу обнуления суммирующего счетчика управляемого делителя, и через второй элемент задержки к объединенным, управляющим входам группы вентилей переноса кода результата измерения 2,

Такому частотомеру также присущи запаздывание на текущий период измеряемой частоты и ограниченная

10 динамическая точность, уменьшающаяся при увеличении скорости изменения измеряемой частоты, связанные с тем, что в течение текущего периода результат на выходе устройства оста15ется неизменным и равным значению, полученному в предыдущем периоде.

Цель изобретения - повышение быстродействия и уменьшение динаилической ошибки измерения,

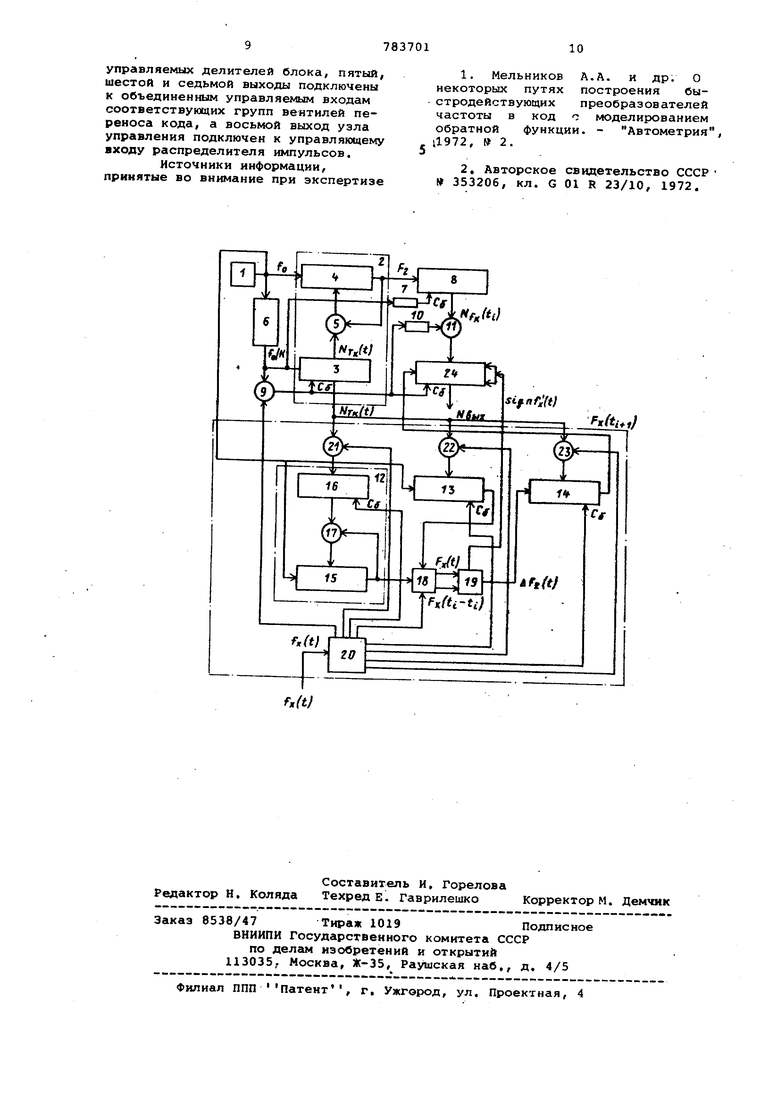

Цель достигается тем,что в устрой20ство введены блок дифференцирования и реверсивный счетчик, причем первый вход блока дифференцирования подключен к . входной шине частотомера, второй вход подключен к выходу генератора опорной частоты, третий ;вход подключен к выходам разрядов суммирующего счетчика управляемого делителя, первый выход блока дифференцирования подключен к управляющему входу элемента запрета, второй выход подключен к-счетному входу реверсивного счетчика, знаковые управлякхцие входы которого подключены к третьему выходу блока дифференцирования, вход рбк ления реверсивного счетчика подКлючен к выходу элемента запрета, а Ьходы разрядов реверсивного счетчика подключены к выходам группы вентиле переноса кода результата, : При этом блок дифференцирования состоит из трех управляемых делите лей частоты, каждый из которых (включает вычитающий счетчик и реги (памяти, соединенные через группу (вентилей переноса кода, трех групп (вентилей переноса кода, распределит ля импульсов, элемента вычитания им (пульсов и узла управления, вход (которого подключен к первому входу (блока дифференцирования, счетные вх ды первого и второго управляемых Делителей блока подключены ко второму входу блока,управляющие входы управляемых делителей через соответ ствующие группы вентилей подключены К третьему входу блока, выходы перво го и второго управляемых делителей подключены ко входам распределителя импульсов, выходы которого подключе ко входам элемента вычитания импуль сов, импульсный выход которого подключен к счетному входу третьего управляемого делителя частоты, выход которого подключен ко второму выход (блока дифференцирования, знаковые выходы элемента вычитания импульсов подключены к третьему выходу блока, первый выход узла управления подклю чен к первому выходу устройства, второй, третий и четвертый выходы подключены ко входам обнуления регистров памяти управляемых делителей, пятый, шестой и седьмой выходы подключены к объединенным управляемым входам соответствующих групп вентилей переноса кода, а восьмой выход узла управления подключен к управляющему входу распределителя импульсов. Функциональная схема цифрового частотомера показана на чертеже. Частотомер содержит генератор 1 опорной частоты, подключенный к управляемому двоичному делителю 2 частоты, состоящему из суммирующего счетчика 3, подключенного к вычитаю щему счетчику 4 импульсов через Вентили 5, неуправляемый делитель 6 частоты, подключенный входом к Генератору 1, а выходом через элемент 7 задержки ко входу обнуления счетчика 8 ыходных импульсов управляемого делителя 2 и непосредственйо к суммирующему счетчику 3 и к эле ,менту 9 запрета, выход которого йодключен ко входу обнуления сумми| ующего счетчика 3 и через элемент id задержки к объединенным управляющим входам вентилей 11 переноса кода результата измерения, соединенных со счетчиком 8, блок дифференцирования, состояыий из трех управляемых делителей 12 - 14 частоты, каждый из которых образован из вычитающего счетчика 15, подключенного к регистру 16 памяти через группу вентилей 17 переноса кода, распределителя 18 импульсов, два входа которого соединены с выходами вычитающих счетчиков 15 делители 12 и 13, а выход - с элементом 19 вычитания, соединенным с делителем 14 узла 20 управления и трех групп вентилей 21-23 переноса кода, реверсивный счетчик 24, счетный вход которого подключен к выходу блока дифференцирования, вход обнуления подключен к выходу элемента 9 запрета, а ВХОДЫ- разрядов соединены с группой вентилей 11 переноса кода результата. Группы вентилей 21 - 23 переноса кода соединяют выход суммирующего счетчика 3 со входами регистров 16 памяти управляемых делителей 12-14. Выход генератора 1 подключен ко входам вычитающих счетчиков 15 делителей 12 и 13. Выходы узла 20 управления соединены с управляющими входами элемента 9 запрета, вентилями 21-23 переноса кода, входами обнуления регистров 16 памяти управляемых делителей 12-14, а вход узла 20 управления соединен с входной шиной частотомера. Устройство работает следующим образом. С приходом первого импульса t -ого такта измерения частоты (t) в узле управления 20 формируется сигнал, снимающий запрет с элемента 9 запрета. Импульсом с делителя 6 элементы устройства устанавливаются в исходное состояние. При этом суммирующий счетчик 3 через элемент 9 запрета устанавливается в О, код из реверсивного счетчика 24 переписывается во внешний регистр памяти (на чертеже не показан), реверсивный счетчик 24 устанавливается в О и в него через время, определяемое элементом 10 задержки переписывается через вентили 11 код из счетчика 8. Элемент 9 запрета закрывается сигналом от узла 20 управления. По второму импульсу измеряемой частоты в узле 20 управления вырабатываются сигналы управления, производящие установку в О регистров 16 памяти в делителе 14 и в одном из делителей 12 или 13 в зависимости от того, в какой из них был записан код в предыдущем такте. Затем производится запиаь кода из счетчика 3 через вентили 23 и 21 или 22 в регистры 16 памяти соответствующих делителей 14 и 12 или 13. В зависимости от того, какой из делителей 12 или . 13 работает в режиме памяти от npefl -дущего такта, узел 20 управления устанавливает распределитель 18 в соответствующее положение, меняя ме тами выходы с каждым последующим тактом. Последовательность импульсов с частотой о подается с генератора 1 на делители 2, б, 12, 13, Частота импульсов на выходе делителя б равн Р io i где К - коэффициент деления не равляемого делителя б, С приходом каждого импульса с выхода делителя 6 счетчик 8 через элемент 7 задержки, сбрасывается Текущее деление кода в счетчике 3 определяется выражением По сигналу с выхода счетчика 4 обратный код из счетчика 3 перепис вается в счетчик 4, который работа в режик1е делителя частоты с переменным коэффициентомделения, вводимым из счетчика 3. Частота на вы ходе счетчика 4 равна г л ГТ Так как в счетчике 8 суммируютс импульсы с частотой 2 в промежутке времени, определяемом моментами сброса, то за время Т в нем сформи руется код, соответствующих момент времени Т и определяемый выражение j, r, ,)J 2d lcJt, (4) лЛ где i - текущее время, С приходом второго импульса L такта измерения входной частоты, соответствующего времени 1 , с мо мента начала преобразования пройде время T(,), За это время в счетч 8 будет сформирован код ) (5 Этот код по сигналу от узла 20 уп равления через вентили 11 перепишется в предварительно очищенный реверсивный счетчик 24, и устройст подготоЕится к следующему такту измерения. За время Т (, ) , равное период измеряемой частоты в С -ом такте измерения, в счетчике 3 образуетс пропорциональный ему код T.it rif xKi) (б) Этот код через вентили 21-23 по с;:гналам управления переноситс В предварительно очищенные регистры пг1мяти делителя 14 и в один из делителей 12 или 13, Последовательностью работы делителей 12 и 13 управляет узел 20 так, чтобы код менялся в одном из них, оставляя неизменным код предыдущего (г- 1)-ого такта в другом. Таким образом, коэффициент деления в делителях 12 и 13 меняется поочередно через такт. Коэффициент деления в делителе 14 меняется каждый такт. Благодаря такому управлению на выходе делителей 12 и 13 формируются последовательности импульсов, пропорциональные входной частоте и сдвинутые друг относительно друга на период Т (tu) . Так, моменту времени tt - концу -ого такта будет соответствовать частота на выходе одного из делитеей 12 или 13, равная Px(t);r- - zrTr;-- ixlt.) (71 .) a моменту времени bt-r- началу г -ого такта будет соответствовать частота на выходе другого делителя p.,)..lt.j xl- -J Импульсные последовательности с этими частотами поступают на входы элемента 19 вычитания частоты через распределитель 18, который по сигналу управления с каждым тактом меняет свои выхода, в результате чего всегда на одном и том же его выходе имеется отстающий по времени сигнал. Это необходимо для определения знака рассогласовани:я сравниваемых в элементе 19 частот, сигнал от которого sign fy (i,) поступает на управляющие, входь реверсивного счетчика 24, устанавливая его в режим сложение либо вычитание, На выходе элемента 19 образуется последовательность импульсов, равная рассогласованию сравниваемкх частот РХ (t). Как известно, при вычитании из исходного сигнала (bl ) защержанного сигнала Рц (tl-Tt), получается величина, пропорциональная первой производной входного сигнала и времени задержки APxN - ,+ 1 dPxK) г dPxItO dPxUH, di,(: t . где T - сумма отброа-енных членоВ ряда Тейлора, представляющая собОй методическую ошибку Для линейнс изменяющихся сигналов и на малом в|)емекном промежутке эта величина п иближается к нулю. Таким образом, нА выходе элемента 19 образуется пфследовательность импульсов, ча-сфота которой пропорциональна первой производной и периоду измеряемой частоты в д, -ом такте измерения. Дфя получения частоты, пропорциональ нфй первой производной измеряемого сигнала и не зависящей от переменногф значения периода согласованной пф коэффициенту пропорциональности с i кодом измеряемой частоты в счетчикф 8, сигнал с элемента 19 делят выделителе 14 с коэффициентом, пропорциональным периоду входной частоты в -ь -ом такте и получаемым в-счетчике 3. На выходе делителя 14 образуется частота f (4. (10) Импульсы этой частоты поступают на счетный вход реверсивного счетчика 24 и в зависимости от знака щэоизводной суммируются или вычитаю ся из внесенного в него кода N(t,. ) На выходе реверсивного счетчика 24 в течение ( + 1)-ого такта измерения непрерывно меняется код, соответствующий мгновенному значению измеряемой частоты в интервале TJ; ТхИ,,, ,г1 P,ltjdt j-f,(t,rч.(..} , di ,H,UAixltO t dt Таким образом,в данном устройстве путем интегрирования на временно Оромежутке текущего такта измерения частоты, пропорциональной первой Производной измеряемого сигнала, вв дится коррекция в результат по скорости измерения измеряемого сигнала Этим самым экстраполируется изменение измеряемой частоты в текущем .ранте .измерения по скорости изменения сигнала в предыдущем такте изме рения. Благодаря этому увеличиваетс быстродействие устройства и уменьша ется динамическая ошибка измерения. Формула изобретения 1. Цифровой частотомер, содержащ генератор опорной частоты, связанны О входами управляемого делителя чайтоты и неуправляемого делителя частоты, выход которого подключен к входу сум « ирующего счетчика импульс управляемого делителя, через первый элемент задержки - ко входу обнуления счетчика выходных импульсов управляемого делителя и непосредственно - ко входу элемента запрета, выход которого подключен ко входу обнуления суммирующего счетчика управляемого делителя, и через второй элемент задержки - к объединенным управляющим входам группы вентилей переноса кода результата измерения, отличающийся тем, что, с целью повышения быстродействия и уменьшения динамической ошибки измерения, в него дополнительно введены блок дифференцирования и реверсивный счетчик, причем первый вход блока дифференцирования подключен к входной шине частотомера, -второй вход подключен к выходу генератора опорной частоты, третий вход подключен к выходам разрядов суммирующего счетчика управляемого делителя, первый выход блока дифференцирования подключен к управляющему входу элемента запрета, второй выход подключен к счетному входу реверсивного счетчика, знаковые, управляющие входы которого подключены к третьему выходу блока дифференцирования, вход обнуления реверсивного счетчика подключен к выходу элемента запрета, а входы разрядов реверсивного счетчика подключены к выходам группы вентилей переноса кода результата, 2, Частотомер по п. 1, о i л ичающийся тем, что блок дифференцирования состоит из трех управляемых делителей частоты, каждый из которых включает вычитающий счетчик и регистр памяти, соединенные через группу вентилей переноса кода, трех групп вентилей переноса кода, распределителя импульсовр элемента вычитания импульсов и узла управления, вход которого подключен к первому входу блока дифференцирования, счетные входы первого и второго управляемых делителей блока подключены ко второму входу блока, управляющие входы управляемых делителей через соответствующие группы вентилей подключены к третьему входу блока, выходы первого и второго управляемых делителей блока подключены ко входам распределителя импульсов, выходы которого подключены ко входам элемента вычитания импульсов, выход которого подключен к счетному входу третьего управляемого делителя частоты, выход которого подключен к второму выходу блока дифференцирования, знаковые выходы элемента вычитания импульсов подключены к третьему выходу блока, первый выход узла управления подключен к первому выходу частотомера, второй, третий и четвертый Ч&ыходы подключены ко входам обнуления регистров памяти

управляемых делителей блока, пятый, шестой и седьмой выходы подключены к объединенным управляемым входам соответствующих групп вентилей переноса кода, а восьмой выход узла управления подключен к управляющему входу распределителя импульсов.

Источники информации, принятые во внимание при экспертизе

1,Мельников А.А. и др. О некоторых путях построения бы. стродействующих преобразователей частоты в код с моделированием обратной функции. - Автометрия, 11972, № 2.

2.Авторское свидетельство СССР W 353206, кл. G 01 R 23/10, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования частоты в код | 1977 |

|

SU696604A1 |

| Устройство цифрового задания частоты следования импульсов | 1976 |

|

SU641455A1 |

| Устройство для преобразования суммы частотно-импульсных сигналов в код | 1976 |

|

SU657441A1 |

| Устройство для дифференцирования частотно-импульсных сигналов | 1976 |

|

SU624244A1 |

| Датчик углового положения,скорости и ускорения вращения вала | 1983 |

|

SU1101740A1 |

| Цифровой частотомер | 1973 |

|

SU481851A1 |

| Цифровой определитель дисперсии | 1978 |

|

SU767772A1 |

| Устройство для формирования импульсных последовательностей | 1975 |

|

SU618839A1 |

| Устройство умножения частоты следования импульсов | 1975 |

|

SU528695A1 |

| Часточно-импульсное дифференцирующее устройство | 1977 |

|

SU691891A1 |

)

Авторы

Даты

1980-11-30—Публикация

1975-02-03—Подача