О1

о

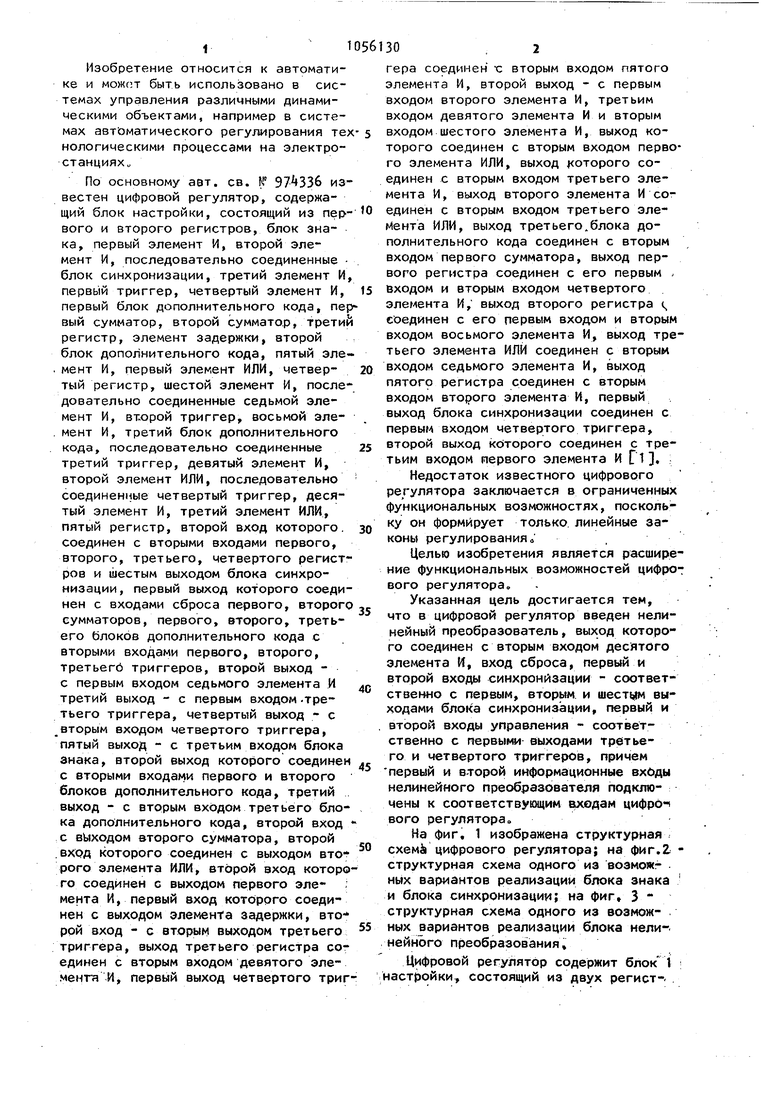

00 Изобретение относится к автоматике и может быть использовано в системах управления различными динамическими объектами, например в системах автоматического регулирования те нологическими процессами на электростанцияхПо основному авт. св. ff из вестен цифровой регулятор, содержащий блок настройки, состоящий из пер вого и второго регистров, блок знака, первый элемент И, второй элемент И, последовательно соединенные блок синхронизации, третий элемент И первый триггер, четвертый элемент И, первый блок дополнительного кода, пе вый сумматор, второй сумматор, трети регистр, элемент задержки, второй блок дополнительного кода, пятый эле . мент И, первый элемент ИЛИ, четвертый регистр, шестой элемент И, после довательно соединенные седьмой элемент И, вт-орой триггер, восьмой эле. мент И, третий блок дополнительного кода, последовательно соединенные третий триггер, девятый элемент И, второй элемент ИЛИ, последовательно соединенные четвертый триггер, десятый элемент И, третий элемент ИЛИ, пятый регистр, второй вход которого, соединен с вторыми входами первого, второго, третьего, четвертого регист ров и шестым выходом блока синхронизации, первый выход которого соеди нен с входами сброса первого, второг сумматоров, первого, второго, третьего блоков дополнительного кода с вторыми входами первого, второго, третьегб триггеров, второй выход с первым входом седьмого элемента И третий выход - с первым входом -третьего триггера, четвертый выход - с вторым входом четвертого триггера, пятый выход - с третьим входом блока знака, второй выход которого соединен с вторыми входами первого и второго блоков дополнительного кода, третий выход - с вторым входом третьего блока дополнительного кода, второй вход с выходом второго сумматора, второй .вход которого соединен с выходом вто рого элемента ИЛИ, второй вход которо го соединен с выходом первого элемента И, первый вход которого соединен с выходом элемента задержки, вто- рой вход - с вторым выходом третьего триггера, выход третьего регистра cor единен с вторым входом девятого элеменгя И, первый выход четвертого триг гера сое.динен с вторым входом пятого элемента И, второй выход - с первым входом второго элемента И, третьим входом девятого элемента И и вторым входом шестого элемента И, выход которого соединен с вторым входом первого элемента ИЛИ, выход | оторого соединен с вторым входом третьего элемента И, выход второго элемента И соединен с вторым входом третьего элемента ИЛИ, выход третьего.блока дополнительного кода соединен с вторым входом первого сумматора, выход первого регистра соединен с его первым . входом и вторым входом четвертого элемента И, выход второго регистра t, соединен с его первым входом и вторым входом восьмого элемента И, выход третьего элемента ИЛИ соединен с вторым входом седьмого элемента И, выход пятого регистра соединен с вторым входом второго элемента И, первый выход блока синхронизации соединен с первым входом четвертого триггера, второй выход kdTOporo соединен с третьим входом (первого элемента И Г1 . i Недостаток известного цифрового регулятора заключается в ограниченных функциональных возможностях, поскольку он формирует только линейные законы регулирования Целью изобретения является расширение функциональных возможностей цифро-: вого регулятора. Указанная цель достигается тем, что в цифровой регулятор введен нелинейный преобразователь, выход которого соединен с вторым входом десятого элемента И, вход сброса, первый и второй входы синхронизации - соответственно с первым, вторь м и шестом выходами блока синхронизации, первый и второй входы управления - соответственно с первыми выходами третьего и четвертого триггеров, причем первый и второй информационные вхОды нелинейного преобразователя подключены к соответствующим ерсодам цифрО-ч вого регулятора. На фиг, 1 изображена структурная cxeMi цифрового регулятора; на фиг. структурная схема одного из аозможг ных вариантов реализации блока знака и блока синхронизации; на фиг, 3 структурная схема одного из возможных вариантов реализации блока нели-нейного преобразования. Цифровой регуЛятОр содержит блок 1 астройки, состоящий из двух регистров 2 и 3, три регистраЛ-6, два сум матора 7 и 8, блок 9 знака, блок 10 синхронизации, три блока 11-13 дополнительного кода, четыре триггера нелинейный преобразователь 18, 5 три элемента ИЛИ , десять элементов И 22-31, элемент 32 задержки.

Цифровой регулятор имеет информаj4MOHHue шины: входные 33 и 3 и одну выходную 35,а также шины знака: вход- О ныв 36 и 37 и одну выходную 38.Регистры 2-6 имеют группы шин уЛрйВления и ввода данных соответственно.

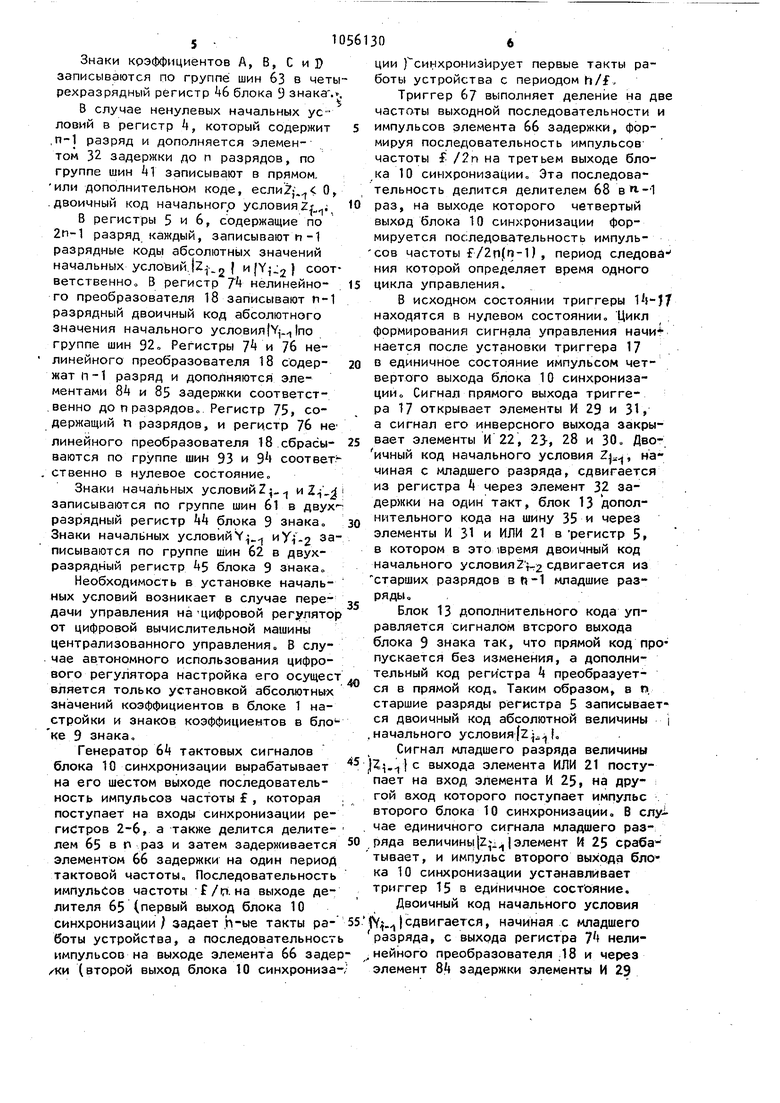

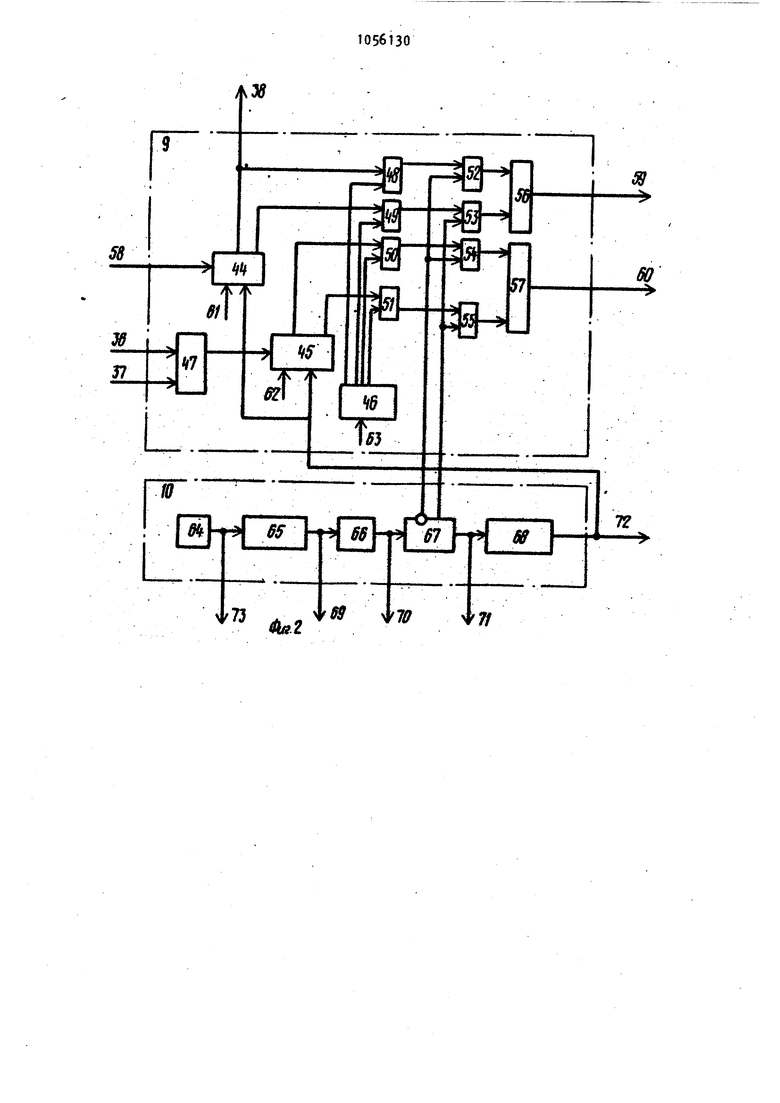

Блок 9 знака (фиг, 2 I содержит дв4 двухразрядных регистра- и 5 рдвига, четырехразрядный регистр t, пять элементов ИСКЛЮЧАЮЩЕЕ ИЛИ , четыре элемента И 52-55, два элемента ИЛИ 5б и 57, входную шину 5В и две выходные шины 59 и 60, группы шин 61-20 63 для управления и ввода данных в регистры -46 соответственно Шины 36-38 блока 9 знака являются соответственно первой, второй входными шинами знака и выходной шиной знака 25 цифрювого регулятора.

Блок 10 синхронизации (фиг. 2)содержит генератор 6k тактовых импульсов, первый делит &ль 65 частоты, элемент 66 задержки, т иггер 67 со счет-зо ным входом, второй делитель 68 частоты, выходные шины 69-73.

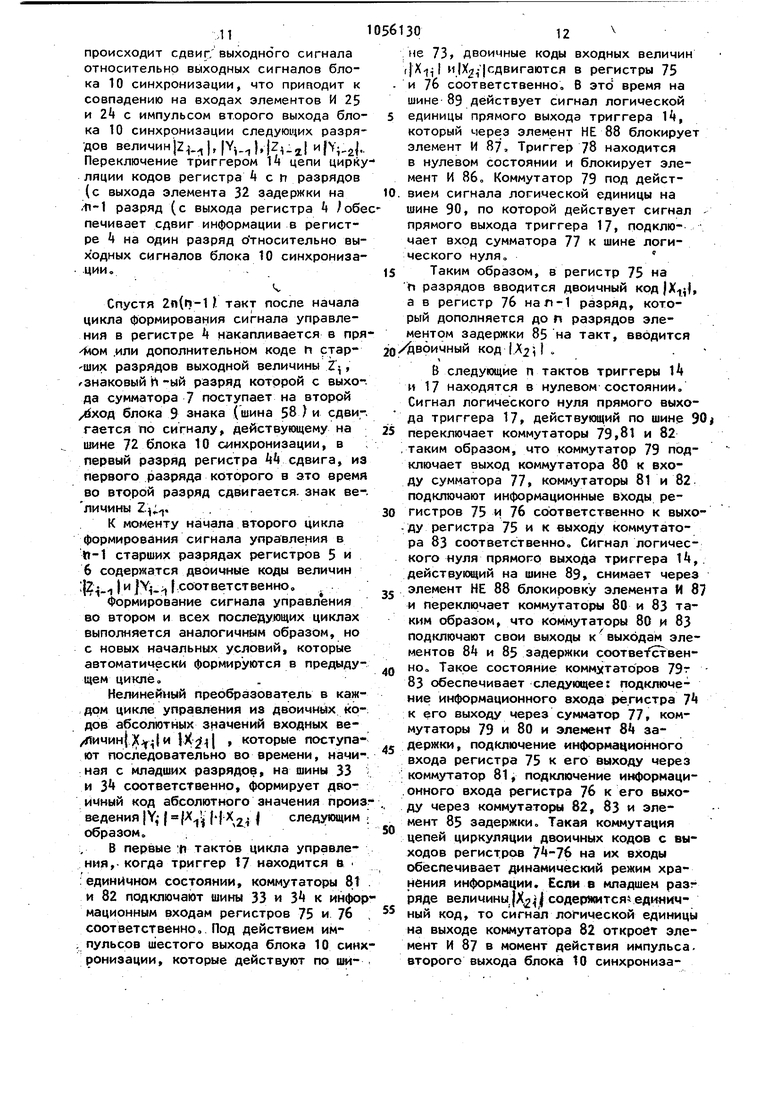

Нелинейный преобразователь 18 (фиг, 3 ) содержит три регистра , сумматор 77, триггер, 78, пять коммутаторов 79-83, два элемента 8V и 85 задержки, два элемента И 86 и 87, элемент НЕ 88, две шины 89 и 90 управления, выходную шину 91, группу шии 92-9t управления, для ввода данных в регистры соответственно.

Цифровой регулятор работает следу 1б1дим образом.

Регулирующее воздействие для каж- . дого iTO цикла управления формируется согласно рекуррентному соотношению

- ,BZb2CYi. Y XirXziVfn

где значение первой и вто- 50 рой входной величины цифрового регулятора соответственно в каждом

1-ом цикле управления; Yj. значения преобразован- 55 ного рассогласования на 1-1 и l-2-ом циклах управления;

Z, ZjM значения регулирующего воздействия на i, i-1 и i-2-ом цикла управления;

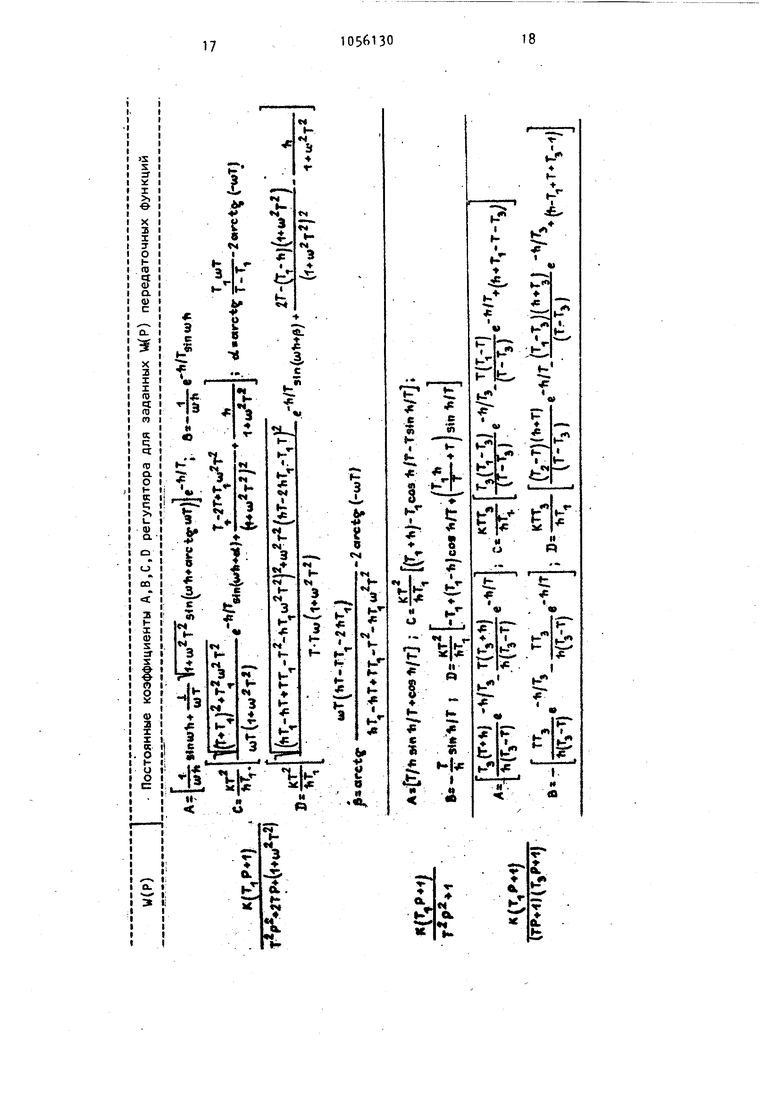

А,В, С и D - постоянные коэффициенты, значения которых зависят от вида закона управления, шага ,квантования по времени, коэффициента усиления и постоянных времени.,

Настройка цифрового регулятора осу ществляетсч заданием постоянных коэф4|ициентов А, В, С и D и начальных условий Zf, , Z, ,-.и Y , которые, в частности, могут быть нулевыми.

Предварительный расчет постоянных коэффициентов -А, В, Си D для часто реализуемых законов управления выполняют по формулам, приведенных в таблице , где К - коэффициент усиления; Т -1 Т, Т, ,Тд- постоянные времени; h - шаг квантования по времени,выбираемой из условий заданной точности.

Цифровой регулятор оперирует с двоичными переменными, для которых соотношение (1) принимает следующий вид п-1 .

(in-/V2 .- j,«J

v,E:2-

.y..i

jrl

где индекс j обозначает ;-ый разряд двриыной переменной соответствующей величины, например,Zj:j двоичная переменная j-ro разряда величины 2ц

Количество разрядов представления величин составляет Vi-1 разряд, п-ый разряд - знаковый.

Настройка цифрового регулятора выполняется следующим образом,

В регистры 2 и 3 блока 1 настройки, содержащие по 2п разрядов каждый, записывают по шинам 35 и АО соответственно, например, от цифровой вычислительной машины централизованного управления либо от цифрового задатчина диспетчерского пульта двоичные П-разрядные коды абсолютных значений коэффициентов А, В,С и D соответственно, которые соответствуют требуемому линейному интегродифференциальному эакону управления (таблица ), Для эаписи информации в регистры 2 и 3 используются выходные сигналы блока 10 синх(юнизации. Знаки коэффициентов А, В, Сир записываются по группе шин 63 в четы рехразрядный регистр +6 блока Э знака. В случае ненулевых начальных условий в регистр k, который содержит ,п-| разряд и дополняется элементом 3 задержки до п разрядов, по группе шин Т записывают в прямом. ИЛИ дополнительном коде, если2.. О, .двоичный код начального условия2|„ ; В регистры 5 и 6, содержащие по 2п-1 разряд каждый, записывают п-1 разрядные коды абсолютных значений начальных условий.|Z|.2 } ) соот ветственнОо В регистр 7 нелинейного преобразователя 18 записывают п-1 разрядный двоичный код абсолютного значения начального условия(Y.lno группе шин 92 о Регистры 7 и 76 нелинейного преобразователя 18 содержат разряд и дополняются элементами 84 и 85 задержки соответст.венно до празрядов. Регистр 75, содержащий п разрядов, и регистр 7б нелинейного преобразователя 18 сбрасываются по группе шин 93 и 9 соответ. . ственно в нулевое состояние Знаки нача;1ьных условий Z и записываются по группе шин б1 в двух разрядный регистр k блока 9 знака Знаки начальных условийУ. иУ|.2 записываются по группе шин б2 в двухразрядный регистр 45 блока 9 знака Необходимость в установке начальных условий возникает в случае передачи управления на цифровой регулятор от цифровой вычислительной машины централизованного управления В случае автономного использования цифрового регулятора настройка его осущест вляется только установкой абсолютных значений коэффициентов в блоке 1 настройки и знаков коэффициентов в блоке 9 знака. Генератор 64 тактовых сигналов блока 10 синхронизации вырабатывает на его шестом выходе последовательность импульсов частоты , которая поступает на входы синхронизации регистров 2-6, а также делится делителем б5 в п раз и затем задерживается элементом 66 задержки на один период тактовой частоты Последовательность импульсов частоты f/i;i. на выходе делителя 65 (первый выход блока 10 синхронизации / задает такты работы устройства, а последовательност импульсоо на выходе элемента 66 заде /ки (второй выход блока 10 синхрониза ции ) синхронизирует первые такты работы устройства с периодом h/f. Триггер б7 выполняет деление на две частоты выходной последовательности и импульсов элемента 66 задержки, формируя последовательность импульсов частоты f /2п на третьем выходе блока 10 синхронизациио Эта последовательность делится делителем 68 в --I раз, на выходе которого четвертый выход блока 10 синхронизации формируется последовательность импульсов частоты f/2п(п-1) , период следовйния которой определяет время одного цикла управления. В исходном состоянии триггеры 1}-J7 находятся в нулевом состоянии. Цикл формирования сигнала управления начи нается после установки триггера 17 в единичное состояние импульсом четвертого выхода блока 10 синхронизации Сигнал прямого выхода триггера 17 открывает элементы И 29 и 31 а сигнал его инверсного выхода закрывает элементы И 22, 23-, 28 и 30. Двоичный код начального условия Z|,, начиная с младшего разряда, сдвигается из регистра 4 через элемент 32 задержки на один такт, блок 13 дополнительного кода на шину 35 и через элементы И 31 и ИЛИ 21 в регистр 5, в котором в этоивремя двоичный код начального условия Zfr2 сдвигается из старших разрядов в п-1 младшие разряды, Б.ПОК 13 дополнительного кода управляется сигналом второго выхода блока 9 знака так, что прямой код про пускается без изменения, а дополнительный код регистра 4 преобразуется в прямой код. Таким образом, в п, старшие разряды регистра 5 записывается двоичный код абсолютной величины начального условия|2 I Сигнал младшего разряда величины Z:;. I с выхода элемента ИЛИ 21 поступает на вход элемента И 25i на другой вход которого поступает импульс второго блока 10 синхронизации, В cny-iчае единичного сигнала младшего разряда вели чины |2: I элемент И 25 срабатывает, и импульс второго выхода блока 10 синхронизации устанавливает триггер 15 в единичное состояние. Двоичный код начального условия fy.)сдвигается, начиная с младшего разряда, с выхода регистра 74 нелинейного преобразователя ;18 и через элемент 84 задержки элементы И 29

и или 20 записывается в п старших разрядов регистра 6„ В регистре 6 о это время двоичный код начального

.условия|У,2сдвигается из старших разрядов в п-1 младшие разряды,

Сигнал младшего разряда величины|У.|с выхода элемента ИЛИ 20 поступает на вход элемента И 2, В случае единичного сигнала младшего разряда величины| 5 -1 элемент И 2 ерабатывает по импульсу второго выхода блока 10 синхронизации, и триггер 16 устанавливается в единичное состояние,

. Триггеры 15 и 16 в единичном состоянии открывают элементы И 26 и 27 соответственно, через которые с выходов регистров 2 и 3 блока 1 настройки последовательно, начиная с младших разрядов, сдвигаются двоичные коды коэффициентов Л и С соответственно.

Коэффициент Л поступает через блок 11 дополнительного кода на первый вход сумматора 8 в прямом или дополнительном коде в зависимости от

внака произведения AZ, сигнал которого действует на втором выходе блока 9 знака. Сигнал знака величины

,А2 формируется элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 8, на входы которого поступают сигналы выходов первых разрядов регистров k и 46, где хранятся знаки величин 2 и А соответственно,

Сигнал знака величины с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ й поступает через элементы И 52 и ИЛИ 56 на шину 59 второго выхода блока 9 знака.

Коэффициент С поступает через блок 12 дополнительного кода на второй вход сумматора 8 в прямом или до полнительном коде в зависимости от знака произведения CY, , сигнал которого формируется элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 50, на входы которого посту.пает сигнал знака величины Y с вы хода первого разряда .регистра 5 и сигнал знака коэффициента С с выхода третьего разряда регистра k6 блока 9 знака.:

Сигнал знака величины CV.-j е- выхода элемента ИСКЛЮЧАЮи1ЕЕ ИЛИ 50 чере .элемент И 5 открытый сигналом инверсного выхода триггера 67, и элемент ИЛИ 57 поступает на третий выход блока 9 знака.

Таким образом, на входы последова;тельного одноразрядного двоичного сумматора 8 поступают в прямом или дополнительном коде последовательно во времени, начиная с младшего разряда, двоичные коды коэффициентов А и С, алгебраическая сумма которых поступает на второй вход последовательного одноразрядного двоичного сумматора 7 В это время на первом входе сумматора 7 действует сигнал логического нуля, так как элементы И 22 и 23 закрыты сигналом инверсного выхода триггера 17,

Алгебраическая сумма коэффициентов А и С с выхода одноразрядного последовательного сумматора 7 записывается, начиная с младшего разряда, в ргистр j,

В конце каждого rt-ro такта сигнал первого выхода блока 10 синхронизации блокирует цепи переносов сумматоров 7 и 8, а также сбрасывает блоки 11-13 дополнительного кода в исходное состояние.

Спустя п тактов после установки триггера 17 в единичное состояние триггеры сбрасываются в нулевое состояние импульсом первого выхода блока 10 синхронизации. Триггер 17 в нулевом состоянии закрывает элементы И 29 и 31 сигналом прямого выхода и открывает элементы И 22, 23, 28 и 30 сигналом инверсного выхода. Элементы И 28 и 30 подключают выходы регистров 5 и 6 к их входам соответственно. Цепи циркуляции кодов в регистрах 5 и 6 сдвига замыкаются через элементы И 28 и 30 соответственно.

Элемент И 23, открытый сигналами инверсных выходов триггеров 1А и 17, подключает выход регистра Ц через элемент 32 задержки к первому входу сумт матора 7, что обеспечивает в течение следующих тактов поступление на первый вход сумматора 7 двоичного кода алгебраической суммы коэффициентов (А+СК

L ,

В следующем такте после возврата триггера 17 в нулевое состояние с выходов регистров 5 и 6 сдвигаются разряды величины |z.2 и |Y, соответственно,

В случае единичных кодов в младших разрядах величин|2-.2} и ( элементы И 25 и 2 срабатывают по импульсу второго выхода блока 10 синхронизации, что приводит к установке триггеров 15 и 16 соответственно в единичное состояние. Сигналы прямых выходов триггеров 15 и 16 открывают соответственно элементы И 26 и 27, через которые с выходов регистров 2 . и 3 блока 1 настройки сдвигаются дво ичные коды коэффициентов В и D соот ветственно.. Двоичные коды коэффициен тов Вир преобразуются соответствую щими блоками 11 и 12 дополнительного кода и поступают последовательно, начиная с младшего разряда, в прямом или дополнительном коде на входы сумматора 8„ Управление преобразование,м блоками 11 и 12 дополнительного кода осуществляется по сигналам второго и третьего выходов блока 9 знака соответственно Сигнал знака произведе ния формируется элементом ИСКЛЮЧЛЮЩЁН ИЛИ 9, на входы которого поступают выходы вторых разрядов kk и 6 регистров блока 9 знака, где /хранятся знаки величин 2.2 соответственноо С выхода элемента ИСК/ВОЧЛЮЩЕЕ ИЛИ if9 сигнал знака величины через элементы И 53 и ИЛИ 5 поступает на шину 59 второго выхода блока 9 знака Сигнал знака произведения BY.o формируется элементом ИСКЛЮЧАЮЩЕЕ Или 51 по сигналам выходов второго и четвертого разрядов регистров 45 и г 46. блока 9 знака о С выхода элемен та ИСКЛЮЧЛЮи|ЕЕ ИЛИ 51 сигнал знака произведения DYi-2 считывается через элементы И 55 ИЛИ 57 на шину 60 третьего выхода блока 9 знака„ Прямой или дополнительный код алгебраической суммы коэффициентов В и и с выхода сумматора 8 поступает на второй вход сумматора 7, на первый вход которого с выхода регистра 4 через элемент 32 задержки, элементы И 23 и ИЛК 19 сдвигается -двоичный код алгебраической суммы коэффициентов Л и Со С выхода сумматора 7 двоичный код алгебраической суммы коэффициентов А, В, Си J) запи сывается в регистр 4„ . Таким образом, за 2и тактов после начала цикла в регистре 4 накапливается алгебраическая сумма коэффициен тов А, В, С иБ, после чего триггер , устанавливается в единичное состояние импульсом третьего выхода блока синхрон 1зации. Триггер 14 в единичном состоянии открывает сигналом пря мого выхода элемент И 22 и блокирует элемент И 23 сигналом инверсного вы хода« К моменту сдвига второго paap да алгебраической суммы коэффициенутов А, В, С и В с выхода регистра 4 элемент- И 22 подключает выход регистра 4 к первому входу сумматора 7- В . это время с выходов регистров 5 и 6 Сдвигаются вторые разряды еличин |2. j и СУ I соответственно о В случае единичных кодов во вторых разря х величин|2 1.1 и|У.-, срабатывают элементы И Й5 и И 24, выходные сигналы которых устанавливают триггеры 15 и 16 в единичное состояние. Двоичные кодыпроизведения коэффициентов Аи С на двоичные .пере- Мённые вторых разрядов величин 2), и|У.} соответственно преобразуются в прямой или дополнительный код блоками 11 и 10 соответственно Затем эти коды суммируются сумматором 8, сигнал суммы которого суммируется сумматором 7 с двоичным кодом алгебраической суммы коэффициентов А, В, С и I), сдвигаемой с выхода регистра 4,начиная с второго разряда. Следовательно, установка триггера 14 в единичное состояние приводит к сдвигу на один разряд накопленной суммы коэффициентов в регистре 4, обеспечивая Э.ТИМ выполнение операции умножения на два. Спустя п тактов после установки триггера 14 в единичное состояние сигнал первого выхода блока 10 синхронизации возвращает триггер 14 в нулевое состояние, в котором обеспечивается подключение элементом И 23 выхода регистра 4 через элемент 32 задержки на такт к первому входу сумматора 7« В это время на второй вход сумматора 7 с выхода сумматора 8 поступает двоичный код алгебраической суммы произведения коэффициентов В и р на двоичные переменные вторых разрядов величин|2 2 I )-2 f. соответственно которая формируется таким же образом, как и в предыдущие Г тактов формировалась алгебраическая сумма произведения коэффициентов А и С на двоичные переменные вторых разрядов величин |) IY. соответственное Сумматор 7 суммирует сумму коэффициентов в регистре 4 с алгебраической суммой произведения коэффициентов В и D на двоичные переменные вторых pai .рядов величин|Е; Ц; I и соответст веннр, и результат суммирЬвания записывается В pej-истр 4 о В дальнейшем формирование регулирующего воздействия выполняется аналогичным образом. Каждьге 2п,тактов в кольцевых, регистрах 5 и 6, содержищих 2(п-1I разряд,

происходит сдвиг. выходного сигнала относительно выходных сигналов блока 10 синхронизации, что приводит к совпадению на входах элементов И 25 и 2 с импульсом второго выхода блока 10 синхронизации следуюидих разря-дов величинlZ|..,l,|Y.J,}2-j| .. Переключение триггером 1ч цепи циркуляции кодов регистра А с п разрядов (с выхода элемента 32 задержки на .п-1 разряд (с выхода регистра )обес печивает сдвиг информации в регистре А на один разряд Относительно выходных сигналов блока 10 синхронизации,

v

Спустя 2п(п-1 I такт после начала цикла формирования сигнала управления в регистре 4 накапливается в пряФюм .или дополнительном коде и старШих разрядов выходной величины Z,

/знаковый h -ый разряд которой с выхо-. да сумматора 7 поступает на второй

ход блока 9 знака (шина 58 ) и сдви-, гается по сигналу, действующему на шине 72 блока 10 синхронизации, в ; первый разряд регистра сдвига, из первого разряда которого в это время во второй разряд сдвигается, знак ве-.

личины Z.;.. .

К моменту начала второго цикла формирования сигнала управления в П-1 старших разрядах регистров 5 и 6 содержатся двоичные коды величин

.,) и |Y. соответственно,

Формирование сигнала управления во втором и всех последующих циклах выполняется аналогичным образом, но с новых начальных условий, которые автоматически формируются в предыдущем цикле, .

Нелинейный преобразователь в каждом цикле управления из двоичных ко-: дов абсолютных значений входных ве/Личин|Х; -|и , которые поступают последовательно во времени, нами-, нал с младших разрядов, на шины 33 1 и З соответственно, формирует двоичный код абсолютного значения произведения |Y, ({Х 21 I следующим; образом, .

В первые :п тактов цикла управления, когда триггер t7 находится & .

:единичном состоянии, коммутаторы 8t и 82 подключают шины 33 и 3 к информационным входам регистров 75 и 76 , соответственноо. Под действием им, пульсов шестого выхода блока 10 синхронизации, которые действуют по шине 73 двоичные коды входных величин и|Х2,-|сдвигаются в регистры 75 и 76 соответственно, В это время на шине 89 действует сигнал логической единицы прямого выхода триггера Ц, который через элемент НЕ 88 блокирует элемент И 87, Триггер 78 находится в нулевом состоянии и блокирует элемент И 86, Коммутатор 79 под действием сигнала логической единицы на шине 90, по которой действует сигнал прямого выхода триггера 17, подключает вход сумматора 77 к шине логического нуля,

Таким образом, в регистр 75 на п разрядов вводится двоичный код)Х.,)Ь а в регистр 76 нал-1 разряд, который дополняется до п разрядов элементом задержки 85 на такт, вводится ХЙВОИЧНЫЙ код |X2il.

В следующие п тактов триггеры И и 17 находятся в нулевом состоянии. Сигнал логического нуля прямого выхода триггера 17, действующий по шине 90 переключает коммутаторы и 82 таким образом, что коммутатор 79 подключает выход коммутатора 80 к входу сумматора 77, коммутаторы 81 и 82 подключают информационные входы регистров 75 и 76 соответственно к выходу регистра 75 и к выходу коммутатора 83 соответственно. Сигнал логического нуля прямого выхода триггера 14,. действующий на шине 89, снимает через элемент НЕ 88 блокировку элемента И 87 и перекл10чает коммутаторы 80 и 83 таким образом, что коммутаторы 80 и 83

подключают свои выходы к выходам элементов 84 и 85 задержки соотве ственно. Такое состояние коммутаторов 79т 83 обеспечивает следующее: подключение информационного входа регистра 74 к его выходу через сумматор 77, коммутаторы 79 и 80 и элемент 84 задержки , подключение информационного входа регистра 75 к его выходу через коммутатор 81, подключение информаци.онного входа регистра 76 к его выходу через коммутаторы 82, 83 и элемент 85 задержки. Такая коммутация цепей циркуляции двоичных кодов с выходов регистров 74-76 на их входы обеспечивает динамический режим хранения информации. Если в младшем разг ряде величины.}Х.2,)|содерисится4 единичный код, то сигнал логической единицы на выходе коммутатора 82 откроет элемент И 87 в момент действия импульса, второго выхода блока 10 синхрониза1310Триггер 78 устанавли ции на шине 70 вается в единичное состояние выходны сигналом элемента И 87 на время П; та тов. Сигнал прямого выхода триггера 7В открывает элемент И 86, через который на вход сумматора 77 сдвигается, начиная с младших разрядов, .двоичный код величиныJX I с выхода регистра 75 За п тактов двоичный ко .величины |Х I переписывается с выхо да регистра 75 через коммутатор 81, элемент И 86 и сумматор 77 в ре-, гистр 7 в следующие п тактов на шине 89 устанавливается сигнал логической ед ницы прямого выхода триггера 14, который блокирует через элемент НЕ 88, элемент И 87 и подключен с помощью коммутаторов 80 и 83 выходы регистров 7 и 76 к входам коммутаторов 79 и 82 соответственно Цикл циркуляции кодов в регистрах 7 и 76 сокращаются на один такт что обеспечивает сдвиг кодов на один разряд в регистрах 74 и 76 по отноше нию к коду в регистре 75, цикл циркуляции кодов, в котором по-прежнему составляет п тактов. Таким образом, сигнал логической единицы на шине 89 прямого выхода триггера 14, действующий в нечетные п тактов че/рез каждые 2п тактов, обеспечивает сдвиг информации в регистрах 74 и 76 по отношению к информации в.регистре 75. Во время четных п тактов через каждые 2 тактов на шине 89 действуе сигнал логического нуля триггера 14, который снимает блокировку элемента И 87 через элемент НЕ 88, На входах элемента И 87 произойдет совпаде ние с импульсом второго выхода бло,ка 10 синхронизации, действующим на шине 70, сигнала единичного кода вто рого разряда величины I, поступающего с выхода коммутатора 82. Триггер 78 устанавливается в единичное состояние на п тактов выходным сигналом элемента И 87 и снимает бло кирбвку элемента 86, через который н вход сумматора 77 с выхода коммутатора 81 поступает, начиная с младшего разряда, двоичный код величины |Xii |„ В это время на другой вход сум матора 77 через коммутаторы 79-80 и элемент 84 задержки сдвигается с выхода регистра 74 двоичный код величины Х, начиная с второго разряда, так как в предыдущие h тактов информация в регистре 7 была сдвинута относительно информации в регистре 75 Последовательный двоичный сумматор 77 суммирует .двоичные коды, поступающие на его входы, и результат сдвигается в регистр 7 Дальнейшие вычисления в блоке 18 нелинейных преобразований осуществляются аналогичноТаким образом, в регистре 7 за время одного цикла управления, состав1яющего 2ti(h-.1| тактов накапливается двоичный код старших разрядов произведения )., (. , который в первый Г1 тактов следующего цикла управления сдвигается с выхода регистра 7 через элемент 84 задержки и по шине 91 поступает через элементы И 29 и ИЛИ 20 на информационный вход регистра 6, где записывается в его h старшие разряды В это время в регистре 6 из старших разрядов в младшие разряды сдвигается двоичный код величины jYi-., -сформированный нелиней Ь1М преобразователем 18 на предыдущем цикле управления. В первом такте каждого цикла управления сигналы знаков входных величин Xl,. и Х2 , поступающие по шинам 36 и 37 в блок 9 знака, преобразуются элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 47 ,в сигнал знака произведения, ОПЫЙ сигналом, действующим на шине 72 блока синхронизации 10 сдвигается в первый разряд регистра 45, из которого во второй разряд сдвигается код знака -произвет Дения У., сформированный на предыдущем цикле управления. Двоичный код абсолютного значения регулирующего воздействия 12 f и си|- нал его знака действуют на шинах 35 и 38 соответственно в начале каждого цикла управления. Помимо широкого набора линейных интегродифференциальных законов управления первого и второго порядка данный цифровой регулятор выполняет нелинейное преобразование над входными сигналами, что позволяет реализовать адаптивные законы управления и этим повысить качество управления. Например, если на первый информационный вход цифрового регулятора поступает сигнал рассогласования, а на второй вход - сигнал, пропорциональный возмущению, действующему на объект регулирования, или нагрузке на объект регулирования, то цифровой регулятор 15 , 10 реализует интегродифференциальный закон управления с переменным коэффи- . циентом усиления. Если на оба информационных входа цифрового регулятора подать сигнал рассогласования, то цифровой регулятор реализует интегродифференциальный закон управления над квадратом сигнала рассогласования, что повышает качество управления при значительных сигналах рассогласования. Если на один вход цифрового регуля topa подать сигнал рассогласования, а на второй вход - сигнал цифрового программно-временного устройства, то переключаемый коэффициент усиления цифрового регулятора принимает свое.знйчение согласно изменениям сигнала цифрового программно-временного устройства. 0 - 16 Цифровой регулятор можно использовать для формирования линейных и нелинейных законов управления любого порядка. В этом случае несколько цифровых регуляторов соединяются последовательно так, что выходные шины 35 и 38 каж/joro предыдущего цифрового регулятора подключаются к одной из групп входных шин 33 и 36 или З и 37 соответственно. Оставшиеся свободными входные шины 33 и 36 или 3 и 37 цифровых регуляторов используют для адаптивного изменения параметров законов управления либо подключают к шинам логического нуля или единицы. Таким образом, широкие функциональные возможности цифрового регулятора значительно расширяют область его применения, что обуславливает получение определенного технико-экономического эффекта.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой регулятор | 1980 |

|

SU938255A1 |

| Цифровой регулятор | 1981 |

|

SU974336A1 |

| Квадратор | 1985 |

|

SU1258826A2 |

| Интегро-дифференциальный вычислитель | 1980 |

|

SU955051A1 |

| Интегро-дифференциальный вычислитель | 1981 |

|

SU1020823A1 |

| Интегро-дифференциальный вычислитель | 1983 |

|

SU1108445A2 |

| Цифровой регулятор | 1979 |

|

SU938253A1 |

| Интегродифференциальный вычислитель | 1981 |

|

SU1007105A1 |

| Квадратор | 1983 |

|

SU1180885A1 |

| Интегро-дифференциальный вычислитель | 1980 |

|

SU960813A1 |

ЦИФРОВОЙ РЕГХДЯТОР по авт.св. 1Г , отличающ и и с я тем, что, с целью расшире 11ия функциональных возможностей, в , него введен нелинейный преобраэова тель,выход которого соединен с вторым входом десятого элемента И, вход . сброса, первый и второй входы синхро ниэации - соответственно с первым, : вторым и шестым выходами блока синхронизации, первый и второй входы управления - соответственно с первыми выходами третьего и четвертого триггеров, п(}ичем первый и второй информационные входы нелинейного преобразователя подключены к соответствующим входам цифрового регулятора.

Авторы

Даты

1983-11-23—Публикация

1982-06-23—Подача