1

Изобретение относится к области вычислительной техники и может применяться в устройствах управления вычислительных машин.

Известны устройства микропрограммирования вычислительных машин, содержаш,ие триггера, дешифратор, собирательные схемы и схемы совпадения.

Однако известные устройства обладают малым быстродействием, вызванным последовательным выполнением микроопераций.

С целью повышения быстродействия в предлагаемое устройство введен («+) дополнительный триггер (где п - целое положительное число), вторые входы / схем «И соединены с выходом первой дополнительной схемы «И, первый вход которой подключен к нулевому выходу (z-f-I)-ro триггера, а второй-к выходу генератора синхроимпульсов, а первые входы дополнительных i схем «И, вторые входы которых соединены соответственно с единичными входами i триггеров, подключены к выходу второй дополнительной схемы «И, первый вход которой соединен с единичным выходом (я-|-1)-го триггера, а второй вход - с выходом генератора синхроимпульсов и с первыми входами п схем «И, вторые входы которых связаны соответственно с единичными выходами п дополнительных триггеров.

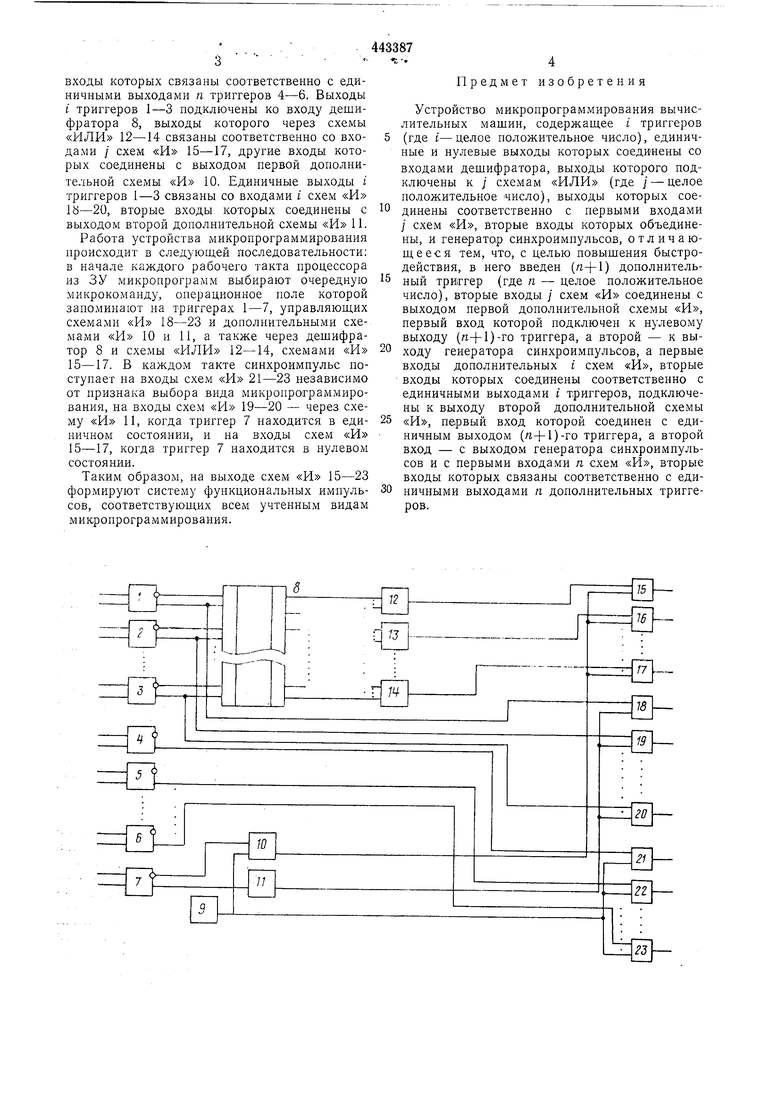

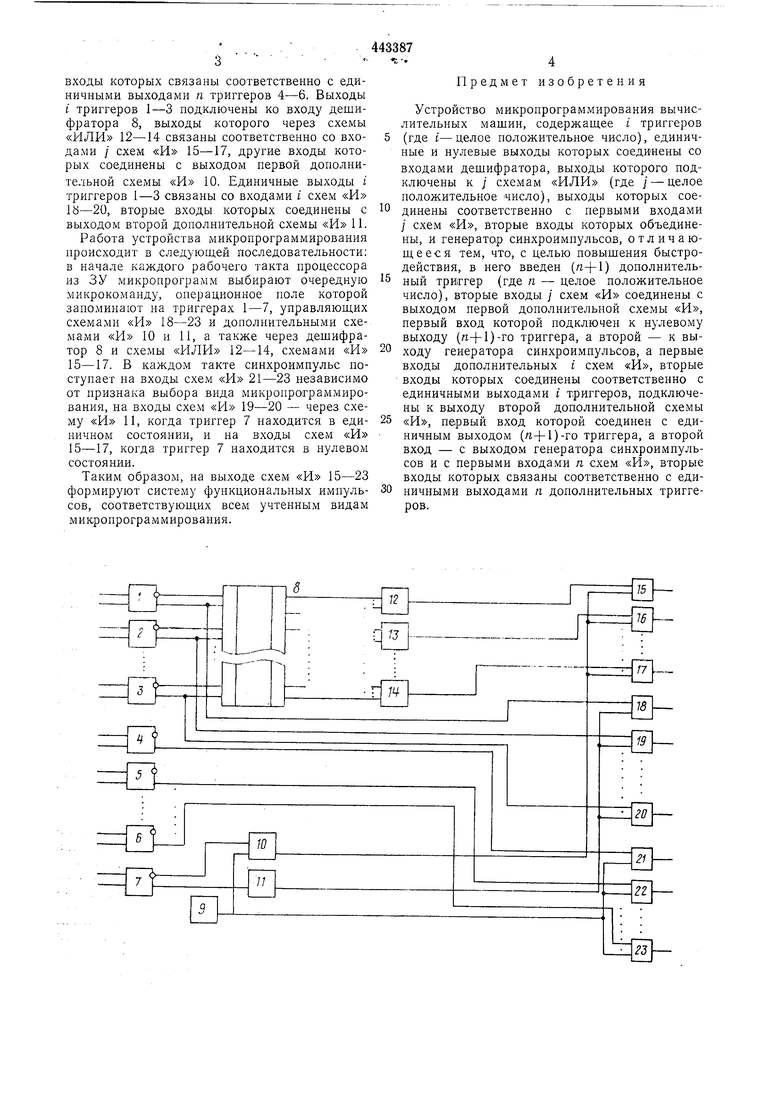

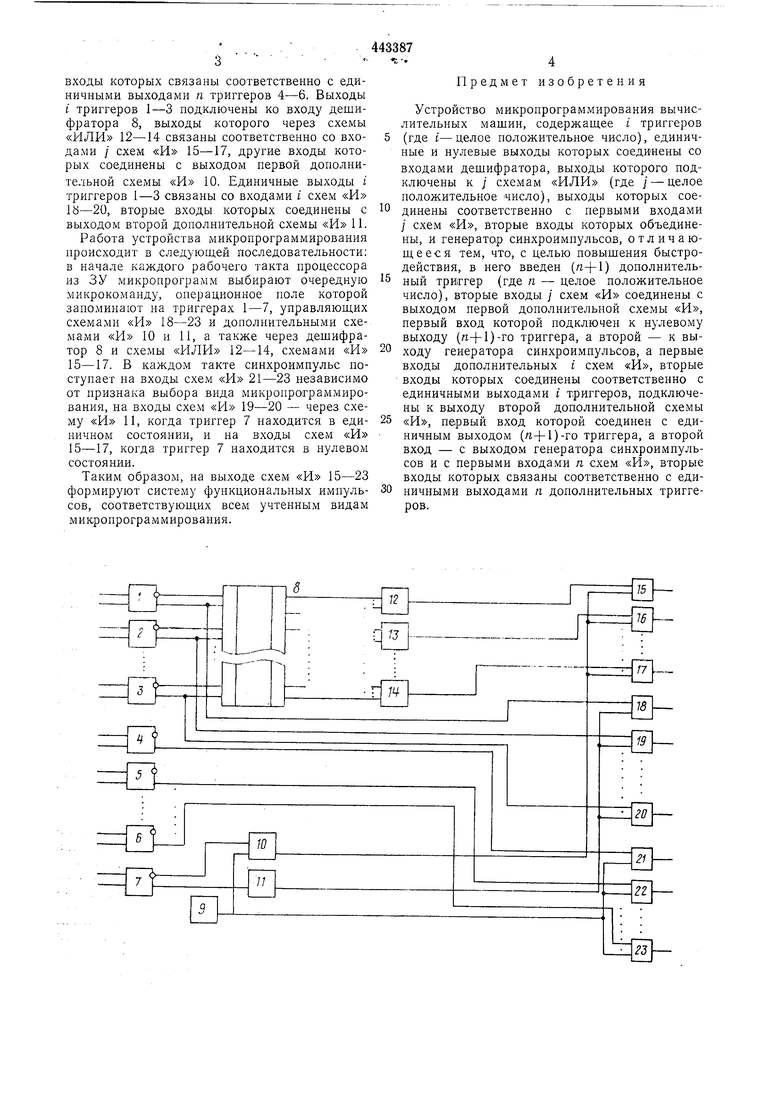

На чертеже представлена схема предлагаемого устройства.

Предлагаемое устройство содержит триггеры 1-3 i части операционного поля, выделенной для перехода с одного (например, горизонтального) на другой (например, вертикальный) вид микропрограммирования, триггеры 4-б (t+ij и (t+O части операционного поля, предназначенной для реализации выбранного неизменного вида микропрограммирования, триггер 7 (1+/г-+-1) для запоминания признака выбора одного из видов микропрограммирования, дешифратор 8 на t входов и 2 выходов, генератор У синхроимпульсов,

первую дополнительную схему «И 1U, вторую дополнительную схему «И И, схемы «ИлИ 12-14, количество / которых определяется набором реализуемых микроопераций при выбранном виде микропрограммирования и схемы «И 1о-1/, 1Ь-2U и 21-26 соответственно в количестве /, i, п, предназначенные для формирования функциональных импульсов.

Ьходы триггеров 1-7 связаны с запоминаюш,ил1 устройством (,ЗУ) для микропрограмм.

Прямой и инверсный выходы (/i-pij-ro дополнительного триггера / соответственно связаны со входами схем «И И и 10, вторые входы которых соединены с генератором 9, образуя блок разделения видов микропрограммирования, и со входами п схем «И 21-23, вторые

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство сортировки чисел | 1986 |

|

SU1441384A1 |

| Устройство для синхронизации | 1981 |

|

SU1012228A1 |

| Устройство для лексического анализа символьного текста | 1984 |

|

SU1187173A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Многоканальная микропрограммная управляющая система | 1985 |

|

SU1280628A1 |

| Устройство для лексического анализа метамикроассемблера | 1982 |

|

SU1034043A1 |

| Устройство для управления цифровой вычислительной машиной | 1974 |

|

SU520591A1 |

| Устройство для сортировки чисел | 1990 |

|

SU1781680A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Вычислительное устройство | 1987 |

|

SU1430962A1 |

Авторы

Даты

1974-09-15—Публикация

1972-01-21—Подача