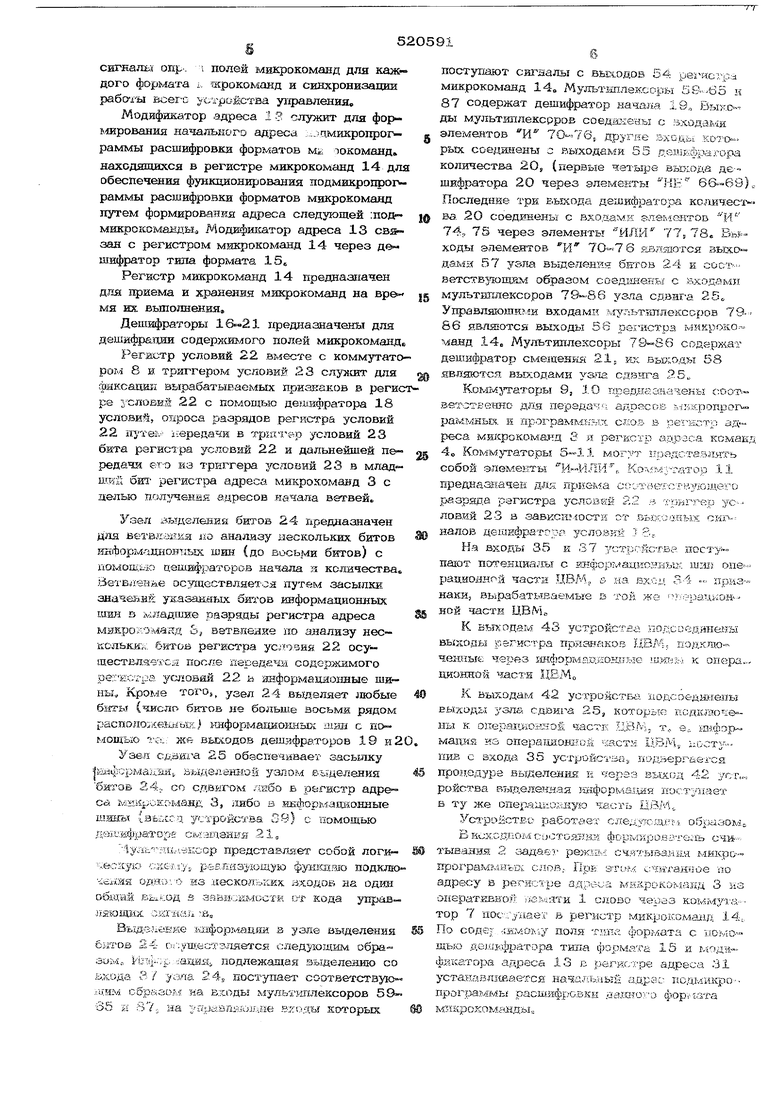

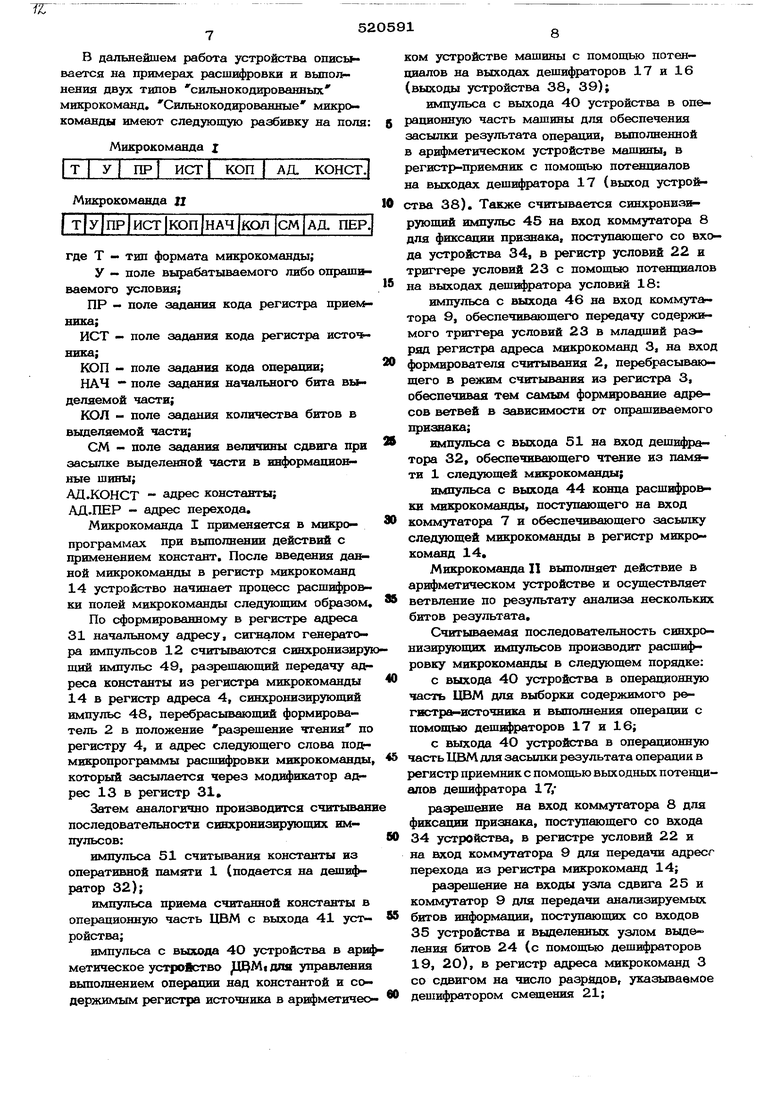

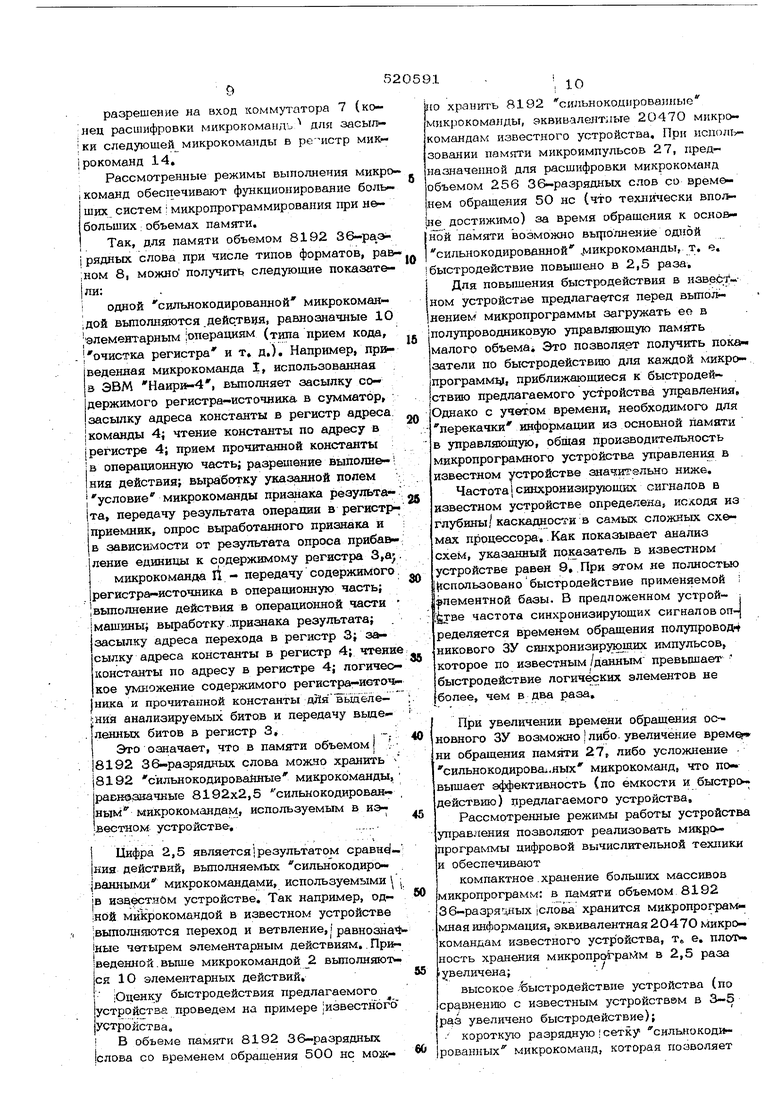

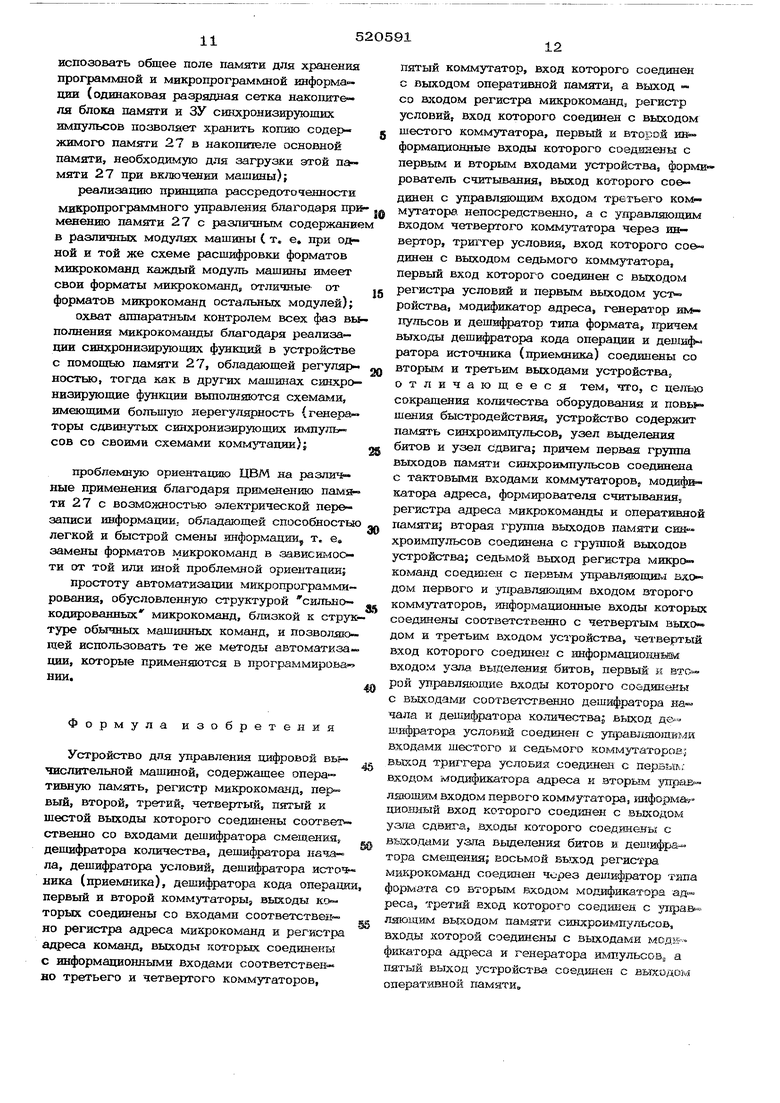

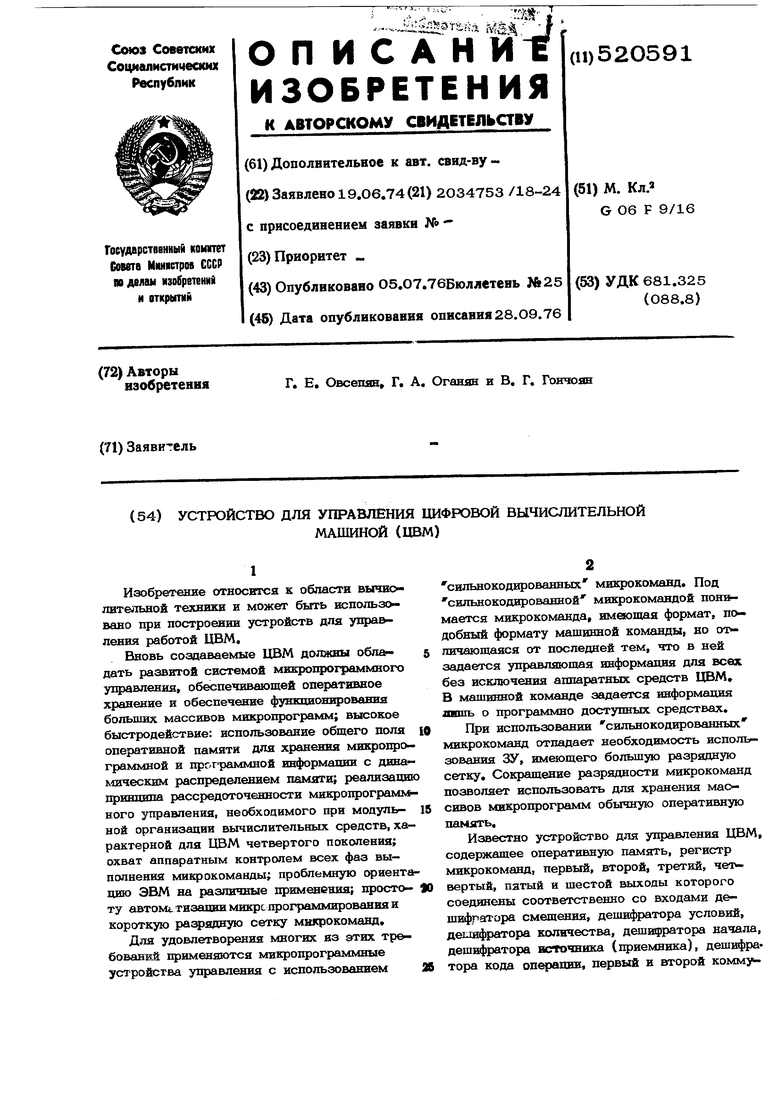

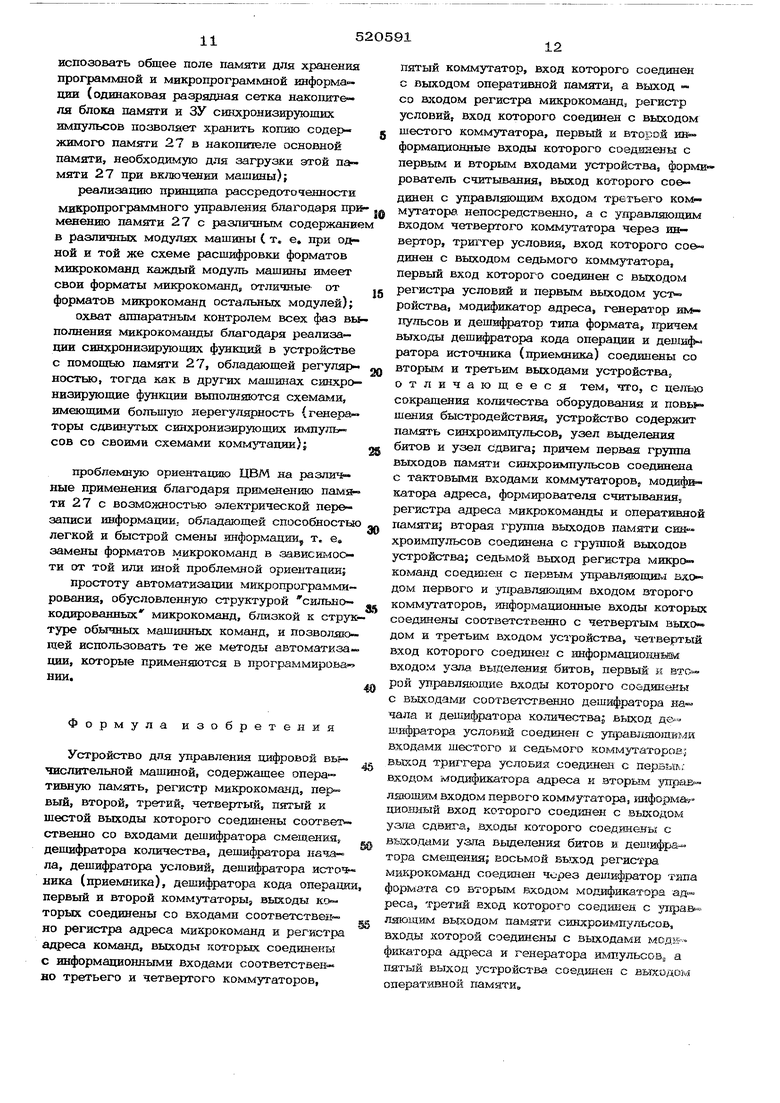

таторы, выходы которых соединены со входами соответственно регистра адреса микрокоманд и регистра адреса команд, выходы которых соединены с информационными входами соответственно третьего и четвертого коммутаторов, нятый коммутатор, вход кото рого соединен с выходом оперативной памяти, а выход - со входом регистра микрокоманд, регистр условий, вход которого соединен с выходом шецтого коммутатора, первый и второй информационные входы Kt торого соединены с первым и вторым вxoдafмн устройства, формирователь считывания, выход которого соединен с управляющим входом третьего коммутатора непосредственно, а с упргшляющим входом четвертого ком мутатора через инвертор, триггер условия, вход которого соединен с выходом седьмого коммутатора, первый вход которого соединен с выходом регистра услобий и первым выходом устройства, модификатор адреса, генератор импульсов и дешифратор типа формата. Выходы дешифратора кода операции и дешифратора источника (преемника) соедвннены с вторым и трютьим выходами устрой Недостатками известного устройства являются повышенные затраты оборудования и малое быстродействие. Цель изобретения - сокращение количества оборудования и повышение быстродействия устройства. Поставленная цель достигается тем, что устройство содержит память синхроимпульсов, узел выделения битов и узел сдвига. Первая группа выходов памяти синхроимпуль сов соединена с тактовыми входами коммутаторов, модификатора адреса, формироват&ля считывания, регистра адреса микрокоманды и оперативной памяти. Вторая группа вы ходов памяти синхроимпульсов соединена с группой выходов устройства. Седьмой выход регистра микрокоманд соединен с первым управляющим входом первого и управляющим входом второго коммутаторов, информацион - ные входы которых соединены соответственно с четвертым выходом и третьим входом устройства, четвертый вход которого соединен с информационным входом узла вьщелени битов, первый и второй управляющие входы которого соединены с выходами соответстве но дешифратора начала и дешифратора колвнчества. Выход дешифратора условий соединен с управляющими входами шестого и седьмого коммутаторов. Выход триггера ус ловия соединен с первым входом модифика тора адреса и вторым управляющим входом первого коммутатора, информационный вход которого соединен с выходом узла сдвига, входы которого соединены с выходами узла вьщеления битов и дешифратора смещения, I восьмой выход регистра микрокоманд соединен через дешифратор типа формата со вторым входом модификатора адреса, третий вход которого соединен с управляющим входом памяти синхроимпульсов, входы которой соединены с выходами модификатора адреса и генератора импульсов, а пятый выход устройства соединен с выходом оперативной памяти. На фиг, 1 представлена блок-схема yci ройства для управления ЦВМ; на фиг, 2- схема узла выделения битов и узла сдвига. Устройство управления ЦВМ содержит оперативную память 1, формирователь считывания 2, регистр адреса микрокоманд 3, регистр адреса команд 4, коммутаторы 5-11, генератор импульсов 12, модификатор адреса 13j регистр микрокоманд 14, дешифратор типа формата 15, дешифратор кода операции 16, дешифратор источника (тфиемника) 17, дешифратор условий 18, дешифратор начала 19, дешифратор количества 2 О, деши4 ратор смещения 21, регистр условий 22, триггер условий 23, узел выделения битов 24, узел сдвига 25, инвертор 26 и память синхроимпульсов 27, На фиг, 1 обозначены: 28, 2 9-накопители, ЗО-31 - регистры адреса, 32, 33 - дешифраторы адреса, 34-37-входы устройства, 38-43- выходы устройства, 44-53 - выхсь. ды памяти синхроимпульсов, 54 - выход регистра микрокоманд, 55 - выход дешифратора количества, 56 - выход регистра микрокоманд, 57 - выход узла выделения битов, 58 - выход узла сдвига. Узлы выделения битов и сдвига содер™ жат мультиплексоры 59-65, элементы НЕ 66-69, элементы И 7О-76, элементы ИЛИ 77, 78 и мультиплексоры 79-86, Оперативная память 1 предназначена для хранения программной и микропрограммной информации. Формирователь считывания 2 предназна- чен для подключения адресного тракта ЦВМ для чтения программных и микропрограммных слов из оперативной памяти 1, Фэрмирователь считывания может быть вьшолнен в виде обычного R5 4.-триггера, Регистры 3 и 4 предназначены соответст венно для приема и хранения адресов микропрограммных и программных слов. Коммутаторы 5 и 6 управляют приемом адресной информации в регистр адреса ЗО оперативной памяти 1, коммутатор 7 - приемом считанной микрокомандной информации в регистр микрокоманд 14, Генератор импульсов 12 вырабатывает тактовые сигналы устройства управления, память синхроимпульсов 27 - тактирующие сигналы опр.- 1 полей микрокоманд для каждого формата i. йфокоманд и синхронизагсии рабо-гы всегС устройства уиравпения. Модификатор адреса 1 3 служит для форьшрования начального адреса :.,..)микропрограммы расшифровки форматов ма оокоманд. находящихся в регистре микрокоманд 14 дл обеспечения функционирования подмикропрограммы расшифровки форматов микрокоманд путем формирования адреса следующей :подмикрокоманды,а Модификатор адреса 13 свэзан с регистром микрокоманд 14 через дешифратор типа формата 15 Регистр микрокоманд 14 предназначен для приема и хранения микрокоманд на вр&мя их вьшолнения. Дешифраторы .21 предназначены для дешифрации содерхсшлого полей микрокоманд Регистр условий 22 вместе с коммутато ром 8 и триггером условий 23 слухшт для фиксацшл вырабатываемых приакаков в реги ре условий 22 с помощью дешифратора 18 условий, онроса разрядов регистра условий 22 путеь нередачи в трнтговр условий 23 бита регис1ра условий 22 и дальнейшей передачи ет-о из триггера условий 23 в младший бЖ1- регист эа адреса микрокоманд 3 с делью пол7;ченйя адресов начала ветвей. Узел выделения битов 24 гфеднааначен для ветвкэ11ия по анализу несколышх битов якфарз,4адионт2ых шин (до восьми битов) с помощью п.ешиф раторов начала и количества Бе1Вй;енйе осуществляется путем засылки значевий указанных информационных Ш2Н в младтиие разрЕЕ.цы регистра адреса мнкро.эмадд о, ветвлелие по алализу несксльк.й1о. битов региствд ус г -эе-ий 22 осуществляется после гшредачи содержимого petHCipa ушювам 22 ь анформаняоашые шины. Кроме того, узел 24 выделяет любые биты (число битов не больше восьми рядом располо хешгЫх.) г-шформадиояньсс ыиш с по- Г:/ющыо .:).: же выходов дешифраторов 19 и 2 Узел cfiBHia 25 обеспечивает засылку |Килф;;рмаиаи Быделенной узлом выделения битов 24;. со- сгвигом якбо в perncip адреса мнк скоманд 3, jiH6o в икформашгонные шж1Ь ( з-гтр&кстаа 39) помощью г;е:11й;фраггоре смзщения 2 ,:и;{,1 агсор представляяет собой логи есгсую . реализующую фуинлаю подклю одна о- КЗ несколышх йходоБ на один общий .вь.сод S за,вн1:л-1мостй сгг кода управ- .кяюздкх GKiiiaj i -в, Вьщсаежке шлформац ш в ;узле выделения бшов 24 рг ущестзляетсЕ следующим образиы, Hj-ai- p -ахщяь подлежащая выделению со ьхода 3 / узла 2 4 поступав соответствую /аим CDpasOjif на в.гсоды муль- иплексоров 59 о5 и 87; на аравпйюлаю входы которых поступают скгвалы с вьЕ10дов 54 регисгра микрокоманд 14„ Мультиплексоры 5S-e5 и 87 содержат дешифратор начала 19„ мультаилексрров соедж.нены с зходами элементов И 70-76, другие входы ко орых соединены о выходами 55 дешифрагора количества 2Os (первые четыре выкода де-шифратора 20 через элементы 6&---69), Последние три выхода дешифратора количества 20 соединены с входами элементов 74, 75 через элементы ИЛИ . Bi-jходы элементов И явлшотся д.зл4-и 57 узота выделения битов 24 Е соот-ветствзгющйм образом соедгы-гены с кходами мультиплексоров 79-86 сдвига 25, Управляюшиг;и входами мульт ;шлек;ссров 79-86 являготся выходы 56 регистра микроко манд. 14, Мультиплексоры 79-86 садерждт дешифратор смещения 21. их 0ьп;оды 58 являются вьгеодами узла сдзига 25 Комыутаторы 9, 10 предяеаначекы -:оотзетственно для перадачч адресов ьзклропроП раммнь. и программных схсов в peis:cTp адреса микрокоманд S и регистр адрэса ксман/д 4в, Коммутаторы 5-11 ъАОгуг- праястезлять собой элемеггты И-ИЛИ с Ко ;м:утатор 11 преднааначен для приег а соо-тйелстуующего разряда регистра условий 22 я 1-ригге1 jc-ловий 23 в завксиг-юсти от вькссны -: о ар-налов дешифратора условий 8,На входы 35 и 37 устройства яосту naioT потенциалы с siH:iioj: ivamiG: iibur. lumi one- рздио юой часзл ЦВМ s на ЕХСД З.с -- приз- наки, вырабатываемые в той же - v- pau;-;ottной части ЦВМ,, К Бъгеодэм 43 устройстга подсаединены ВЫХОДЫ регистра признаков ЦВМ, подключенные через информйдкошгые щиьь.. к операционной части ЦВМ о К выходам 42 устройства подсоединены выходы узла сдвига 2.5, которые поцг;.пюч&пы к onepaiiiiOHHOK части ЦВМ; т., е,. ш фэр-мадия иа операционной iacTM ЦВМ, дюступив с входа 35 устройстааг подвергается проп.еяура Быделен11Я и через выход 42 уст,-, ройства В7зщеяендая гокформал.шя поступает в ту же onepaiiiiOKKyso :асгь ЦВМ., З стройстЕО работает следуЕощгя обтзом В KcxcKGOMcijCTGHKH-i формйровзте гь . тывааия 2 задает pejKinrf счктмва гш микр&... sporpaJvi.iHv,EK с.лоВ; Ггрк счятанкое п.о адресу Б регисЛре адре;;а мнй.рокомзнд 3 из оиератЕВВоя жг,/;дти 1 слово через ког-..мута- тор 7 uoc-;;.)iii3er в регистр микроЕома11.д 14 По соде-;- -tiSviObiy поля тика формата с иомо- шью де.1лгк-фрат 3ра типа формата 15 и модз.- ф жатора адреса 13 в регис-:сре адреса 31 усталавл1шается на гапьнын адрес псдмихфо-. прогр,аммы расшифровки .aa,:&jo::;D фор.гата микрокоманды. В дальнейшем работа устройства описывается на примерах расшифровки и вьшо; нения двух типов сильнокодированных микрокоманд. Сильнокодированные микрокоманды имеют следующую разбивку на поля: Микрокоманда х Т I У t ПР1 ИСТ i КОП i АД. KOHCT.I Микрокоманда П где Т - тип формата микрокоманды; У - поле вырабатываемого либо опрашиваемого условия; ПР - поле задания кода регистра приемника;ИСТ - поле задания кода регистра исто ника;КОП - поле задания кода операции; НАЧ - поле задания начального бита BI деляемой части; КОЛ - поле задания количества битов в выделяемой части; СМ - поле задания величины сдвига при засылке выделенной части в информапион- ные шины; АД.КОНСТ - адрес константы; АД.ПЕР - адрес перехода. Микрокоманда I применяется в микропрограммах при выполнении действий с применением констант. После введения да№ной микрокоманды в регистр микрокоманд 14 устройство начинает пропесс расшифровки полей микрокоманды следующим образом, По сформированному в регистре адреса 31 начальному адресу, сигналом генератора импульсов 12 считываются синхронизиру щий импульс 49, разрешающий передачу ад реса константы из регистра микрокоманды 14 в регистр адреса 4, синхронизирующий импульс 48, перебрасывающий формирователь 2 в положение разрешение чтения по регистру 4, и адрес следующего слова noftмикропрограммы расшифровки микрокоманды который засылается через модификатор адрес 13 в регистр 31, Затем аналогично производится считыван последовательности синхронизирующих импульсов:импульса 51 считывания константы из оперативной памяти 1 (подается на дешифратор 32); импульса приема считанной константы в операпионную часть ЦВМ с выхода 41 уст ройства;импульса с вьсшда 4О устройства в ари метическое устройство ДЭМ| для управления выполнением операции над константой и содержимым регистра источника в арифметичео ом устройстве машины с помощью потениалов на выходах дешифраторов 17 и 16 (выходы устройства 38, 39); импульса с выхода 4О устройства в оп&ационную часть машины для обеспечения засылки результата операшш, выполненной арифметическом устройстве машины, в егистрн-приемник с помощью потенциалов а выходах дешифратора 17 (выход устрой тва 38), Также считывается синхронизирующий импульс 45 на вход коммутатора 8 для фиксации признака, поступающего со входа устройства 34, в регистр условий 22 и триггере условий 23 с помощью потенциалов на выходах дешвфратора условий 18: импульса с выхода 46 на вход коммутатора 9, обеспечивающего передачу содержимого триггера условий 23 в младший разряд регистра адреса микрокоманд 3, на вход формирователя считывания 2, перебрасывающего в режим считывания из регистра 3, обеспечивая тем самым формирование адр&сов ветвей в зависимости от опрашиваемого признака; импульса с выхода 51 на вход дешифратора 32, обеспечивающего чтение из 1 следующей мнкрокомазады; импульса с выхода 44 конца расшифро&ки микрокоманды, поступающего на вход коммутатора 7 и обеспечивающего засылку следующей микрокоманды в регистр микрокоманд 14. Микрокоманда II выполняет действие в арифметическом устройстве и осуществляет ветвление по результату анализа нескольких битов результата. Считываемая последовательность синхронизирующих импульсов производит расши4 ровку микрокоманды в следующем порядке: с выхода 4О устройства в операционную часть ЦВМ для выборки содержимого регшугра-источника и выполнения операции с помощью дещвфраторов 17 и 16; с выхода 40 устройства в операционную часть ЦВМ для засылки результата операции в регистр приемник с помощью выходных потенциалов дешифратора 17, раарешевяе на вход коммутатора 8 для фиксации признака, поступающего со входа 34устройства, в регистре условий 22 и на вход коммутатора 9 для передачи адресг перехода из регистра микрокоманд 14; разрешение на входы узла сдвига 25 и коммутатор 9 для передачи анализируемых битов информации, поступающих со входов 35устройства и выделенных узлом выделения битов 24 (с помощью дешифраторов 19, 20), в регистр адреса микрокоманд 3 со сдвигом на число разрядов, указываемое дешифратором смещения 21; разрешение на вход коммутатора 7 (конец расшифровки микрокомандь для заеыл- I ки следующей микрокоманды в мик1рокоманд 14, Рассмотренные режимы выпол 1ения микро i команд обеспечивают функционирование больших систем ; микропрограммирования при небольших : объемах памяти. Так, для памяти объемом 8192 36-ра,эi рядных слова при числе типов форматов, ра& ;ном 8, можно получить следующие показате- i ли; одной сильнокодированной микрокоман;дой вьтояняются .действия, равнозначные 10 элементарным ;операциям (типа прием кода, очистка регистра и т, д.). Например, прЕНведенная микрокоманда I, использованная 3 ЭВМ HaHpftHti выполняет засылку содержимого регистра-источника в сумматор, засылку адреса константы в регистр адреса, j команды 4; чтение константы по адресу в регистре 4; прием прочитанной константы в операционную часть} разрешение выполне- ВИЯ действия; выработку указанной полем jусловие микрокоманды признака реаульта |та, передачу результата операпии в регистрприемник, опрос выработанного признака и в зависимости от результата опроса прибав- ление единицы к содержимому регистра 3,aj микрокоманда П - передачу содержимого регистра-источника в операционную часть; 1 выполнение действия в операционной части I машины; выработку .признака результата; засылку адреса перехода в регистр 3; з сылку адреса константы в регистр 4; чтение константы по адресу в регистре 4; логическое умножение содержимого регистра-источника и прочитанной константы ел е|;ния анализируемых битов и передачу выделенных битов в регистр 3 Это означает, что в памяти объемом 8192 36-разрядных слова можно хранить J8192 сильнокодировайные микрокоманды, раЕказвачные 8192x2,5 сильнокодирован- , ным микрокомандам, используемым в иэвестаом устройстве. Цифра 2,5 является 1 результатом сравне(- ния действий, вьтолняемых сильнокодиро- (ваннымк микрокомандами, используемыми , jB известном устройстве. Так например, микрокомандой в известном устройстве выполняются переход и ветвление, i равнозна |ные четырем элементарным действиям.. Пр№|веденной. въпде микрокомандой 2 выполняют- |ся 10 элементарных действий. 1. Юценку быстродействия предлагаемого устройства проведем на примере ;известнЪг6 устройства, В объеме памяти 8192 36-разрядных Ьлова со временем обращения 500 не мож.jjto хравт-ь 8192 сильнокодированные микрокоманды, эквивалелтлые 20470 микро{командам известного устройства. При исполт зовании памяти микроимпульсов 27, предназначенной для расшифровки микрокоманд объемом 256 36-разрядных слов со временем обращения 50 не (что техшгаески впо/ь1не достижимо) за время обращения к осно&ной памяти возможно выполнение одной сильнокодированной .микрокоманды, т, е, быстродействие повышено в 2,5 раза. Для повышения быстродействия в извес; -ном устройстве предлагается перед вьшолнением микропрограммы загружать ее в полупроводниковую управляющую память малого объема Это позволяет получить пока«« затели по быстродействию для каждой микропрограмму, приближающиеся к быстродействию предлагаемого устройства управления. Однако с учетом времени, необходимого для перекачки информации из основной памяти в управляющую, общая производительность микропрограмного устройства управления в известном устройстве значительно ниже. Частотасинхронизирующих сигналов в известном устройстве определена, исходя из глубины/каскадности в самых сложных схемах процессора,. Как показывает анализ схем, указанный показатель в известном устройстве равен 9, При этом не полностью (использовано быстродействие применяемой ; пементной базы. В предложенном устрой- ; ве частота синхронизирующих сигналов определяется временем обращения полупровод4 никового ЗУ синхронизир5тощих импульсов, которое по известным /данным превьш1ает быстродействие логических элементов не более, чем в два раза. При увеличении времени обращения осовного ЗУ возможно либо, увеличение времег и обращения памяти 27, либо усложнение сильнокодироваа.ных микрокоманд, что по- ышает эффективность (по емкости и быстроействию) предлагаемого устройства. Рассмотренные режимы работы устройства правления позволяют реализовать микророграьгмы цифровой вычислительной техпикл обеспечивают компактное . хранение больших массивов икропрограмм: в памяти объемом 8192 б-разря ных |слова хранится микропрограмная информация, эквивалентная 2047О микроомандам известного устройства, т е, плотость хранения микропрограмм в 2,5 раза увеличена; . высокое .быстродействие устройства (по равнению с известным устройствам в 3-5 аз увеличено быстродействие); . короткую разрядную сетку силыгокод ованных микрокоманд, которая позволяет испозовать общее поле памяти для хранения программной и микропрограммной информации (одинаковая разрядная сетка накопителя блока памяти и ЗУ синхронизирующих импульсов позволяет хранить копию содержимого памяти 27 в накопителе основной памяти, необходимую для загрузки этой памяти 27 при включении машины); реализашпо принципа рассредоточенности микропрограммного управления благодаря при менению памяти 27 с paзлнчньпvI содержание в различных модулях машины ( т. е, при одной и той же схеме расшифровки форматов микрокоманд каждый модуль машины имеет свои форматы микрокоманд, отличные от форматов микрокоманд остальных модулей); охват аппаратньпу контролем всех фаз вы полнения микрокоманды благодаря реализации синхронизирующих функций в устройстве с помощью памяти 27, обладающей регулярм ностью, тогда как в других машинах синхронизирующие функции выполняются схемами, имеющими большую нерегулярность (генераторы сдвинутых синхронизирующих импульсов со своими схемами комм5тации)| проблемную ориентацию ЦВМ на различные применения благодаря применению памяти 27 с возможностью электрической перезаписи информации, обладающей способностью легкой и быстрой смены информации т, е замены форматов микрокоманд в зависимооти от той или иной проблемной ориентации; простоту автоматизации MHKponporpaMiviH- рования, обусловленную структурой сильнокодированньзх микрокоманд, близкой к струк туре обычных машинных команд, и позволяющей использовать те же методы автоматизации, которые применяются в программировав Формула изобретения Устройство для управления цифровой Бьг- числительной машиной, содержащее опера тивную память, регистр микрокоманд, первый, второй, третий, четвертый, пяггый и шестой выходы которого соединены соответ - ственно со входами дешифратора смешения дешифратора количества, дешифратора начала, дешифратора условий, дешифратора истоФника (приемника), дешифратора кода операци первый и второй коммутаторы, выходы которых соединены со входами соответствен- но регистра адреса микрокоманд и регистра адреса команд, выходы которых с информационными входами соответствен- но третьего и четвертого коммутаторов. пятый коммутатор, вход которого соединен с выходом оперативной памяти, а выход со входом регистра микрокоманд,, регистр условий, вход которого соединен с выходом шестого коммутатора, первый и второй информационные входы которого соединены с первым и вторым входами устройства, формирователь считывания, выход к&горого соединен с управляющим входом третьего кок мутаторе. непосредственно, а с управляющим Входом четвертого коммутатора через инвертор, триггер условия, вход которого соединен с выходом седьмого коммутат-ора, первый вход которого соединен с выходом регистра условий и первым выходом устройства, модификатор адреса, генератор импульсов и дешифратор типа формата, причем выходы дешифратора кода операции и дешиф- ратора источника (приемника) соединены со вторым и третьим выходами устройства, отличающееся тем, что, с целью сокращения количества оборудований и повь шения быстродействия, устройство содержит память синхроимпульсов, узел выделения битов и узел сдвига; причем первая группа выходов памяти синхроимпульсов соединена с тактовыми входами коммутатороВа модификатора адреса, формирователя считывания, регистра адреса микрокоманды и оперативной памяти; вторая группа выходов памяти синхроимпульсов соединена с группой выходов устройства; седьмой выход регистра микрокоманд соединен с первым управл5шэщнм входом первого и .управляющим входом второго коммутаторов, информационные входы которых соединены соответственно с четвертым выходом и третьим входом устройства, четвертый вход которого соединен с информационным входом узла выделения битов, первый и втс™ рой управляющие входы которого соединены с выходами соотвеахггвенно дешифратора на- чала и дешифратора количества выход де- шифратора условий соединен с утфавлшощвмя входами шестого и седьмого коммутаторов; вьхкод триггера условия соединен с первьт; входом модификатора адреса и вторым управ ляюшка-к входом первого коммутатора, информа вход которого соединен с выходом узла сдвига, входы которого соединены с выходами узла вьзделения битов и дешифратора смещения; восьмой вьжод регистра микрокоманд соединен через дешифратор типа формата со вторым входом модификатора ад реса, третий вход которого соедикен с 1Тфа&--. ляющим вь5ходом памяти синхроимпульсов, входы которой соединены с выходами модкгфккатора адреса и генератора иь-шульсов,, а пятый выход устройства с вь гя:одом олерат:ивной памяти М .

49

uz.i fl

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения вычислительной машины с внешними устройствами | 1981 |

|

SU1013939A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

| Устройство для сопряжения ЦВМ с накопителями на магнитной ленте | 1985 |

|

SU1288708A1 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

| Устройство для обработки данных | 1978 |

|

SU736106A1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559341A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559340A1 |

| Адаптер канал - канал | 1988 |

|

SU1608677A2 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

Авторы

Даты

1976-07-05—Публикация

1974-06-19—Подача