г, -

В

Ь

I i 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Многоуровневое устройство для коммутации процессоров в многопроцессорной вычислительной системе | 1984 |

|

SU1187174A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Процессор | 1984 |

|

SU1246108A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1649540A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1264172A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

1

Изобретение относится к вычислительной технике и может быть использовано в универсальных и специализированных вычислительных илашинах (ЦВМ), ;

Современные цифровые вычислительные машины и системы состоят из большого количества асинхронно работающих устройств, обрабатывакщих, хранящих или передающих информацию, ,Общее управление .такой системой осуществляется обрабатывающим устрой;ством, работающим по программе, В целях получения оптимального соотношения между производительностью и стоимостью для малых и средних систем оказывается предпочтительным использование ресурсов обрабатывающего устройства Iт.е.регистров сумматора и т.п.) для выполнения некоторых функций устройств, передающих информацию (устройств ввода-вывода). Специфика организации взаимодействия между обрабатываю1ЩМИ устройствами и автоношо ра-

ботащей аппаратурой устройств ввода-вывод (называемой, в дальнейшем, блоками ввода-вывода) заключается в том, что обрабатывающее устройство и блоки ввода-вывода ра-. оотают асинхронно по отношению друг к другу. Кроме того, в большинстве обрабатывающих устройств современных ЭВМ используется микропрограммное управление, причем за один цикл работы устройства совмещается выполнение текущей микрокоманды и выборка из памяти следующей микрокоманды. Дальнейшее усложнее взаимодействия имеет место в случае наличия в составе обрабатывающего устройства регистров и триггеров, состояние которых меняет каждый цикл работы такого устройства и июжет быть опрошено бло- ком микропрограммного управления для формирования адреса следующей микрокоманды.

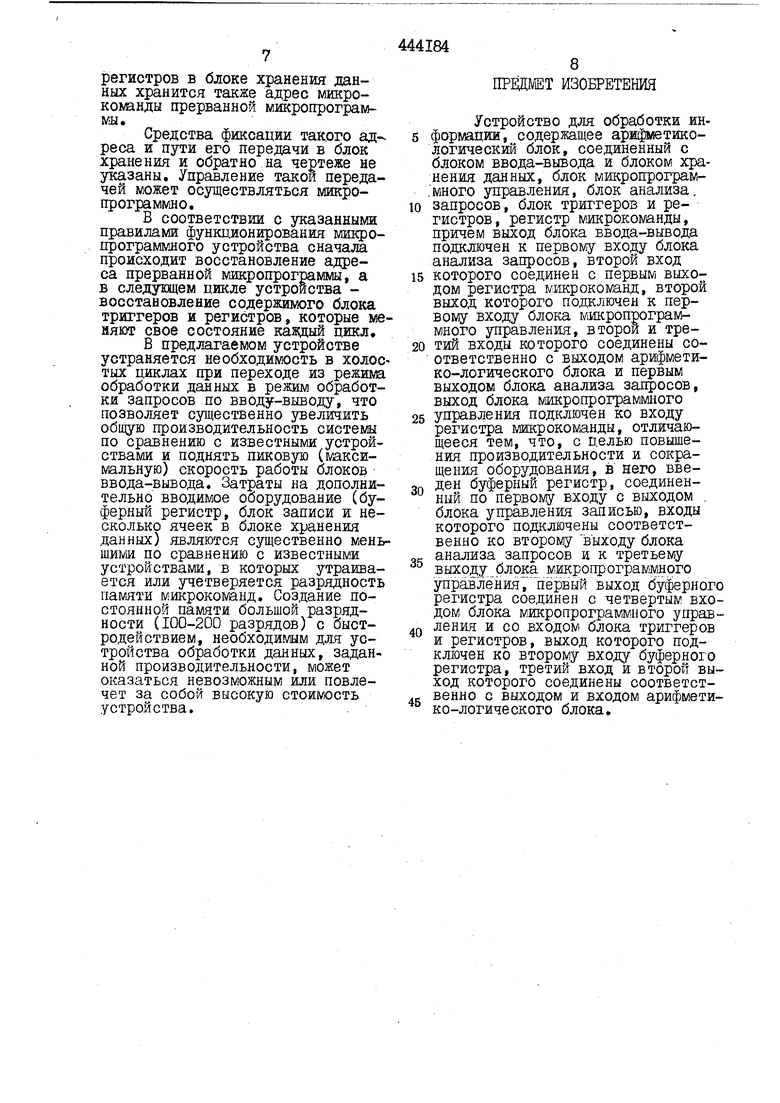

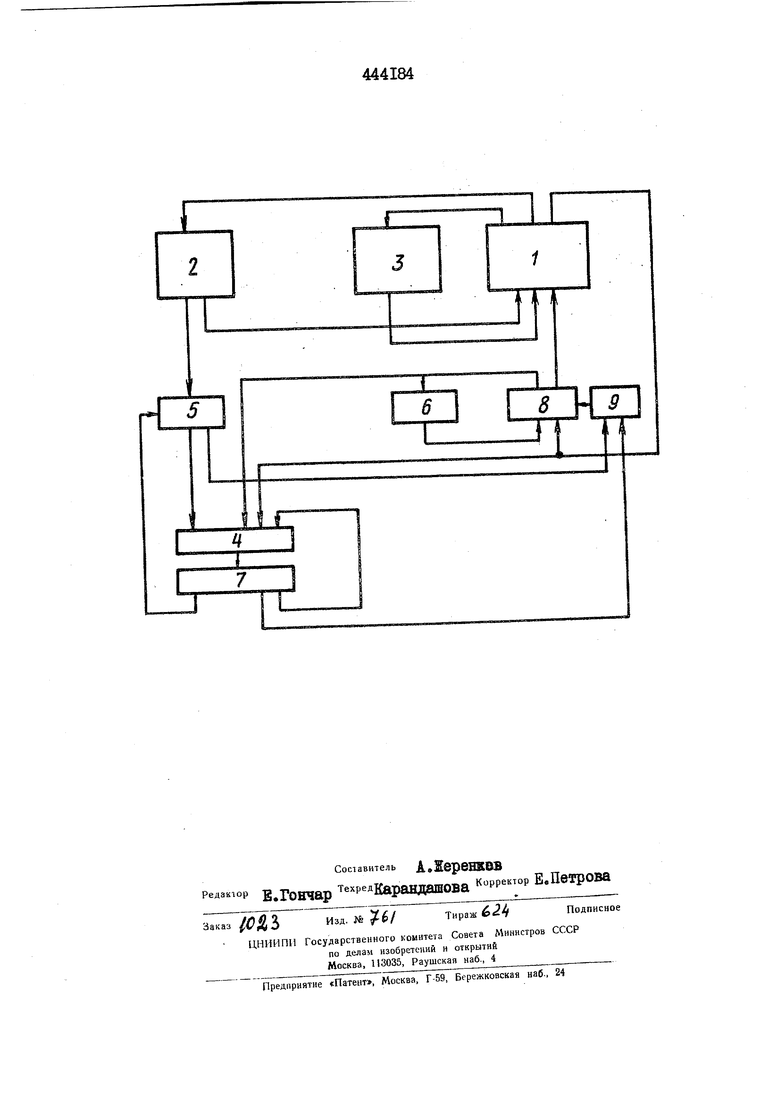

Известна система, в состав которой входят автономные устройства (блоки) ввода-вывода, каждое из которых может oб 1eнивaтьGЯ инфор /ацией с устройством хранения (оперативной памятью) через центральное обрабатывающее устройство, Каждый из блоков ввода-вывода выставляет один или несколько запросов с различным приоритетом, которые анализируются спепиальной аппаратурой обрабатывающего устройства, же .аппаратура осуществляет определение наиболее, приорил тетного запроса и определение момента начала обработки такого приоритета, В соотве тств1Ш с выделениым запросом в обрабатывающем устройстве осуществляется формирование адреса микрокоманды, соответст вующей выделенному запросу, и блокирование приема в регистр микрокоманды инфорг апии из памяти микро команд,, адрес которой был сформиро ван в предыдущем такте работы устройства. При этом в регистр микрокоманды заносится нулевая инфорш,ция во все разряды. Такая микрокоманда не задает никаких действий в устройстве и тем самым осуществляет холостой цикл, в течение которо го специальные схемы запоминают адрес той мшфокоманды, прием которой в регистр микрокоманды был заблокирован, а также содержимое некоторых других регистров, например регистра адреса блока хранения (сверхоперативной памяти), входящего в состав обрабатываадего устройства. Тактовые сигналы в основные блоки устройства в холостом цикле не поступают, Аналогичный холостой такт осу ществляется по окончании выполнен ния микропрограммы обработки запроса от блока ввода-вывода, в течение которого также блокируется додача тактов в основные блоки обрабатывающего устройства и осущест вляется восстановление адреса за-г помненной микрокоманды, а также другой информации, относящейся к прерванной микропрограмме. Наличие холостых тактов при переключении аппаратуры устройства для обработки информации из режима обработки информации в режим обработки запросов ввода-вывода и обратно снижает общую производительность системы, особенно, в случае частых запросов. Как правшю, наиболее часто выполняемые микропрограммы каналов, весьма коротки (4-10 мжроког внд), Кроме того, наличие нулевых комбинаций в кажд{ом поле микрокоманды как . нерабочих (они не..должны вызывать управляющих сигналов в системе) ведет к увеличению разрядности памяти микрокоманды и ее выходного регистра. Известно также микропрограммное обрабатывающее устройство, в котором адрес следующей микрокоманды формируется по результату выполнения текущей. Это позволяет при функционировании устройства не учитывать специфику триггеров и регистров, состояние которых изменяется каждый машинный цикл. Этим устройствам свойственно наличие памяти ммкроколй-нд большой разрядности. Цель изобретения - повышение быстродействия устройства и сокращение оборудования. Предложенное устройство отличается от известных тем, что в него введен буферный регистр, соединенный по первому входу с выходом блока управления записью, входы которого подключены соответственно ко BTOpowry выходу блока анализа и .к третьему выходу блока микропрограммного управления, первый выход буферного регистра соединен с четвертым входом блока микропрограммного управления и с входом блока триггеров и регистров, выход которого подключен к второму входу буферного регистра, третий вход и второй выход которого соединены соответственно с выходом арифметикологического блока. На чертеже изображена схема предложенного устройства для обработки данных. Устройство содержит арифметико-логический блок I, блок 2 ввода-вывода, блок 3 хранения данных, блок 4 микропрограммного управления, блок 5 анализа запросов, блок 6 триггеров и регистров, регистр 7 микрокоманды, буферный регистр 8, блок 9 управления записью. Выход арифметико-логического блока связан с входом блока 2 ввода-вывода и входом блока 3 хранения данных. Выход блока вводавывода подключен к первому входу блока 5 анализа запросов, второй вход которого связан с первым выходом регистра 7 мшcpoкo aнды, второй выход которого подключен к первому входу блока 4 микропрограммного, управления, второй и третий входы которого соединены соответственно с выходом арифметико-логического блока I и первым ВЫХОДОМ Олока анализа запросов. Выход блока микропрограммного управления подключен к входу регистра ыикроколанды, Первш вход буферного регистра 8 соединен с выходом блока 9 управления записью, входы которого подключены соответственно ко второблу выходу блока, анализа запросов и третьему выходу регистра миркокомаиды. Пер вый выход буферного регистра соединен с четвертым входом блока микропрограммного управления и со входом блока триггеров и регистров, выход которого подключен ко второму входу буферного регистра, третий вход и второй выход которо го соединены соответственно со входом и выходом аржЬмети1со-логйческого блока, к другим входамко :торого подключены выходы-блока ввода-вывода и выход блока хранения данных. Работает устройство для обра ботки инфорьш1ии следущим образо Блоки ввода-вывода выставляют запросы на обслуживание в любой момент времени, причем каждый блок может выставить одим из нескольки запросов. Каждый запрос имеет определенный приоритет. Устройство для обработки информации в каждом цикле своей работы анализирует на личие запроса на обслуживание ж выделяет жз них жанболее приоритетный. Эту функцюо выполняет блок анализа запросов, Прж некшто рых своих состояйжях, например в иачале выполнения микропрограммы обработки запроса на обслуживание могут быть замаск1фованы все запросы на обслуживание. Это может быть осуществлено, например, специальным разрядом микрокош-нды, В случае отсутствия указанньк запросов или наличия заш.скйрованных запросов поведения устройства для обработки информации в текущем цикле, а также адрес следующей кшкрококанды задается текущей микрокомандой, выбранной на регистр микрокоманды 7. В случае условного формирования адреса следующей кжсрокоманды опрашиваются состояния регистров и триггеров 6, При наличии незамаскированного запроса (с наибольшим приоритетом) при помощи блока 5 анализа запросов блокируется нормаль ное форм1фование адреса следующей микpoкovaнды по указаниям текущей микрокоманды и формируется адрес микрокоманды, соответствующий запросу. Микрокоманда, выбранная аз памяти на регистр микрокоманд 7, выполняется полностью. По окончаНИИ выполнения текущей микрокоманды блок анализа запросов осуществляет запись состояния регистров и триггеров 6 в буферный регистр 8 при пошщи блока 9 управления записью. В следующем цикле работы устройства для обработки данных будет выполняться первая микроког/анда MMKponporpavMi обработки принятого запроса на обслуживание, дрес второй { микрокоманды определяться предыдущей первой микрокомандой, которая также блокирует работу блока-анализа запросов и блокирует изменение буферного регистра посредством соответствующего управления блоком записи. Блокирование записи в буферный регистр осуществляется до тех пор, пока инфорш.ция, хранящаяся в буферном регистре не перепишется через арифметико-логический блок в блок храненш данных. По окончании этой процедуры очередная выполняемая микрокош.нда, находящаяся в регистре микрокоманды, может снять блокировку работы блока анализа и разрешить тем самым обработку нового запроса на обслуживание. Таким образом управление моментом обработки запросов от блока ввода-вывода осуществляется микропрограммно, причем возможна многоуровневая обработка, когда более приоритетный запрос прерывает микропрограмму обслуживания запроса более низкого пpиo ритета. По окончании выполнения микропрограммы обслуживания запроса информация из соответствушАНХ ячеек блока хранения через арифметико-логический блок передается в буферный регистр, а затем в блок триггеров и регистров. Управление этими передачами осуществляется одной или несколькими микрокомандами, в зависимости от конкретиой структуры устройства для обработки данных. На время передачи инфop йцюi из блока хранения в блок триггеров и регистров м-икрокомандамй, осуществляющий эту передачу,происходит также запрет работы блока анализа запросов. Наряду с информацией о текуг щем состоянии блока триггеров и ,

регистров в блоке хранения данных хранится также адрес микроколанды прерванной микропрограммы,

Средства фиксации такого адреса и пути его передачи в блок хранения и обратно на чертеже не указаны, Управление такой передачей может осуществляться микропрограмшо,

В соответствии с указанными правилами функционирования микропрограммного устройства сначала происходит восстановление адреса прерванной микpoпpoгpa мы, а в следущем цикле устройства восстановление содержимого блока триггеров и регистров, которые меняют свое состояние каждый цикл,

В предлагаемом устройстве устраняется необходимость в холостых циклах при переходе из режима обработки данных в режим обработки запросов по вводу-выводу, что позволяет существенно увеличить общую производительность системы по сравнению с известными устройствами и поднять пиковую (максимальную) скорость работы блоков ввода-вывода. Затраты на дополнительно вводимое оборудование (буферный регистр, блок записи и несколько ячеек в блоке хранения данных) являются существенно меньшим по сравнению с известными устройствами, в которых утраивается или учетверяется разрядность памяти У жрокоманд, Создание постоянной памяти большой разрядности (100-200 разрядов) с быстродействием, необходимым для устройства обработки данных, заданной производительности, может оказаться невозможным или повлечет за собой высокую стоимость устройства.

8

ПРЩМЕТ ИЗОБРЕТЕНИЯ

Устройство для обработки информации, содержащее арифметикологический блок, соединенный с блоком ввода-вывода и блоком хранения данных, блок микропрограм.много управления, блок анализа,

запросов, блок триггеров и регистров, регистр микрокоманды, причем выход блока ввода-вывода подключен к первому входу блока анализа запросов, второй вход

которого соединен с первым выходом регистра микрокоманд, второй выход которого подключен к первому входу блока М1жропрограммного управления, второй и третий входы которого соединены соответственно с выходом арифметико-логического блока и первым выходом блока анализа запросов, выход блока мшtpoпpoгpa мIiOгo

управления подключен ко входу регистра микрокоманды, отличающееся тем, что, с целью повышения производительности и сокращения оборудования, в него введен буферный регистр, соединенный по первому входу с выходом . блока управления записью, входы которого подключены соответственно ко второму выходу блока анализа запросов и к третьег/у

выходу .блока микропрограшшрго управле нйя7 пёрвый выход буферного регистра соединен с четвертым входом блока микропрограммного управления и со входом блока триггеров и регистров, выход которого подключен ко второму входу буферного регистра, третий вход и второй выход которого соединены соответственно с выходом и входом арифметико-логического блока.

rQ

6

Авторы

Даты

1974-09-25—Публикация

1971-08-19—Подача