Изобретение относится к области цифровой вычислительной техники и может быть использовано в электрон- . ньгк нычислительных машинах средней производительности широкого применения.

Цель изобретения - повьшение надежности процессора путем обеспечения контроля выборки и чтения операндов, выполнения команд, записи результата и восстановления вычислительного процесса.

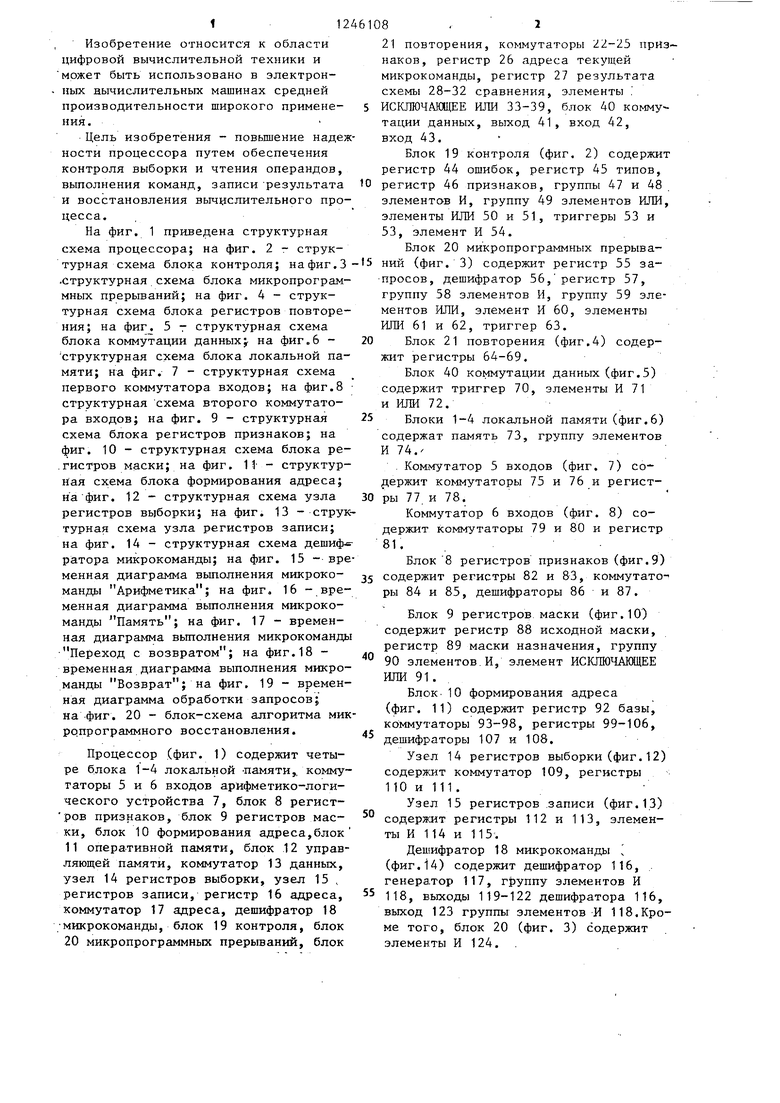

На фиг. 1 приведена структурная схема процессора; на фиг. 2 - струк10

21 повторения, коммутаторы 22-25 при наков, регистр 26 адреса текущей микрокоманды, регистр 27 результата схемы 28-32 сравнения, элементы ИСКЛЮЧАЩЕЕ ИЛИ 33-39, блок 40 комму тации данных, выход 41, вход 42, вход 43.

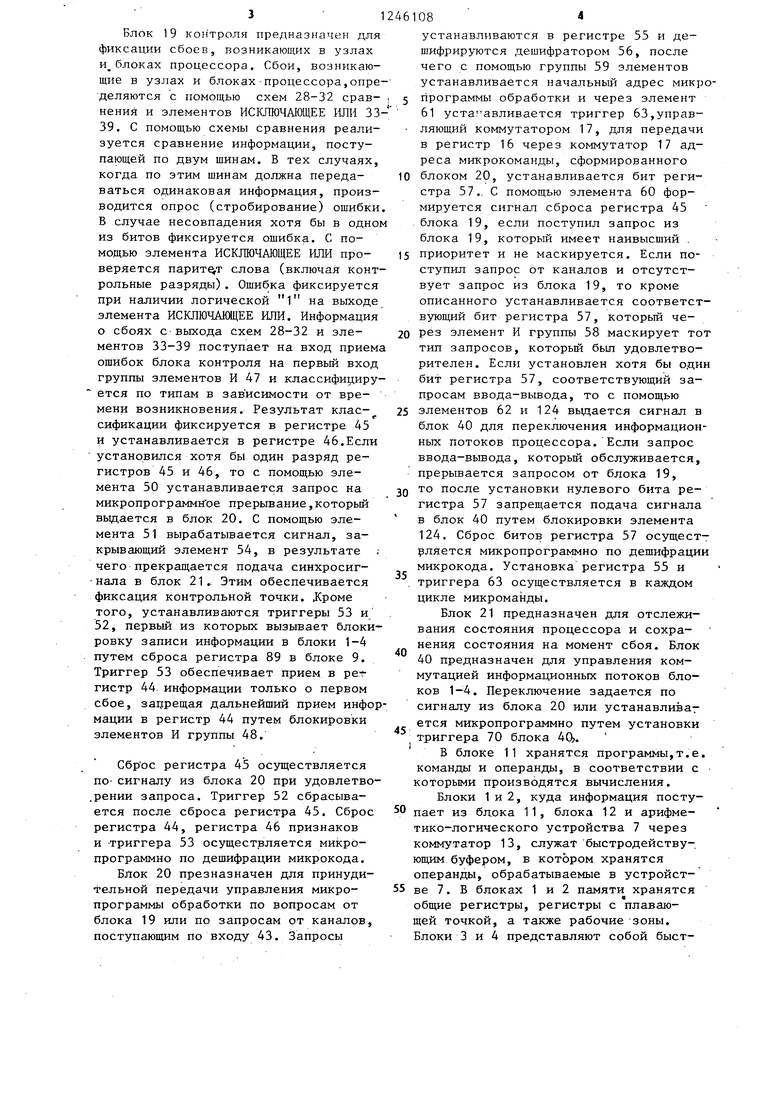

Блок 19 контроля (фиг. 2) содержи регистр 44 ошибок, регистр 45 типов, регистр 46 признаков, группы 47 и 48 элементов И, группу 49 элементов ИЛИ элементы ИЛИ 50 и 51, триггеры 53 и 53, элемент И 54.

Блок 20 микропрограммных прерыватурная схема блока контроля; нафиг.З- - ний (фиг. 3) содержит регистр 55 за- Структурная схема блока микропрограм- -просов, дешифратор 56, регистр 57,

58

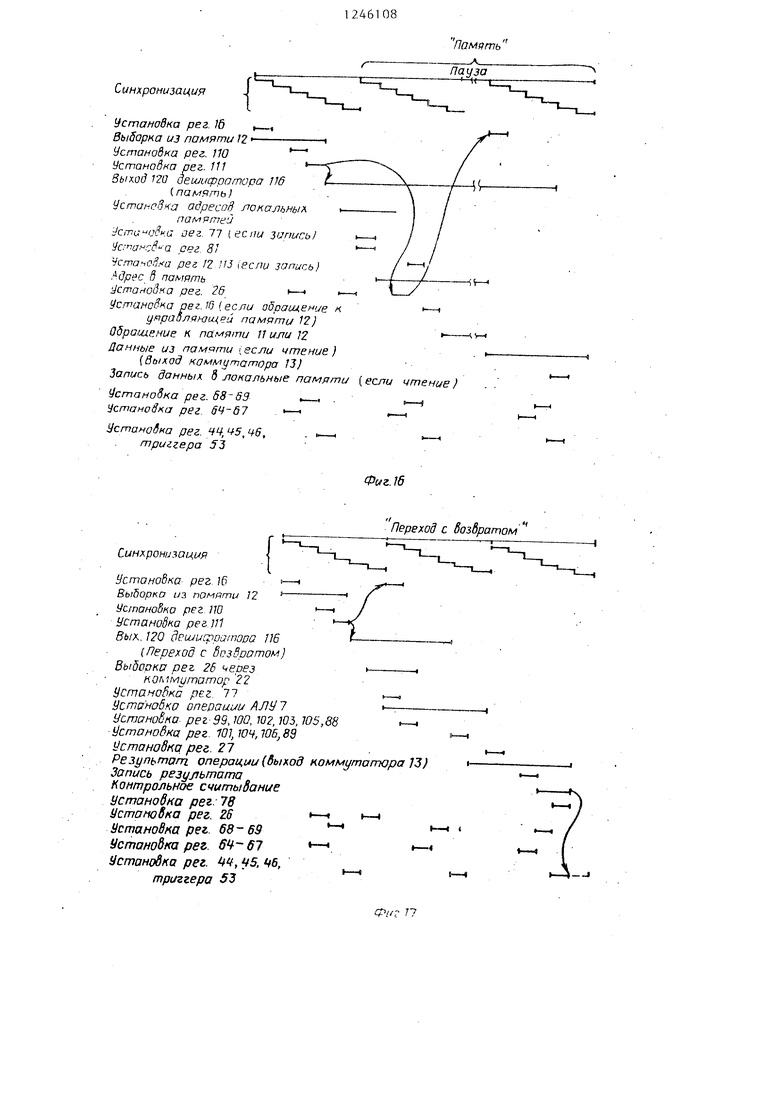

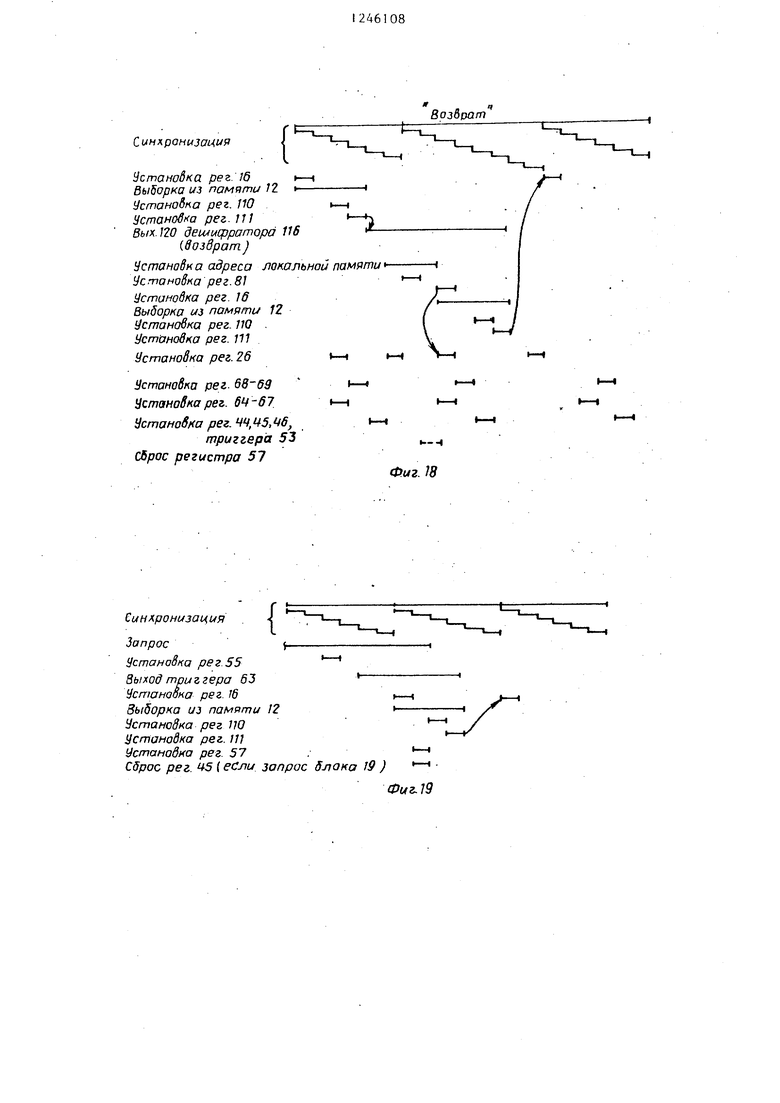

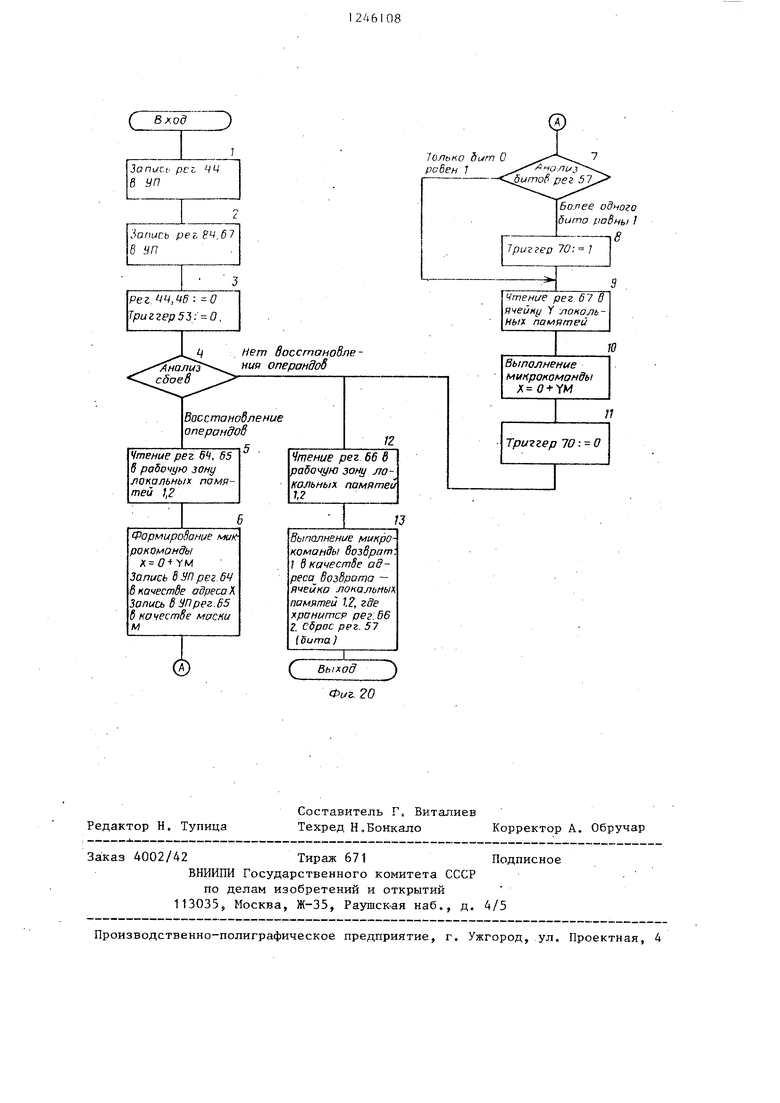

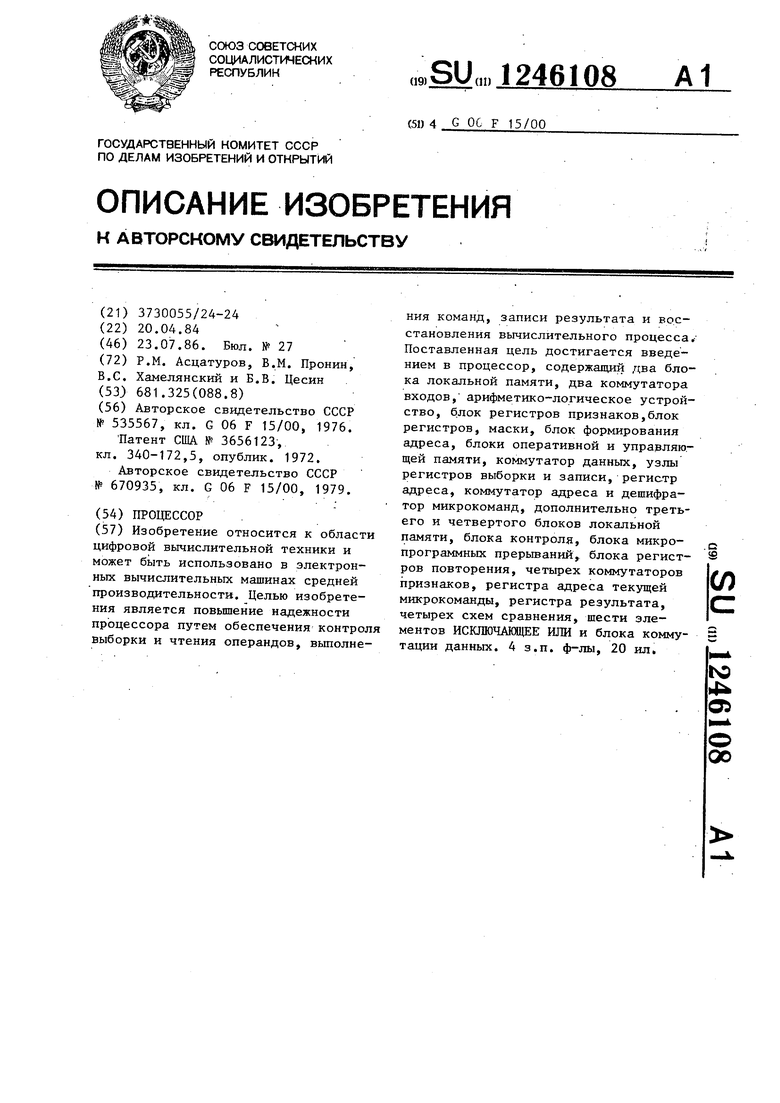

мньпх прерываний; на фиг, 4 - структурная схема блока регистров повторения; на фиг. 5 т структурная схема блока коммутации данных ; на фиг «6 - структурная схема блока локальной памяти; на фиг. 7 - структурная схема первого коммутатора входов; на фиг.8 структурная схема второго коммутатора входов; на фиг. 9 - структурная схема блока регистров признаков; на фиг. 10 - структурная схема блока ре- .гистров маски; на фиг. 11 - структурная схема блока формирования адреса; на фиг. 12 - структурная схема узла регистров выборки; на фиг. 13 - структурная схема узла регистров записи; на фиг. 14 - структурная схема дешиф ратора микрокоманды; на фиг. 15 - временная диаграмма выполнения микрокоманды Арифметика ; на фиг. 16 - временная диаграмма выполнения микрокоманды Память ; на фиг. 17 - временная диаграмма выполнения микрокоманды Переход с возвратом ; на фиг.18 - временная диаграмма выполнения микроманды Возврат ; на фиг. 19 - временная диаграмма обработки запросов; на фиг. 20 - блок-схема алгоритма мик- ponporpetMMHoro восстановления.

Процессор (фиг. 1) содержит четыре блока 1-4 локальной -памяти,, коммутаторы 5 и 6 входов арифметико-логического устройства 7, блок 8 регист ров признаков, блок 9 регистров маски, блок 10 формирования адреса,блок 11 оперативной памяти, блок 12 управляющей памяти, коммутатор 13 данных, узел 14 регистров выборки, узел 15 . регистров записи, регистр 16 адреса, коммутатор 17 адреса, дешифратор 18

микрокоманды, блок 19 контроля, блок 20 микропрограммных прерываний, блок

20

25

30

группу за элементов И, группу 59 эле ментов ИЛИ, элемент И 60, элементы ИЛИ 61 и 62, триггер 63.

Блок 21 повторения (фиг.4) содержит регистры 64-69.

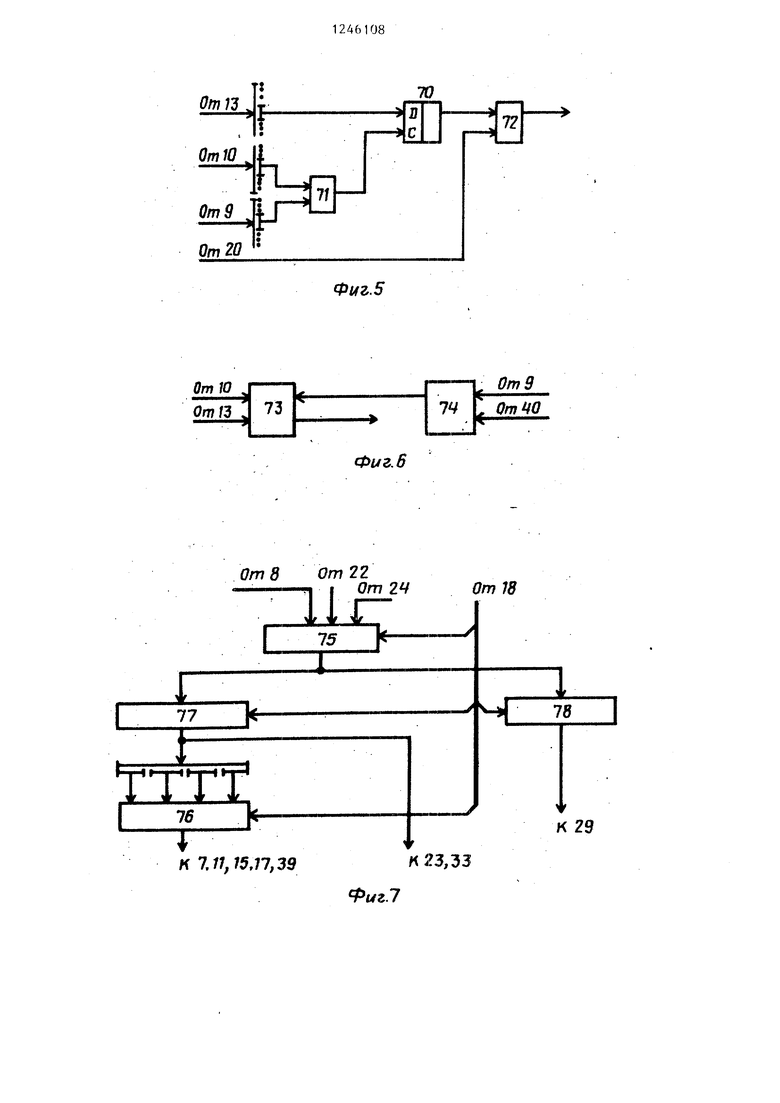

Блок 40 коммутации данных (фиг.5) содержит триггер 70, элементы И 71 и ИЛИ 72.

Блоки 1-4 локальной памяти (фиг.6) содержат память 73, группу элементов И 74.

. Коммутатор 5 входов (фиг. 7) со- ;ержит коммутаторы 75 и 76 и регистры 77 и 78.

Коммутатор 6 входов (фиг. 8) содержит коммутаторы 79 и 80 и регистр 81.

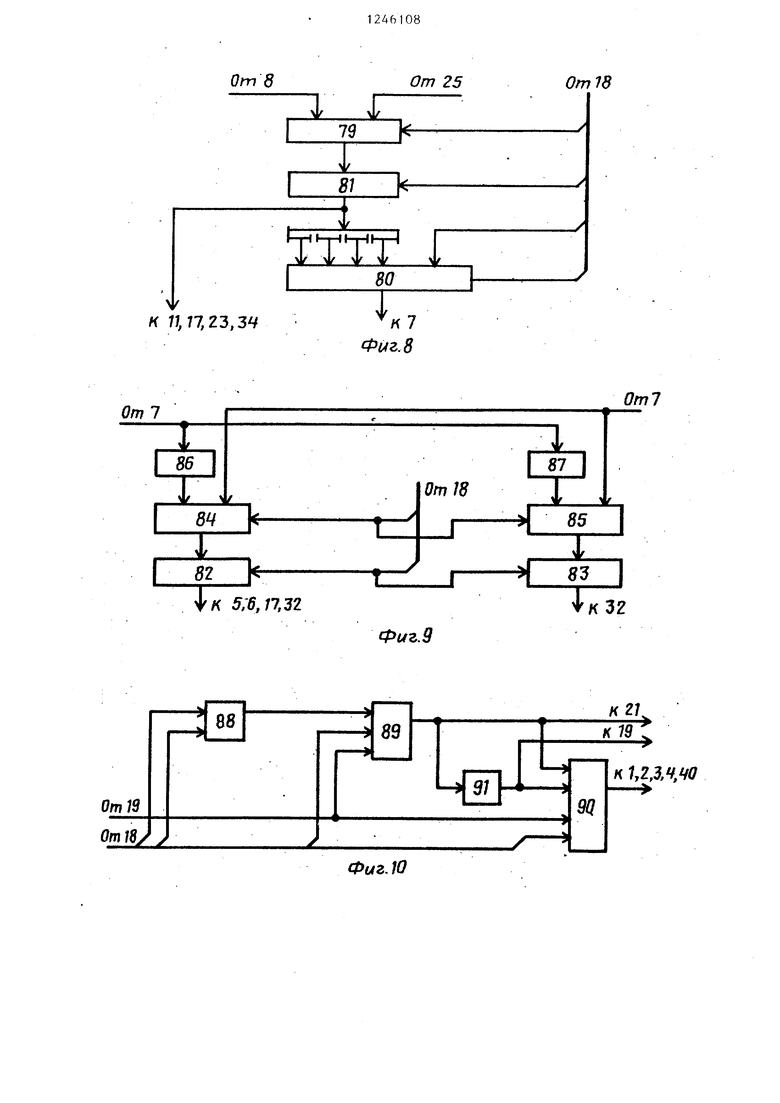

Блок 8 регистров признаков (фиг.9) 35 содержит регистры 82 и 83, коммутато ры 84 и 85, дешифраторы 86 и 87.

Блок 9 регистров маски (фиг.10) содержит регистр 88 исходной маски, регистр 89 маски назначения, группу 90 элементов. И, элемент ИСКПЮ ШОДЕЕ ИЛИ 91.

Блок-10 формирования адреса (фиг. 11) содержит регистр 92 базы, коммутаторы 93-98, регистры 99-106, дешифраторы 107 и 108.

Узел 14 регистров выборки (фиг. 12) содержит коммутатор 109, регистры 110 и 111.

Узел 15 регистров записи (фиг.13) содерлит регистры 112 и 113, элементы И 114 и 115.

Дешифратор 18 микрокоманды (фиг.14) содержит дешифратор 116, генератор 117, группу элементов И 55 118, выходы 119-122 дешифратора 116, выход 123 группы элементов И 118.Кро ме того, блок 20 (фиг. 3) содержит элементы И 124. .

45

50

21 повторения, коммутаторы 22-25 признаков, регистр 26 адреса текущей микрокоманды, регистр 27 результата схемы 28-32 сравнения, элементы ИСКЛЮЧАЩЕЕ ИЛИ 33-39, блок 40 коммутации данных, выход 41, вход 42, вход 43.

Блок 19 контроля (фиг. 2) содержит регистр 44 ошибок, регистр 45 типов, регистр 46 признаков, группы 47 и 48 элементов И, группу 49 элементов ИЛИ, элементы ИЛИ 50 и 51, триггеры 53 и 53, элемент И 54.

Блок 20 микропрограммных прерыва58

группу за элементов И, группу 59 элементов ИЛИ, элемент И 60, элементы ИЛИ 61 и 62, триггер 63.

Блок 21 повторения (фиг.4) содержит регистры 64-69.

Блок 40 коммутации данных (фиг.5) содержит триггер 70, элементы И 71 и ИЛИ 72.

Блоки 1-4 локальной памяти (фиг.6) содержат память 73, группу элементов И 74.

. Коммутатор 5 входов (фиг. 7) со- ;ержит коммутаторы 75 и 76 и регистры 77 и 78.

Коммутатор 6 входов (фиг. 8) содержит коммутаторы 79 и 80 и регистр 81.

Блок 8 регистров признаков (фиг.9) содержит регистры 82 и 83, коммутато- ры 84 и 85, дешифраторы 86 и 87.

Блок 9 регистров маски (фиг.10) содержит регистр 88 исходной маски, регистр 89 маски назначения, группу 90 элементов. И, элемент ИСКПЮ ШОДЕЕ ИЛИ 91.

Блок-10 формирования адреса (фиг. 11) содержит регистр 92 базы, коммутаторы 93-98, регистры 99-106, дешифраторы 107 и 108.

Узел 14 регистров выборки (фиг. 12) содержит коммутатор 109, регистры 110 и 111.

Узел 15 регистров записи (фиг.13) содерлит регистры 112 и 113, элементы И 114 и 115.

Дешифратор 18 микрокоманды (фиг.14) содержит дешифратор 116, генератор 117, группу элементов И 118, выходы 119-122 дешифратора 116, выход 123 группы элементов И 118.Кроме того, блок 20 (фиг. 3) содержит элементы И 124. .

Блок 19 контроля предназначен для фиксации сбоев, возникающих в узлах и блоках процессора. Сбои, возникающие в узлах и блоках-процессора,определяются с помощью схем 28-32 срав- нения и элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 33 39. С помощью схемы сравнения реализуется сравнение информации, поступающей по двум шинам. В тех случаях, когда по этим шинам должна переда- ваться одинаковая информация, производится опрос (стробирование) ошибки В случае несовпадения хотя бы в одно из битов фиксируется ошибка. С помощью элемента ИСКЛЮЧАЮЩЕЕ ИЛИ про- веряется паритет слова (включая контрольные разряды). Ошибка фиксируется при наличии логической 1 на выходе элемента ИСКЛЮЧАЩЕЕ ИЛИ. Информация о сбоях с выхода схем 28-32 и эле- ментов 33-39 поступает на вход прием ошибок блока контроля на первьш вход группы элементов И 47 и классифицируется по типам в зависимости от времени возникновения. Результат клас- сификации фиксируется в регистре 45 и устанавливается в регистре 46.Если установился хотя бы один разряд регистров 45 и 46, то с помощью элемента 50 устанавливается запрос на микропрограммнЪе прерывание,который выдается в блок 20. С помощью элемента 51 вырабатывается сигнал, закрывающий элемент 54, в результате чего прекращается подача синхросиг- нала в блок 21. Этим обеспечивается фиксация контрольной точки. Дроме того, устанавливаются триггеры 53 и 52, первый из которых вызывает блокировку записи информации в блоки 1-4 путем сброса регистра 89 в блоке 9. Триггер 53 обеспечивает прием в per гистр 44. информации только о первом сбое, зацрещая дальнейший прием информации в регистр 44 путем блокировки элементов И группы 48.

Сбр ос регистра 45 осуществляется по- сигналу из блока 20 при удовлетво- .рении запроса. Триггер 52 сбрасывается после сброса регистра 45. Сброс регистра 44, регистра 46 признаков и -триггера 53 осуществляется микропрограммно по дешифрации микрокода.

Блок 20 презназначен для принудительной передачи управления микро- программы обработки по вопросам от блока 19 или по запросам от каналов, поступающим по входу 43. Запросы

5 0 s 0 5

0

5

0

5

0

устанавливаются в регистре 55 и дешифрируются дешифратором 56, после чего с помощью группы 59 элементов устанавливается начальный адрес микропрограммы обработки и через элемент 61 устанавливается триггер 63,управляющий коммутатором 17, для передачи в регистр 16 через коммутатор 17 адреса микрокоманды, сформированного блоком 20, устанавливается бит регистра 57.. С помощью элемента 60 формируется сигна,п сброса регистра 45 блока 19, если поступил запрос из блока 19, который имеет наивысший . приоритет и не маскируется. Если поступил запрос от каналов и отсутствует запрос из блока 19, то кроме описанного устанавливается соответствующий бит регистра 57, который через элемент И группы 58 маскирует тот тип запросов, который был удовлетворителен. Если установлен хотя бы один бит регистра 57, соответствующий запросам ввода-вывода, то с помощью элементов 62 и 124 выдается сигнал в блок 40 для переключения информационных потоков процессора. Если запрос ввода-вывода, который обслуживается, прерывается запросом от блока 19, то после установки нулевого бита регистра 57 запрещается подача сигнала в блок 40 путем блокировки элемента 124. Сброс битов регистра 57 осущест- рляется микропрограммно по дешифрации микрокода. Установка регистра 55 и триггера 63 осуществляется в каждом цикле микроманды.

Блок 21 предназначен для отслеживания состояния процессора и сохранения состояния на момент сбоя. Блок 40 предназначен для управления коммутацией информационньгх потоков блоков 1-4. Переключение задается по сигналу из блока 20 или устанавлива7 ется микропрограммно путем установки триггера 70 блока 4(i.

В блоке 11 хранятся программы,т.е. команды и операнды, в соответствии с которыми производятся вычисления.

Блоки 1 и 2, куда информация поступает из бдока 11, блока 12 и арифметико-логического устройства 7 через коммутатор 13, служат быстродействующим буфером, в котором хранятся операнды, обрабатываемые в устройстве 7. В блоках 1 и 2 памяти хранятся общие регистры, регистры с плавающей точкой, а также рабочие зоны. Блоки 3 и 4 представляют собой быстродействующую память встроенных каналов ввода-вывода и предназначены для хранения управляющей информации устройства, управляющей информации ка- нала и рабочих аон. Селекция информационных потоков блоков 1 и 3, а также 2 и 4 осуществляется с помощью коммутаторов 24 и 25 соответственно под управлением блока 40. Селекция информационных потоков и коммутации байтов, поступающих на первый вход устройства 7, осуществляется с помощью коммутатора 5. Селекция информационных потоков и коммутация бай- тов, поступающих на второй вход устройства 7, осуществляется с помощью коммутатора 6. Кроме того, с помощью коммутатора 6 формируется константа, которая является частью микрокода, и поступает с выхода 20 дешифратора 18 на второй вход коммутатора 80,

Арифметико-логическое устройство 7 разрядностью четыре байта имеет параллельные цепи для выполнения всех заложенных в него арифметических и логических операций. Результат операции запоминается. Кроме того, устройством 7 формируются признаки f результата выполненной операции, на- пример больще О, меньше О, равно О. Результат операции в арифметико логическом устройстве контролируется по паритету элементов 37.

Арифметико-логическое устройство (АЛУ) 7 может быть реализовано последовательным соединением интегральных микросхем. Набор операции устройства 7 реализуется с помощью операций, реализованных на указанных мик- росхемах. Признаки результата операции устройства 7 устанавливаются через дешифраторы 86 и 87 и коммутаторы 84 и 85 в регистрах 82 и 83 блока 8. Аппаратура блока 8 продублирована и контролируется схемой 32.

Блок.10 предназначен для хранения адресов, доступных в данный момент зон блоков 1-4 и регистров блоков 19, 21. и 26, Аппаратура блока для адреса- ции блоков 1-4 продублирована.Контроль адресов блоков 1-4 осуществляется схемами 30 и 31,

Управление процессом осуществляется микропрограммно. По адресу, на- ходящемуся в регистре 16, на блоки 12 считывается несколько микрокоманд, выборка нужной микрокоманды осуществю5 20

25 зо

,„

5

ляется в узле 14. Поля микрокоманды дешифрируются с помощью дешифратора 18. Контроль кода микрокоманды осуществляется по йаритету элементов 36.

В дешифраторе 18 с помощью дешифратора 116 из кода микрокоманды выделяются поля, управляющие адресом следующей микрокоманды (выход 119), устанавливающие потенциальные сигна-. лы (выход 120)-, разрешающие временные сигналы (выход 121) и управляющие генератором 117. С помощью генератора 117 и группы элементов 118 формируются стробирующие сигналы процессора, поступающие с выхода 123 дешифратора 18.

Арифметико-логическое устройство 7 выполняет арифметические операции (сложение и вычитание кодов) и логические операции (И-НЕ, ИЛИ, ИСКЛЮЧАЮЩЕЕ IITM) над операндами, поступаю- ш;ими на его входы. В АЛУ 7 генерируются контрольные разряды результата, а также признаки результата (равен О, или больше О, меньше О, переполнение).

В блоке 12, кроме микропрограмм, хранятся управляющие регистры,области сохранения, области расширенной регистрации. Запись в блок 12 производится по адресу, находящемуся в регистре 16, Записьшаемая информация поступает в блок 12 через узел 15 и контролируется по паритету элементом 39. Чтение данных из блока 12 производится по адресу, находящемуся в регистре 16. Информация, считываемая из блока 12, через узел 14 поступает на коммутатор 13. Выббр адреса обращения к блоку 12 осуществляется коммутатором 17.Информация, считываемая из блока 11, блока 12 и выходу устройства 1, через ко;ммутатор 13 поступает в блоки 1-4, .блок 40 и на выход 4 К ИнфЬр-. мация, читаемая из каналов, поступает по входу 42. Каждый бит информации передается по магистралям процессора вместе с контрольным разрядом. Паритет каждого информационного байта до,пжен быть нечетным.

Процессор работает следующим образом.

Управление всеми функциями процессора осу)чествляется с помощью микро- nporpiSMM. Микрокоманды могут зада7.

вать следующие действия: арифметико- логические операции над байтом и над словом, обращения к оперативной или управляющей памяти, переход с возвратом, возвращает, С помощью микрокоманд реализуется система команд процессора, процедуры каналов ввода- вьшода, а также система восстанов.-; ления.

Процессор имеет следующую струн- туру микрокоманды:

1 а) тип микрокоманды (Арифметика Память, Переход с возвратом, Возврат); (Г) функция микрокоманды

. (например, в микрокоманде Арифметика код операции АЛУ, обработка байта или слова и т.п., в микрокоманде Память - операция чтения или записи, операция с оперативной или управляющей памятью); Ь) поле адреса первого операнда; г) поле адреса г второго операнда или константа. В микроког анде Память адрес первого операнда определяет источник данных (при записи) или место назначения (при чтенич). В микрокоманде Пере- ход с возвратом второй операнд не используется, в микрокоманде Возврат используется как константа (маска сброса регистра 57 блока 20); с) поле адреса следующей микрокоманды; е) функция переходов (безусловный

переход, переход по признаку, перехо по анализу байта данных).

Группа выходов 119 дешифратора 11

определяется полем е микрокоманды и поступает на управляющий вход коммутатора 17. Содержимое поля « микрокоманды поступает на вход коммутатора 17.

Группа 120 и 121 дешифратора 116 определяется полями а -е микрокоманды.

Группа выходов 122 дещифратора.116 определяется полем микрокоманды.

Выполнение каждой микрокоманды осуществляется за два цикла синхронизации процессора.

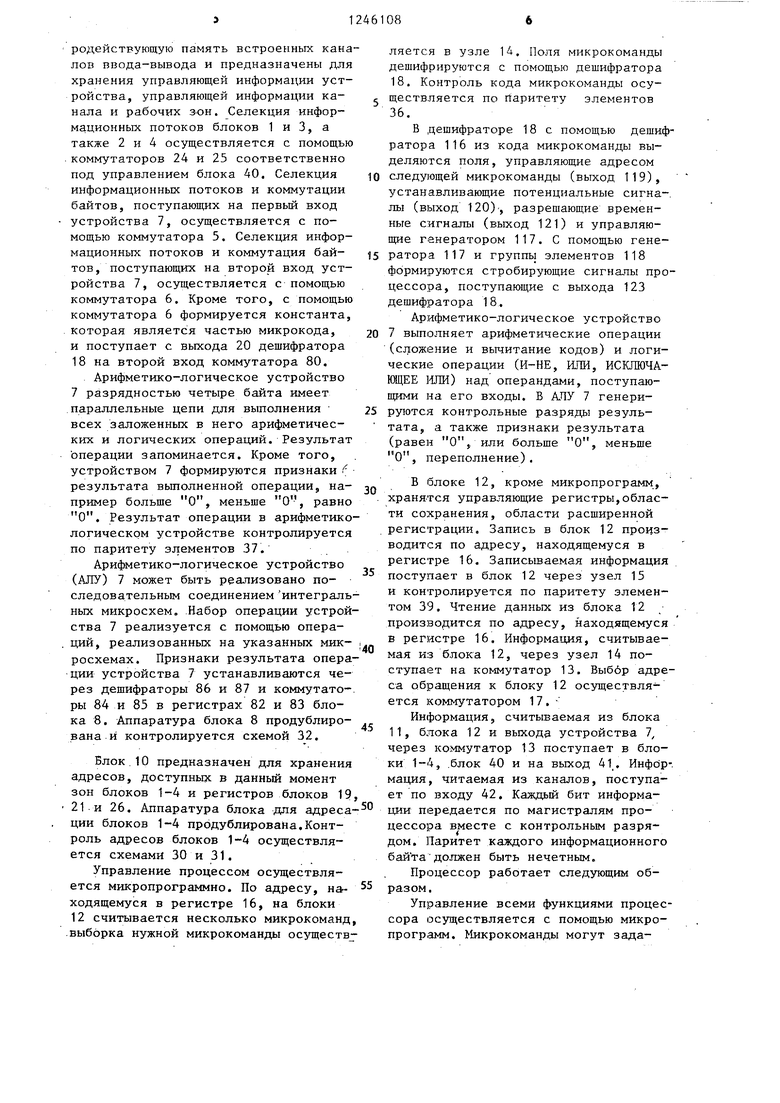

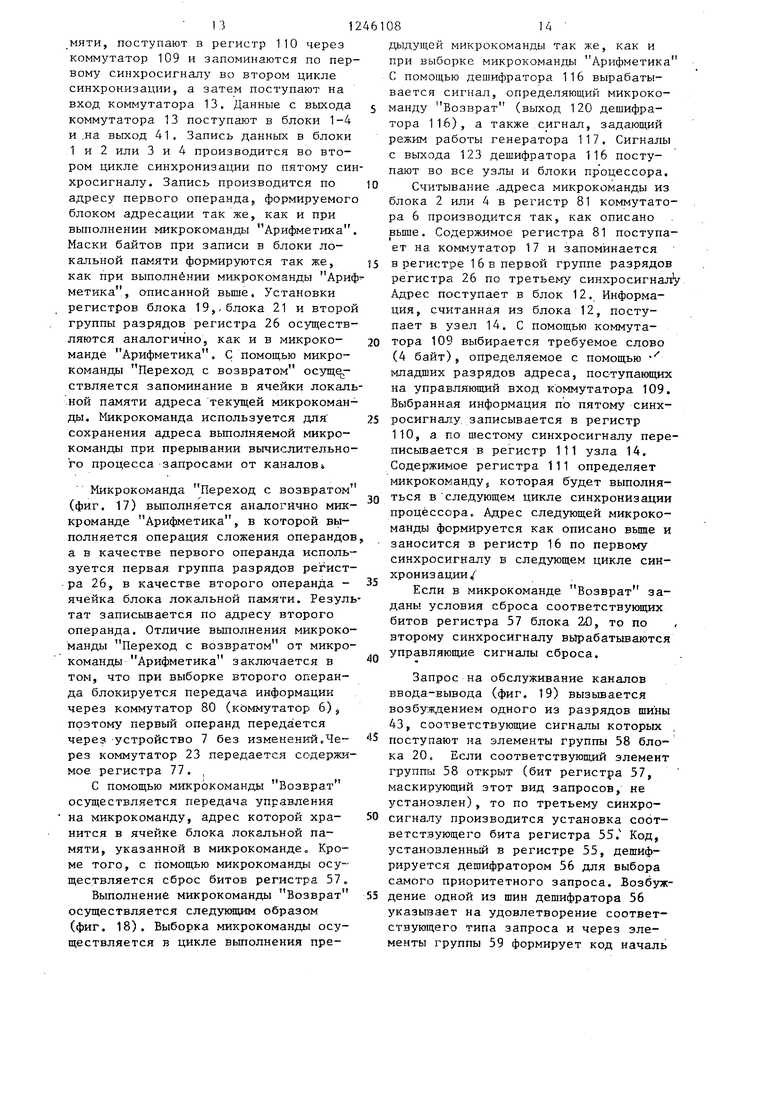

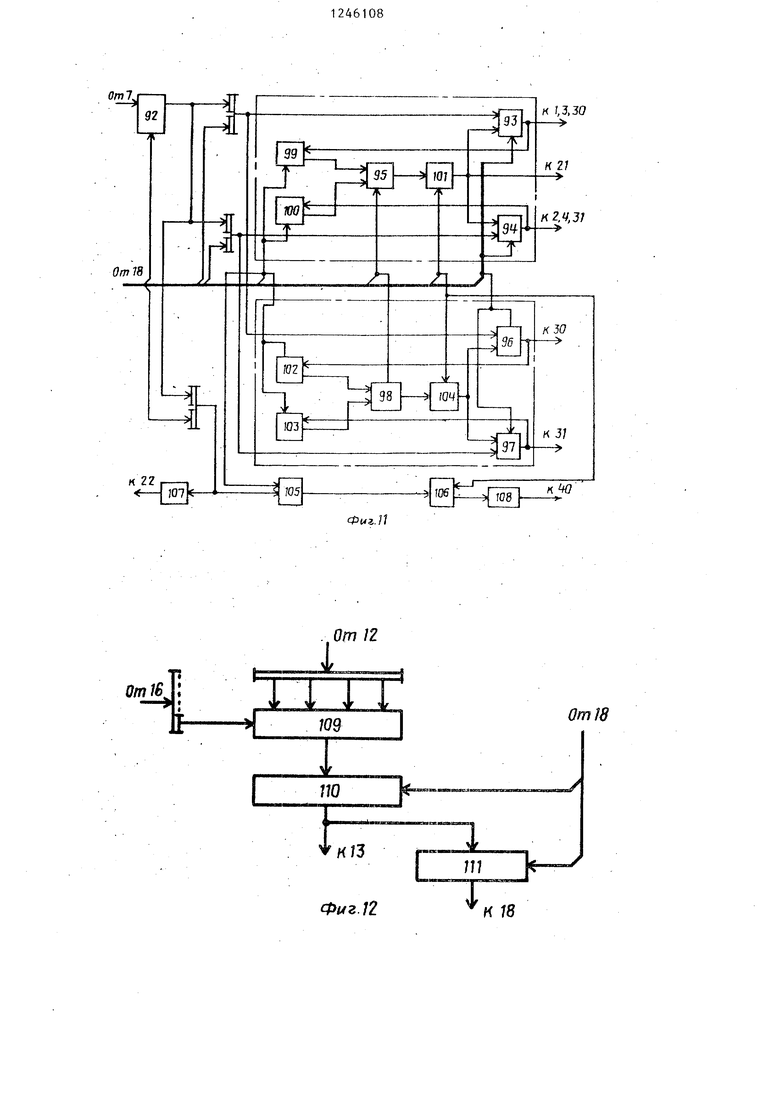

Выполнение микрокоманды Арифметика осуществляется следующим образом (фиг. 15).

Выборка микрокоманды осуществляется в цикле вьтолнения предыдущей микрокоманды. По первому синхросиг- н.алу в регистр 16 из коммутатора адреса заносится адрес выбираемой микрокоманды. Адрес поступает в блок 12 Содержимое регистра адреса крнтроли461088

руется по паритету элементом 38.Ин- . формация из бло.ка 12 поступает в | узел 14. Из блока 12 считывается 16 байт. С помощью коммутатора 109 вы- 5 бирается требуемое (4 байт), определяемое с помощью младших разрядов адреса, поступающих на управляющий вход коммутатора 109. Выбран- , ная информация по третьему синхро10 сигналу записывается в регистр 110, а по четвертому синхросигналу переписывается в регистр 111 узла 114.Регистр 111 является регистром микроманды. Его содержимое контролируется

15 ,по паритету с помощью элемента 36.- Информация из регистра 111 поступает в дешифратор 18 на дешифратор 116. С помощью, дешифратора 116 выбрасывается группа сигналов, определякнцих

20 адрес следующей микрокоманды (выход 119 дешифратора 116), которые через коммутатор 17 поступают в регистр 16 и запоминаются там по первому синхросигналу микрокоманды Арифметика.

25 Если в микрокоманде задан переход

по признаку или по анализу бита, то через коммутатор 17 передаются соответственно регистр 82 блока 8 или байт данных, выдаваемый через комму30 татор 76.

С помощью дешифратора 116 вырабатывается сигнал, определяющий микро- . команду Арифметика (выход 120 де- щифратора 116), а также сигнал (выJJ .ход 112 дешифратора 116), задающий режим работы генератора 117 для выборки соответствующей последовательности синхросигналов, которые с помощью группы элементов 118 формируют

4Q последовательность временных сигналов в соответствии с выполняющейся микрокомандой, дешифрируемой дешифратором 116 (выход 121). Сигналы с выхода 123 дешифратора 116 поступают во

45 все узлы и блоки процессора.

При подаче сигналов, соответствующих адресным полям операндов, с выхода 120 дешифратора 116 на коммутаторы 93 и 94, 96 и 97 в совокупности

5 с содержимым регистра 92 блока 10 формируется полый адрес источников, находящихся в блоках локальной памяти. Причем с выхода коммутатора 93 формируется адрес блока 1 или 3, а с

55 выхода коммутатора 94 - адрес блоков 2 или 4. При подаче сигналов, соответствующих адресным полям операндов, с выхода 120 дешифратора 116 на вход

. 91

дешифратора 117 и совокупности с. содержимым регистра 92 формируется полный адрес источников, передаваемых через коммутатор 22. дреса источников, находящихся в блоках локальной памяти, контролируются сравнением с помощью схем 30 и 31.

Данные, считанные из блоков локальной памяти, через коммутаторы 24 и 25 поступают на входы коммутаторов 5 и 6. Содержимое регистра, выбранного коммутатором 22, поступает на соответствующий вход коммутатора 5, Кроме того, на соответствующие входы коммутаторов 5 и 6 поступает содер- жимое регистра 82. Управляющие сигналы с выхода 120 дешифратора 116 управляют коммутаторами 75 и 79 cqoTBeT ственно коммутаторов 5 и 6 и обеспечивают передачу соответствующих ин- формационных потоков на входы регистров 77 и 81, Информация в регистрах 77 и 81 запоминается по первому синхросигналу в цикле микрокоманды.

Сигналы полей микрокоманды, управ- ляющие форматом информации, с выхода 120 дешифратора 116 поступают на управляющие входы коммутаторов 76 и 80 С помощью коммутаторов 76 и 80 осуществляется перекомпоновка байтов.Инфор мация с выходов коммутаторов 76 и 80 поступает на входы арифметико-логического устройства, на управляющем входе которого устанавливается код выполняемой операции. По окончании операции результат и признаки результата устанавливаются, цо шестому синхросигналу.

Для формирования адреса назначения в блоке 10 адреса источников блоков локальной памяти с выхода коммутаторов 93i и 94, 96 и 97 запоминаются соответственно в регистрах 99 и 100, 102 и 103 по второму синхросигналу, С помощью коммутаторов 95.и 98 осуществляется выборка адреса первого или второго операнда, по которому будет производиться запись, т„е микрокоманда является двухадресной. Адрес назначения через коммутаторы 95 и 96 поступает в регистры 101 и 104 соответственно и запоминается по пятому синхросигналу. Адрес триггера 70 запоминается в регистре 105 по второму синхросигна.лу, а по пятому синхросигналу переписывается в регистр 106. Маска записываемых байтов результата запоминается в регистре

10810

88 блока 9 по второму синхросигналу, а по пятому синхросигналу содержимое регистра 88 переписывается в регистр 89, Содержимое регистра 89 контролируется по паритету с помощью элемента 91. Если, обнаружено нарушение паритета, то сигналом с выхода элемента 91 закрываются элементы группы 90. В результате блокируется выдача маски наз начения.

Запись результата выполнения операции записывается в следующем цикле синхронизации процессора. Информация с выхода устройства 7 через коммутатор 13 выдается в блоки 1-4,. на вход блока 40 и на выход 41, .Запись результата производится по третьему синхросигналу. При записи в блок локальной памяти одновременно производится запись в блоки 1 и 2 или 3 и 4, Информация, записанная в блоки локальной памяти, считывается и сравнивается между собой. В случае несравнения схемой 28 регистрируется сбой,.Кроме того, считанная информация поступает на коммутатор 5 и через коммутатор 75 запоминается- в регистре 78 по пятому синхросигналу. Содержимое р.егистра 78 сравнивается с содержимым регистра 27 с помощью схемы 29. В регистре 27 хранится результат операции устройства 7, запоминаемый по первому синхросигналу.

.Адрес текущей микрокоманлы фиксируется в регистре 26 в первую группу разрядов по третьему синхросигналу, а во вторую - по шестому синхросигналу. Первая группа разрядов регист-. ра 26 в микрокоманде Арифметика не используется. Вторая группа разрядов регистра 26 используется для сохранения адреса текущей микрокоманды в течение всего цикла ее выполнения.

Состояние процессора в каждом цикле по четвертому синхросигналу запоминается в регистрах 68 и 69, В регистре 68 хранится адрес текущей микрокоманды, в регистре 69 - значение оперешда,, который будет записан в результате выполнения микрокоманды. Информация в регистрах 68 и 69 относится к первому циклу синхронизации выполнения микрокоманды. Информация в регистр 69 поступает с выхода коммутатора 23, с помощью которого выбирается тот из операндов, по адресу которого будет произведена запись результата.

П1

По третьему синхросигналу в каждом цикле процессора состояние его запоминается в регистрах 64-67.Информация в регистрах 64-67 для данной микрокоманды действительна после второго цикла синхронизации процессора. В регистре 64 запоминается адрес блоков локальной памяти, по которому была произведена запись, В регистре 65 запоминается маска назначения. - В -регистре 66 запоминается адрес выполненной микрокоманды. В -регистре 67 - операнд, используемый в качестве источника, по адресу которого был записан результат..

Опрос сбоев, относящихся к выборке микрокоманды, производится по пятому синхросигналу в микрокоманде, предшествующей вьшолняемой. Опрос сбоев, связанных с выборкой источни- ков, производится по пятому синхросигналу в первом цикле синхронизации связанном с выполнением данной микрокоманды. Опрос сбоев, связанных с выполнением операции и записью резуль- тата, осуществляется по пятому и шестому синхр осигналам во втором цикле синхронизации, связанном с вьшолне- нием данной микрокоманды. Занесение в регистры 82 и 83 и в регистр 92 про- изводится по дешифрации микрокода с выхода устройства 7 по шестому синхросигналу в первом цикле синхронизации данной микрокоманды. Сброс регистров 44 и 46 и триггера 53 производится по дешифрации микрокода по шестому синхросигналу в первом цикле синхронизации данной микрокоманды.

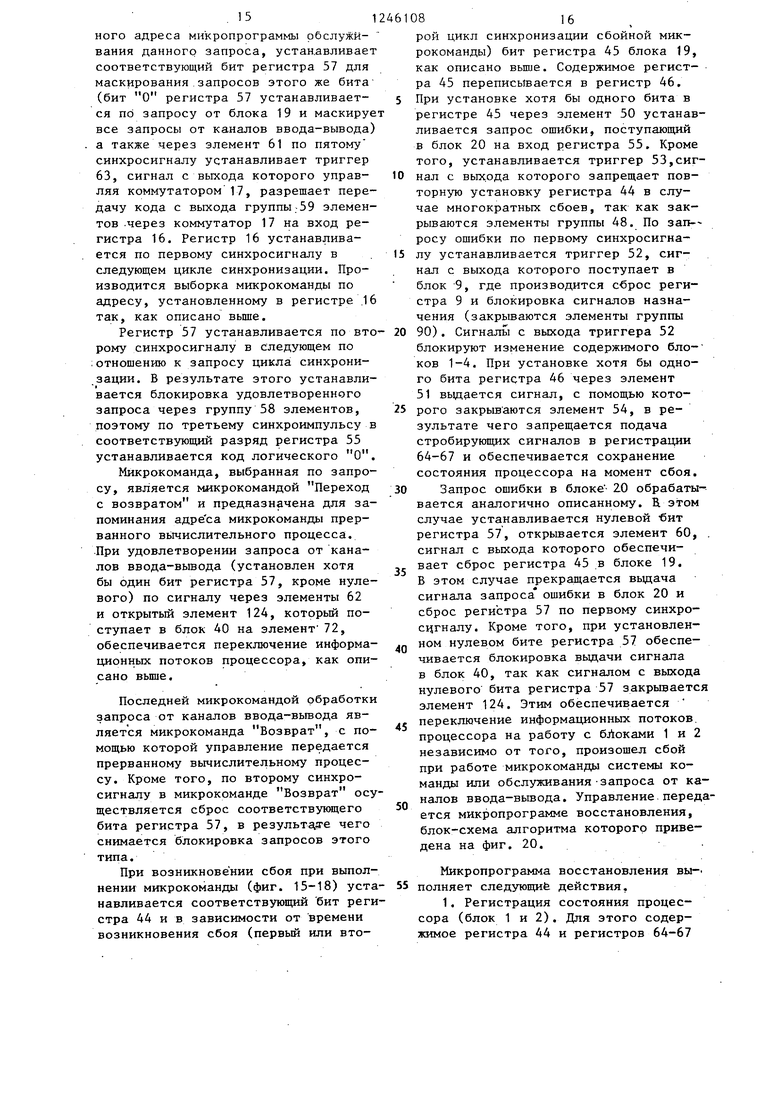

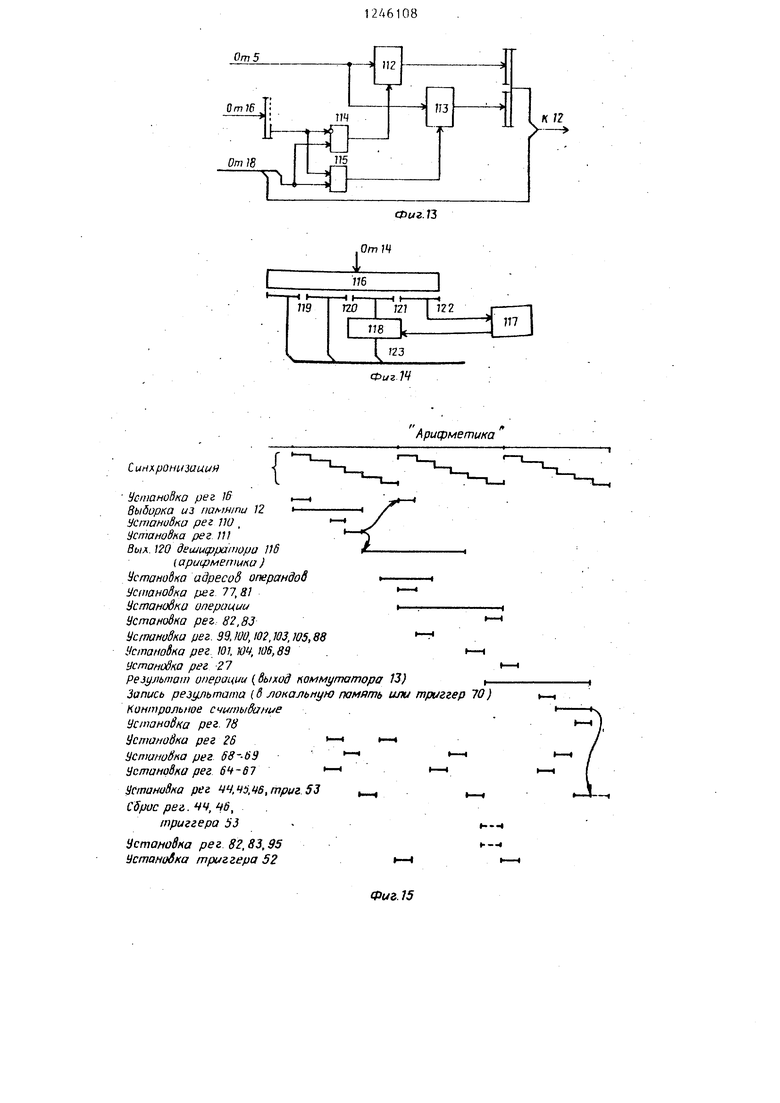

С помощью микрокоманды Память производится чтение или запись инфор- мации в блок 11 или блок 12. Адрес данных поступает через коммутатор 5. Данные из памяти поступают через коммутатор 13.

Выполнение микрокоманды Память осуш;ествляется следующим образом (фиг. 16). Выборка микрокоманды осуществляется в цикле выполнения предыдущей микрокоманды так же, как и при выборке микрокоманды.Арифметика.С помощью дешифратора 116 вырабатывается сигнал, определяющий микрокоманду Память Чвыход 120 дешифратора 116), а сигнал (выход 122 дешифратора 116), задающий режим рабо- ты генератора 117. Сигнал, определяющий микрокоманду Память, выдается в течение двух циклов синхронизации

108

12

процессора, включая паузу между циклами. Длительность паузы определяется генератором 117 и зависит от того производится обращение к блоку 11 лпи блоку 12. Сигналы с выхода 123 дешифратора 116 поступают во .все узлы и блоки процессора.

Считывание адреса обращения производится из блоков 2 или 4 в регистр 81 коммутатора 6. Адрес из регистра 81 поступает в блок 11 или на коммутатор 17 при обращении к блоку 12. Со-держимое регистра 81 контролируется по паритету элементом 34. Информация в регистр 81 принимается по первому синхросигналу первого цикла синхронизации так же, как чтение операнда в микрокоманде Арифметика. Если производится обращение к блоку 12, то адрес обращения через коммутатор 17 поступает в регистр 16 по пятому синхросигналу первого цикла, предварительно по третьему синхросигналу первого цикла содержимое регистра 16 сохраняется в первой группе разрядов регистра 26. Восстановление содержимого регистра 16 производится во втором

цикле синхронизации из первой группы разрядов регистра 26 по пе-рвому синхросигналу. Содержимое регистра 26 поступает в регистр 16 через коммутатор 17.

Если вьшолняется .операция записи, то записываемая информация поступает на первьш выход коммутатор 5 так же, как и при считыв.ании первого операнда в микрокоманде Арифметика. Данные для записи поступают в блок 11 и в узел 15. При записи в блок 12 данные помещаются в четное или нечетное слово двойного слова, адрес которого указан в регистре 16. Информация, записываемая в блок 12, помещается в регистр 112 или 113 в зависимости от младших разрядов адреса С1 бращения,что определяется с помощью элементов 114 и 115. Занесение в регистры 112 и 113 производится по четвертому синхросигналу в первом цикле синхронизации.

Запуск блоков 11 или 12 памяти осуществляется по шестому синхросигналу в первом цикле синхронизации при операциях чтения и записи.

При выполнении операции чтения из блока 11 данные, считанные из памяти, поступают на вход коммутатора 13. При выполнении операции чтения из блока 12 данные, считанные из па1312

мяти, поступают в регистр 110 через коммутатор 109 и запоминаются по первому синхросигналу во втором цикле синхронизации, а затем поступают на вход коммутатора 13. Данные с выхода коммутатора 13 поступают в блоки 1-4 и .на выход 41, Запись данных в блоки 1 и 2 или 3 и 4 производится во втором цикле синхронизации по пятому синхросигналу. Запись производится по адресу первого операнда, формируемого блоком адресации так же, как и при выполнении микрокоманды Арифметика. Маски байтов при записи в блоки локальной памяти формируются так же, как при выполнении микрокоманды Арифметика, описанной выше. Установки регистров блока 19,-блока 21 и второй группы разрядов регистра 26 осуществляются аналогично, как и в микроко- манде Арифметика. С помощью микрокоманды Переход с возвратом ствляется запоминание в ячейки локальной памяти адреса текущей м крокоман- ды. Микрокоманда используется для сохранения адреса выполняемой микрокоманды при прерывании вычислительного процесса запросами от каналов,

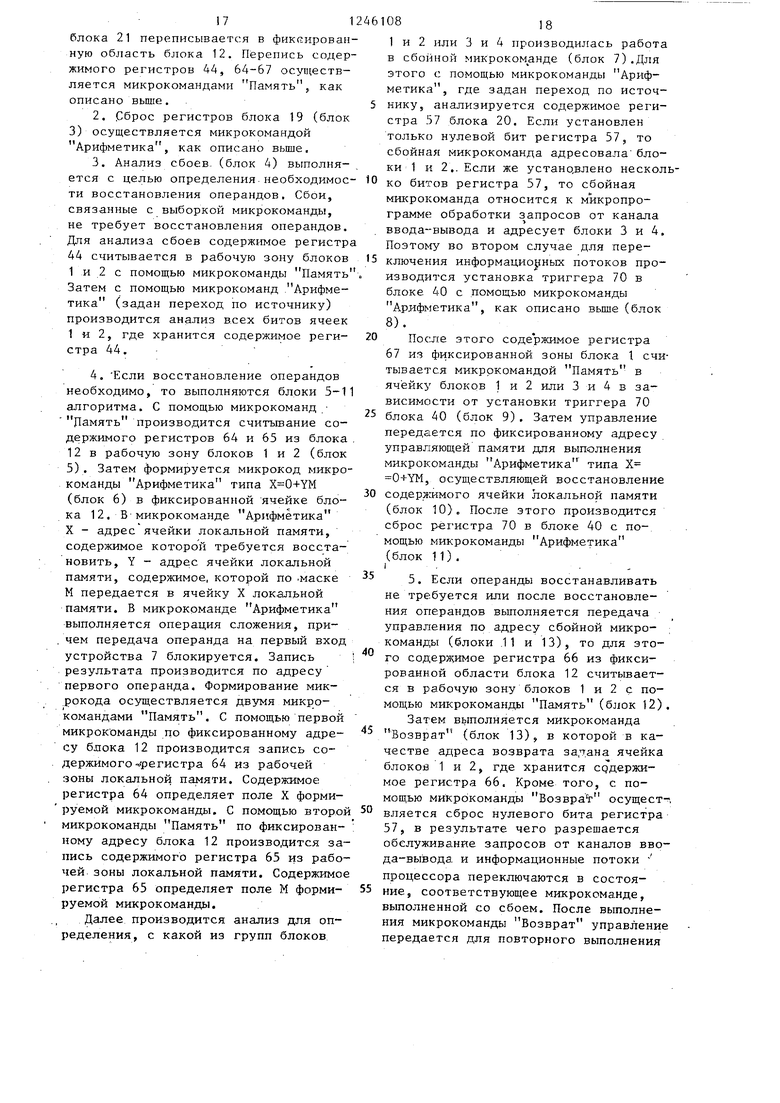

Микрокоманда Переход с возвратом (фиг. 17) вьшолняется анало).- йчно мик- кроманде Арифметика, в которой выполняется операция сложения операндов а в качестве первого операнда используется первая группа разрядов pef HCT- ра 26, в качестве второго операнда - ячейка блока локальной памяти. Результат записывается по адресу второго операнда. Отличие выполнения микрокоманды Переход с возвратом от микрокоманды Арифметика заключается в том, что при выборке второ-го операнда блокируется передача информации через коммутатор 80 (коммутатор б), поэтому первый операнд передается через -устройство 7 без изменений.Че- рез коммутатор 23 передается содержимое регистра 77. ,

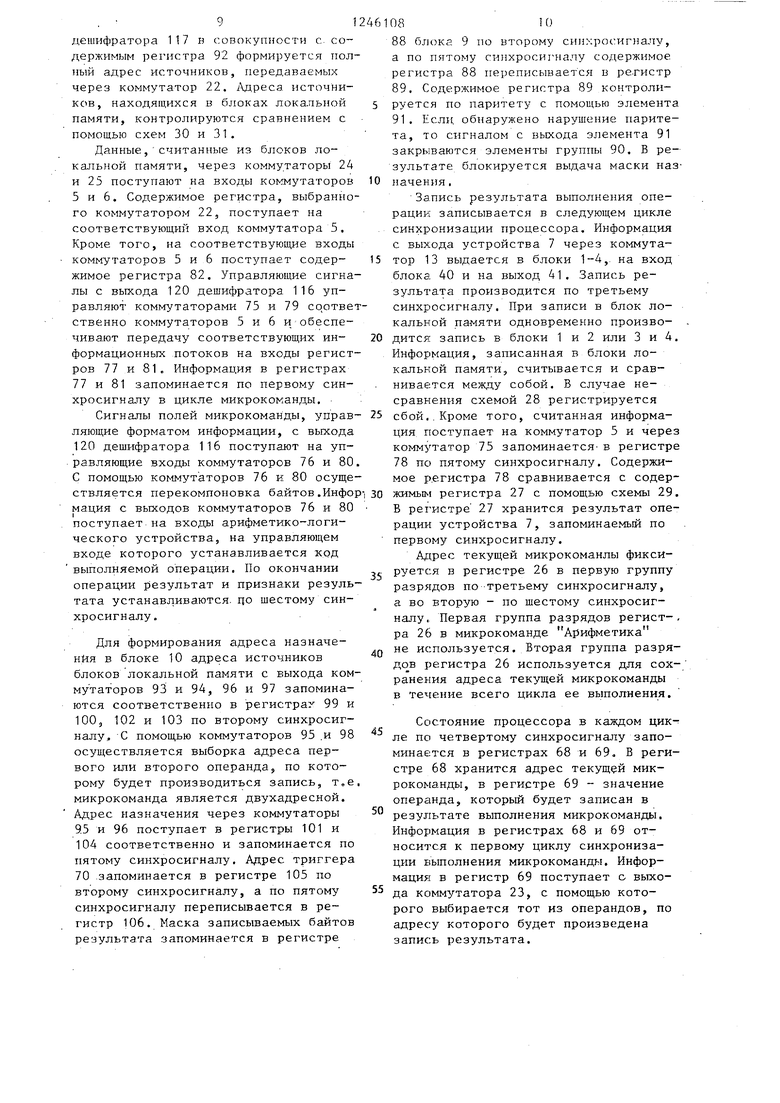

С помощью микрокоманды Возврат осуществляется передача управления на микрокоманду, адрес которой хра- нится в ячейке блока локальной памяти, указанной в микрокоманде Кроме того, с помощью микрокоманды осуществляется сброс битов регистра 57

Выполнение микрокоманды Возврат осуществляется следукнцим образом (фиг. 18). Выборка микрокоманды осуществляется в цикле вьшолнения пре08

14

дыдущей микрокоманды так же, как и при выборке микрокоманды Арифметика С помощью дешифратора 116 вырабатывается сигнал, определяющий микрокоманду Возврат (выход 120 дешифратора 116), а также.сигнал, задающий режим работы генератора 117. Сигналы с выхода 123 дешифратора 116 поступают во все узлы и блоки процессора.

Считывание .адреса микрокоманды из блока 2 или 4 в регистр 81 коммутатора 6 производится так, как описано выше. Содержимое регистра 81 поступает на. коммутатор 17 и запоминается в регистре 16 в первой группе разрядов регистра 26 по третьему синхросигнал Адрес поступает в блок 12. Информация, считанная из блока 12, поступает в узел 14. С помощью коммутатора 109 выбирается требуемое слово (4 байт) , определяемое с помощью младших разрядов адреса, поступающих на управляющий вход коммутатора 109. Выбранная информация по пятому синхросигналу записывается в регистр 110, а по ttiecTOMy синхросигналу пере письшается в регистр 111 узла 14. Содержимое регистра 111 определяет чикрокомандУ5 которая будет выполняться в следующем цикле синхронизации процессора. Адрес следующей микрокоманды формируется как описано выще и заносится в регистр 16 по первому синхросигналу в следующем цикле синхронизации/

Если в микрокоманде Возврат заданы условия сброса соответствующих битов регистра 57 блока 2Л, то по второму синхросигналу вырабатываются управляющие сигналы сброса.

Запрос на обслуживание каналов ввода-вывода (фиг. 19) вызьшается возбу:ждением одного из разрядов ши ны 43, соответствующие сигналы которых поступают на элементы группы 58 блока 20. Если соответствующей элемент группы 58 открыт (бит регистра 57, маскир уюЕций этот вид запросов, не установлен), то по третьему синхро- сигнапу производится установка соответствующего бита регистра 55. Код, згстановленный в регистре 55, дешифрируется дешифратором 56 для выбора самого приоритетного запроса. Возбуждение одной из шин дешифратора 56 указьпзает на удовлетворение соответствующего типа запроса и через элементы группы 59 формирует код началь

. 15

него адреса микропрограммы обслужи- вания данного запроса, устакавливает соответствующий бит регистра 57 для маскирования запросов этого же бита (бит О регистра 57 устанавливает- ся по запросу от блока 19 и маскируе все запросы от каналов ввода-вывода) а также через элемент 61 по пятому синхросигналу устанавливает триггер 63, сигнал с выхода которого управ- ляя коммутатором 17, разрешает передачу кода с выхода группы .-5 9 элементов .через коммутатор 17 на вход регистра 16. Регистр 16 устанавливается по первому синхросигналу в . следующем цикле синхронизации. Производится выборка микрокоманды по адресу, установленному в регистре .16 так, как описано вьщ1е.

Регистр 57 устанавливается по вто рому синхросигналу в следующем по ;отношеншо к запросу цикла синхронизации. В результате этого устанавливается блокировка удовлетворенного запроса через группу 58 элементов, поэтому по третьему синхроимпульсу в соответствующий разряд регистра 55 устанавливается код логического О.

Микрокоманда, выбранная по запросу, является микрокомандой Переход с возвратом и предназначена для запоминания адре са микрокоманды прерванного вычислительного процесса. При удовлетворении запроса от каналов ввода-вывода (установлен хотя бы один бит регистра 57, кроме нулевого) по сигналу через элементы 62 и открытый элемент 124, который поступает в блок 40 на элемент 72, обеспечивается переключение информа- ционных потоков процессора, как описано выше.

Последней микрокомандой обработки запроса от каналов ввода-вывода является микрокоманда Возврат, с по- мощью которой управление передается прерванному вычислительному процессу. Кроме того, по второму синхросигналу в микрокоманде Возврат осуществляется сброс соответствующего бита регистра 57, в результгуге чего снимается блокировка запросов этого типа.

При возникновении сбоя при выполнении микрокоманды (фиг. 15-18) уста навливается соответствующий бит регистра 44 и в зависимости от времени возникновения сбоя (первый или вто

5

0 5

о Q

0

5

5

0816 ,

рой цикл синхронизации сбойной микрокоманды) бит регистра 45 блока 19, как описано вьпие. Содержимое регистра 45 переписывается в регистр 46. При установке хотя бы одного бита в регистре 45 через элемент 50 устанавливается запрос ошибки, поступающий в блок 20 на вход регистра 55. Кроме того, устанавливается триггер 53,сигнал с вых.ода которого запрещает повторную установку регистра 44 в случае многократных сбоев, так как закрываются элементы группы 48. По зап-- росу ошибки по первому синхросигналу устанавливается триггер 52, сигнал с выхода которого поступает в блок 9, где производится сброс регистра 9 и блокировка сигналов назначения (закрываются элементы группы 90). Сигналь с выхода триггера 52 блокируют изменение содержимого бло- ков 1-4. При установке хотя бы одного бита регистра 46 через элемент 51 выдается сигнал, с помощью которого закрьшаются элемент 54, в результате чего запрещается подача стробирующих сигналов в регистрации 64-67 и обеспечивается сохранение состояния процессора на момент сбоя.

Запрос ошибки в блоке - 20 обрабатывается ангшогично описанному. Д этом случае устанавливается нулевой -бит регистра 57, открьшается элемент 60, . сигнал с выхода которого обеспечивает сброс регистра 45 в блоке 19. В этом случае прекращается выдача сигнала запроса ошибки в блок 20 и сброс регистра 57 по первому синхро- сцгналу. Кроме того, при установленном нулевом бите регистра 57 обеспечивается блокировка выдачи сигнала в блок 40, так как сигналом с выхода нулевого бита регистра 57 закрывается элемент 124. Этим обеспечивается переключение информационных потоков, процессора на работу с бЛоками 1 и 2 независимо от того, произошел сбой при работе микрокоманды системы команды или обслуживания-запроса от каналов ввода-вьшода. Управление,передается микропрограмме восстановления, блок-схема алгоритма которого приведена на фиг. 20.

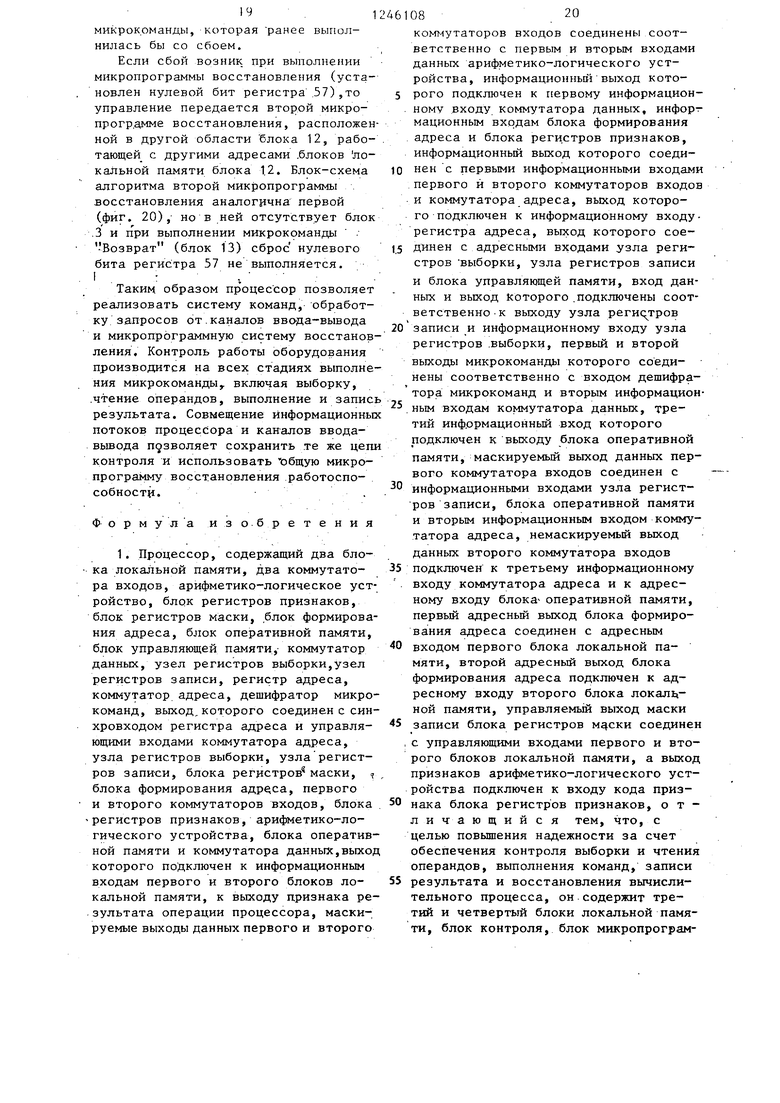

Микропрограмма восстановления вы-, полняет следующие действия.

1. Регистрация состояния процессора (блок 1 и 2). Для этого содержимое регистра 44 и регистров 64-67

7

блока 21 переписывается в фиканрован иую область блока 12. Перепись содержимого регистров 44, 64-67 осуществляется микрокомандами Память, как описано выше. .

2.Рброс регистров блока 19 (блок 3) осуществляется микрокомандой Арифметика, как описано выше.

3.Анализ сбоев, (блок 4) выполняется с целью определения-необходимое ти восстановления операндов. Сбои, связанные с выборкой микрокоманды,

не требует восстановления операндов. Для анализа сбоев содержимое регистр 44 считывается в рабочую зону блоков 1 и 2 с помощью микрокоманды Память Затем с помощью микрокоманд .Лрифме

тика (задан переход по источнику) производится анализ всех битов ячеек 1 и 2, где хранится содержимое регистра 44. -

4, Если восстановление операндов необходимо, то выполняются блоки 5-11 алгоритма. С помощью микрокоманд Память производится считьюание содержимого регистров 64 и 65 из блока , 12 в рабочую зону блоков 1 и 2 (блок 5). Затем формируется микрокод микро- команды Арифметика типа (блок 6) в фиксированной ячейке блока 12. В-микрокоманде Арифметика X - адрес ячейки локальной памяти, содержимое которой требуется восстановить, Y - адрес ячейки локальной

5

20

25

30

40

45

памяти, содержимое, которой по .маске 5 М передается в ячейку X локальной памяти. В микрокоманде Арифметика выполняется операция сложения, причем передача операнда на первый вход устройства 7 блокируется. Запись результата производится по адресу первого операнда. Формирование микрокода осуществляется двумя микрокомандами Память. С помощью первой микрокоманды по фиксированному адресу блока 12 производится запись содержимого - регистра 64 из рабочей зоны локальной памяти. Содержимое регистра 64 определяет поле X формируемой микрокоманды. С помощью второй микрокоманды Память по фиксирован- ; ному адресу блока 12 производится запись содержимого регистра 65 из рабочей зоны локальной памяти. Содержимое регистра 65 определяет поле М формируемой микрокоманды.

Далее производится анализ для определения , с какой из групп блоков

50

55

1 и 2 или 3 и 4 производилась работа в сбойной микроком анде (блок 7) .Для этого с помощью микрокоманды Арифметика, где задан переход по источнику, анализируется содержимое регистра 57 блока 20. Если установлен только нулевой бит регистра 57, то сбойная микрокоманда адресовала блоки 1 и 2,. Если же установлено несколько битов регистра 57, то сбойная микрокоманда относится к микропрограмме обработки запросов от канала ввода-вывода и адресует блоки 3 и 4. Поэтому во втором случае для переключения информацио|1ных потоков производится установка триггера 70 в блоке 40 с помощью микрокоманды Аряфметика, как описано вьше (блок 8).

После этого соде ржимое регистра 67 из фиксированной зоны блока 1 считывается микрокомандой Память в ячейку блоков 1 и 2 или 3 и 4 в зависимости от установки триггера 70

блока 40 (блок 9). Затем управление передается по фиксированному адресу управляюп5ей памяти для выполнения микрокоманды Арифметика типа. Х 0+YM, осуществляющей восстановление

содеряммого ячейки локальной памяти (блок 10). После этого производится сброс регистра 70 в блоке 40 с по-, мощью микрокоманды Арифметика (блок 11).

5. Если операнды восстанавливать не требуется или после восстановления операндов выполняется передача управления по адресу сбойной микро- ; команды (блоки .11 и 13), то для этого содержимое регистра 66 из фиксированной области блока 12 считывается в рабочую зону блоков 1 и 2 с помощью микрокоманды Память (блок 12).

Затем выполняется микрокоманда Возврат (блок 13), в которой в качестве адреса возврата задана ячейка блоков 1 и 2, где хранится срдержи- мое регистра 66. Кроме того, с помощью микрокоманды Возврат осущест-. вляется сброс нулевого бита регистра 57, в результате чего разрешается обслуживание запросов от каналов ввода-вывода: и информационные потоки процессора переключаются в состояние, соответствующее микрокоманде, выполненной со сбоем. После выполнения микрокоманды Возврат управление передается для повторного выполнения

19 . 1 микрокоманды, которая ранее выполнилась бы со сбоем.

Если сбой возник при выполнении микропрограммы восстановления (установлен нулевой бит регистра .57) ,то управление передается второй микро- прогр. восстановления, расположенной в другой области блока 12, рабо- тающей с другими адресами .блоков локальной памяти блока 1.2. Блок-схема алгоритма второй микропрограммы восстановления аналогична первой (фиг. 20), но в ней отсутствует блок .3 и при выполнении микрокоманды . - Возврат (блок 13) сброс нулевого бита регистра 57 не выполняется.

I . : г

Таким образом процессор позволяет

реализовать систему команд, обработку запросов от.каналов ввода-вывода и микропрограммную систему восстановления. Контроль работы оборудования производится на всех стадиях выполнения микрокомандыу включая выборку, .чтение операндов, выполнение и запись результата. Совмещение информационных потоков процессора и каналов ввода- вьшода П9зволяет сохранить .те же цепи контроля и использовать йбщую микропрограмму восстановления работоспособности .

Формула изобретения

1. Процессор, содержащий два блока локальной памяти, два коммутато- ра входов, арифметико-логическое устройство, блок регистров признаков, блок регистров маски, блок формирования адреса, блок оперативной памяти, блок управляющей памяти,- коммутатор данных, узел регистров выборки,узел регистров записи, регистр адреса, коммутатор адреса, дещифратор микрокоманд, выход,которого соединен ссин- хровходом регистра адреса и управля- ющими входами коммутатора адреса, узла регистров выборки, узла регистров записи, блока регистров маски, ч блока формирования адреса, первого и второго коммутаторов входов, блока регистров признаков, арифметико-логического устройства, блока оперативной памяти и коммутатора данных,выход которого подключен к информационным входам первого и второго блоков ло- кальной памяти, к выходу признака результата операции процессора, маскируемые выходы данных первого и второго

5 10 1.5

25

20

30

35 5 50 55

10820

коммутаторов входов соединены соответственно с первым и вторым входами данных арифметико-логического устройства, информационны выход которого подключен к первому информационному входу коммутатора данных, информационным входам блока формирования адреса и блока регистров признаков, информационный выход которого соединен с первыми информационными входами первого и второго коммутаторов входов и коммутатора адреса, выход которого подключен к информационному входу- регистра адреса, выход которого соединен с адресными входами узла регистров выборки, узла регистров записи и блока управляющей памяти, вход данных и выход Которого.подключены соответственно к выходу узла регис тров

записи и информационному входу узла регистров .выборки, первый и второй выходы микрокоманды которого соединены соответственно с входом дешифра тора микрокоманд и вторым информацион.ным входам коммутатора данных, третий информационный вход которого подключен к выходу блока оперативной памяти, маскируемый выход данных первого коммутатора входов соединен с информационными входами узла регист ров записи, блока оперативной памяти и вторым информационным входом коммутатора адреса, немаскируемый выход данных второго коммутатора входов подключен к третьему информационному входу коммутатора адреса и к адресному входу блока- оперативной памяти, первый адресный выход блока формирования адреса соединен с адресным входом первого блока локальной памяти, второй адресный выход блока формирования адреса подключен к адресному входу второго блока локаль - ной памяти, управляемый выход маски записи блока регистров соединен с управляющими входами первого и второго блоков локальной памяти, а выход признаков арифметико-логического устройства подключен к входу кода признака блока регистров признаков, отличающийся тем, что, с целью повышения надежности за счет обеспечения контроля выборки и чтения операндов, выполнения команд, записи результата и восстановления вычислительного процесса, он содержит третий и четвертый блоки локальной памяти, блок контроля, блок микропрограм211; 4(И

мных прерываний,- блок регистрон повторения, четыре,коммутатора признаков, регистр адреса текущей микрокоманды, регистр результата, четыре . схемы сравнения, шесть элементов 5 ИСКЛЮЧАЩЕЕ ИЛИ и блок коммутации данных, информационный выход блока контроля, выход блока регистров повторения, первый вьгкод регистра адреса текущей микрокоманды, вход призна- Ю ка результата операции процессора, выход сохранения признаков запросов блока микропрограммных прерываний соединены с информационными входами с первого по пятый первого кс$ммута- iS тора признаков, выход которого подключен к второму информационному входу первого коммутатора входов, немаскируемый выход которого соединен с входом первого элемента ИСКЛЮЧАЮЩЕЕ 20 ИЛИ и первым информационным входом . второго коммутатора признаков, второй информационный вход которого и вход второго элемента ИСКЛЮЧ.М)ЩЕЕ ИЛИ подключены к немаскируемому выходу 25 данных второго коммутатора, входов, первый и второй информационные входы tpeTbero коммутатора признаков, соединены соответственно с выходами пер-; вого и третьего блоков локальной па- 30 мяти, первый и второй информационные входы четвертого коммутатора признаков подключены к выходам второго и четвертого бл оков локальной памяти, выхдд третьего коммутатора признаков j,j соединен с цервым входом первой схеы :сравнения и третьим информационным входом первого коммутатора входов, второй информационный вход второго

коммутатора входов и второй вход пер- 40 ой схемы сравнения подключены к вы- ходу четвертого коммутатора признаковj ВЫХОД коммутатора данных соединен с информационными входами третьего и четвертого блоков локальной памяти, 45 входом третьего элемента ИСКЛЮЧАЩЕЕ ИЛИ и информационным входом бЛока коммутации данных, выход которого подключен к входам управления выборой блоков локальной памяти с первого 50 по четвертый и управляющим входам третьего и четвертого коммутаторов

признаков, выход регистра результата

.

соединен с первым входом второй схемы сравнения, второй вход которой под- 55 ключей к выходу контрольного чтения первого коммутатора входов, первый адресный выход блока формирования

8 22

адреса соединен с адресным входом третьего блока локальной памяти и первым входом третьей схемы сравнения, второй вход которой под 5лючен к .первому дополнительному адресному выходу блока формирования адреса, второй адресньп выход которого соединен с адресным входом четвертого блока локальной памяти и первым вхо- дом четвертой схемы сравнения,второй вход которой подключен к второму дополнительному адресно гу выходу блока формирования адреса, выход адреса назначения которого соединен с входом адреса назначения блока регистров повторения, вход записи которого подключен к неуправляемому выходу - маски записи блока регистров маски, управляемый выход маски записи которого соединен с управляющими входами третьего и четвертого блоков локальной памяти и блока коммутации данных, адресный вход которого подключ ен к выходу адреса записи регистров.блока формирования адреса, управхшющий вход первого коммутатора признаков соединен с выходом адреса чтени г. регистров блока формирования адресаэ вход управления выборкой блока коммутации данных подключен к выходу упрай леиия коммутацией блока.микро- про. прерываний, выход коммута- . тора адреса соединен с входом данных регистра адреса текущей микрокоманды второй, выход которого подключен к . входу адреса микро команды блока регистров повторения, выход фиксации контрольной точки блока контроля и выход- второго коммутатора признаков соединены соответственно с входом блокировки и входом данных блока регистров повторения, управляющие входы блока регистров повторенияJ блока микропрограммных прерываний, второго коммутатора признаков, блока контроля,, регистра результата и синхровход регистра адреса текущей микрокоманды подключены к выходу дешифратора микрокоманд, вход которого соединен с входом четвертого .элемента ИСКЛЮЧАЮШ.ЕЕ ШШ,ин-- формаиион:ный выход арифметико-логи- ческо о устройства подключен к входу пятого элемента ИСКЛЮЧАКМДЕЕ ИЛИ .и к информационному входу регистра.результата, информационный и дублирующий . выходы: блока регистров признаков соединены с первым и вторым входами пятой схемы сравнения, выход регистра

23

адреса подключен к входу шестого элемента ИС1ШЮЧАЮ1ЦЕЕ ИЛИ, маскируемьш выход данных первого коммутатора входов соединен с входами седьмого элемента ИСКЛЮЧАЩЕЕ ИЛИ, вход блокировки блока регистров маски подключен к выходу блокировки записи блока контроля, выход запроса и вход сброса которого соединены соответственно с входом запроса контроля и выходом удовлетворения запроса блока микропрограммных прерываний, выход адреса . прерывания и вход запроса от каналов которого подключены соответственно к четвертому информационному входу ком- 5 мутатора адреса и входу запросов процессора, выходы схем сравнения с - первой по пятую, в.ыходы элементов ИСКЛЮЧАЩЕЕ ИЛИ с первого по седьмой и выход ошибки блока регистров маски 20 соединены с входом приема ошибок блока контроля , выход запроса блока микропрограммных прерываний подключен к второму управляющему входу коммутатора адреса, пятый информационный 25 вход которого соединен с первым выходом регистра адреса текущей микрокоманды.

5 10

2. Процессор ПОП.1, отличающийся тем, что блок контроля содержит регистр, ошибок, регистр типов, регистр признаков, две группы элементов И, группу элементов ИЛИ, два элемента ИЛИ, два триггера и элемент И, причем информационным выходом блока является выход регистра ошибок, установочный вход которого соединен с выходами элементов И первой группы, прямые входы которых и входы элементов ИЛИ группы подключе- ны к вьпсодам элементов И второй группы, первые входы которых являются входом приема ошибок блока, вход сброса которого и выходы элементов ИЛИ группы соединены соответственно с входами сброса и установки .регистра типов, выход которого подключен к установочному входу регистра признков и входам первого элемента ИЛИ, выход которого является выходом запроса блока и соединен соответственно с информационными и установочными входами первого и второго триггеров, выход первого триггера является выходом блокировки записи блока, выход второго триггера -подключен к инверсным входам элементов И первой группы выход регистра признаков соединен с

5 2025610824

входами второго элемента ИЛИ, выход которого подключен к инверсному входу , элемента И, вторые входы элементов И второй группы, входы сброса регистра 5 ошибок, регистра признаков, второго триггер;, синхровход первого триггера и прямой вход элемента И соединены с управляющим входом блока, вы- .ходом фиксации контрольной точки ко- 10,,торого является выход элемента И.

3. Процессор поп.1,отлича50 5

0

5

0

5

0

ю щ и и с я тем, что блок микропрограммных прерываний содержит регистр запросов, дешифратор, регистр, группу элементов И, группу элементов ИЛИ, два элемента И, два элемента ИЛИ и триггер, причем входом запроса контроля блока является соответствуюш й разряд входа данных регистров запросов, выход которого соединен с входом дешифратора, выход которого подключен к входам первого элемента ИЛИ, элементов ИЛИ группы, регистра и первому входу первого элемента И, второй вход которого соединен с выходом триггера, вход данных подключен к выходу первого элемента ИЛИ, выход регистра соединен с входами второго элемента ИЛИ и инвepQHЫми входами элементов И группы, прямые входы которых являются входом запроса каналов, блока, а выходы элементов И группы подключены к соответствующим разрядам входа регистра запросов, управляющий вход блока соединен с синхро- входами регистра запросов и триггера, входом сброса регистра, выходами удовлетворения запроса, адреса прерывания, управления коммутацией,запроса и сохранения признаков запросов блока являются соответственно выходу первого элемента И, элементов ИЛИ группы, второго элемента И, выход триггера и выход регистра, соответствующие разряды выхода которого подключены к вторым входам элементов ИЛИ группы и инверсному входу вто рого элемента И, прямой выход которого соединен с выходом второго элемента ИЛИ,

4. Процессор по п.1, отличающий с я тем, что блок регистров повторения содержит 1яесть регистров, причем входами адреса назначения и маски записи блока являются информационные входы первого и второго регистров , информационные входы третьего и четвертого регистров соединены с

25

выходами соответственно пятого и шестого регистров, информационные входы которых являются входами адреса микрокоманды и данных блока, выходы ре- гистров с первого по четвертый являются выходы блока, управляющим входом которого являются синхровходы пятого и шестого регистров, а входом блокировки блока являются синхровходы регистров с первого по четвертый. 5. Процессор поп.1,отлича12А6108 26

данных содержит триггер, элементы И и ИЛИ, причем соответствующий разряд информационного входа блока соединен с входом данных триггера, синхровход 5 которого подключен к выходу элемента И, первый и второй входы которого соединены с соответствующими разрядами управляющего и адресного входов блока,, выходом которого является вы- 0 ход элемента ИЛИ, входы которого подключены к выходу триггера и входу

ю щ и и с я тем, что блок коммутации управления выборкой блока.

Фиг. 2

сриг.З

От 26 От 23

ОтЮОт.9

OmtS

Фиг.В

От 8 От 22

К 7.//,75,77,35

Фмг.7

Фиг. 6

Н23,33

От 8

К 5;6,17.32

От Id От 18

От 25

OmW

IK 32

Фиг.9

83

к 19

31

к 7,2ДЧ

9Q

Фиг.Ю

Фиг 13

Арифметика

Curtf pOHuiauuH

Установка ре г б Выборка из па/ 1Н/пи 12 Установка ре г по , станоВка регП Выл. deujuqjpainopa 116

(арисрмегпика )

Установка адресов операндов

Устанодка ,S1

Остановка операцииУстанодна peZ: 82,83 Усгпамавка рег. 39.100,102,103, J05,88 Уста/юбна рег Ю1, ЮЧ, Ю6,89 Установка рег 27 Рвзумтат операции (выход ммм Запись результата (д локальну Контрольное считывание Установка рег. 78

Установка рег 26

Устано/ на рег Установка рег

Устанавна рег 4Ч,чs,6,mpuг.53 Сброс рей. VV, tf, триггера 53

Установка рег 82,83,95 Устанобка триггера 52

70)

t---t --«

Фиг. 15

Память

Синхронизация

У с таffовна ре г. Ю Выборка из памяти 12 Установка ре г. ПО Устанодна рег. 111

Sbiwd 120 оешисрратора 1J6

(память УстаисЗха адресов локальны/

памятей

Л/77« с с «й оег 77 (ec/w запись ре г. 8/ yc.Tta.hOfj. pez I.ИЗ {если зопись} .дрес в память

станоЗна pez. 26 -

Устано8к.а рвг.Ю (если aSpaunenue

yf pa5ляl-au eu памяти 12)

05pauj,SHUs к. Л или 12

ианные из памяти (если чтение

{выпад ко мм (J та тора J3} Запись данные б локальные памя

icmaнoSкa рвг. ,-,

Чстанодх.а рвг. 64-67 -

истанодна рвг. , , Ч-6,. -

триггера 5J

Син/ ронизащ я

УстаноВка рвг. 16 Выборка из помети 12 Установка рег.. ПО Установка рег..1П Вых. 120 дешисрратооа 116 (Переход с So з Spa том)

Выборка рег 26 через

коммитатор 22

Установка рег. 77

ста но5ко операции АЛУ 7

Установка, рег 99, ЮО, Ю2, Ю5, Устатвка рег. Щ 104,

Установка ре&. 27

Резупьтат операции (выкод

Запись результата

Контрольное считыдание

установна рег. 78 ЯстапоВка pez, ZS ИстаноВм рег. 68-69 Устанодка pet Ястано8ка pez. , f/5, б, mpijzzepa 5Ъ

Переход с воздратом

ФИ7 Л

Синхраниза/ ия

Установка рег. б Выборка из памяти 12.

icmaнoдкa рег. 110 Установка рег. /Г7 Вых.120 деиА лсрратора 116 (возврат)

УстаноЗк а адреса локал

Установка рег.8J

Установка рег. 16

Выборка uj памяти 12

Установка рег. 1Ю .

Установка рег. т

Установка pez. 26

станобка рег. Ястано карег. 64-67

Остановка рег. 44,it5,46, триггера 53 С6/70С регистра 57

возврат

I-ч

Фиг. 18

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Микропрограммное устройство управления | 1984 |

|

SU1262516A1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Устройство для управления каналами | 1979 |

|

SU877519A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Ассоциативный матричный процессор | 1981 |

|

SU1005065A1 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| Селекторный канал | 1983 |

|

SU1103218A1 |

Изобретение относится к области цифровой вычислительной техники и может быть использовано в электронных вычислительных машинах средней производительности. Целью изобретения является повьппение надежности процессора путем обеспечения контроля выборки и чтения операндов, выполнения команд, записи результата и восстановления вычислительного процесса. Поставленная цель достигается введением в процессор, содержащий два блока локальной памяти, два коммутатора входов, арифметико-логическое устройство, блок регистров признаков,блок регистров, маски, блок формирования адреса, блоки оперативной и управляющей памяти, коммутатор данных, узлы регистров выборки и записи, регистр адреса, коммутатор адреса и дешифратор микрокоманд, дополнительно третьего и четвертого блоков локальной памяти, блока контроля, блока микропрограммных прерываний блока регистров повторения, четырех коммутаторов признаков, регистра адреса текущей микрокоманды, регистра результата, четырех схем сравнения, шести элементов ИСКЛЮЧАКЯЦЕЕ ИЛИ и блока коммутации данных. 4 з.п. ф-лы, 20 ил. .о (О (Л N9 4 Oi

12

.

апрос блока J9 )

Фиг. 19

( бло

. pcz ЧЦ

IB уп

Запить ре г 84,67 в УП

Только дит О

ровен ./7uj

5umof рег 57,

Триггео 70: 1

Более одного бита раВнь I

8

Pei.44,B: 0 Триг2ер53: 0,

цНет воссгпаноВле /( WWW операндов с5оев

ие

12

Чтение рег 66 6 рабочую эону локальных памятей 12

Выполнение микрокоманды возврат: 1 S качестве адреса Возврата - ячейка лональт/к памятей .2, где хранится рег. 66 2. Сброс рег. 57 (Вита)

JL

( &ыиод

Фтг. 20

Редактор Н. Тупица

Составитель Г, Витагеиев

Техред НоБонкало Корректор А. Обручар

За:каз 4002/42Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Чтение ре г 67 В ячейку У лональ- нь/х памятей

Ю

Выполнение микрокомондь

/;

12

Триггер 7О: 0

| Микропрограммный процессор | 1974 |

|

SU535567A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патент США № 3656123, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Контрольный висячий замок в разъемном футляре | 1922 |

|

SU1972A1 |

| Процессор | 1976 |

|

SU670935A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-07-23—Публикация

1984-04-20—Подача