(54) УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ

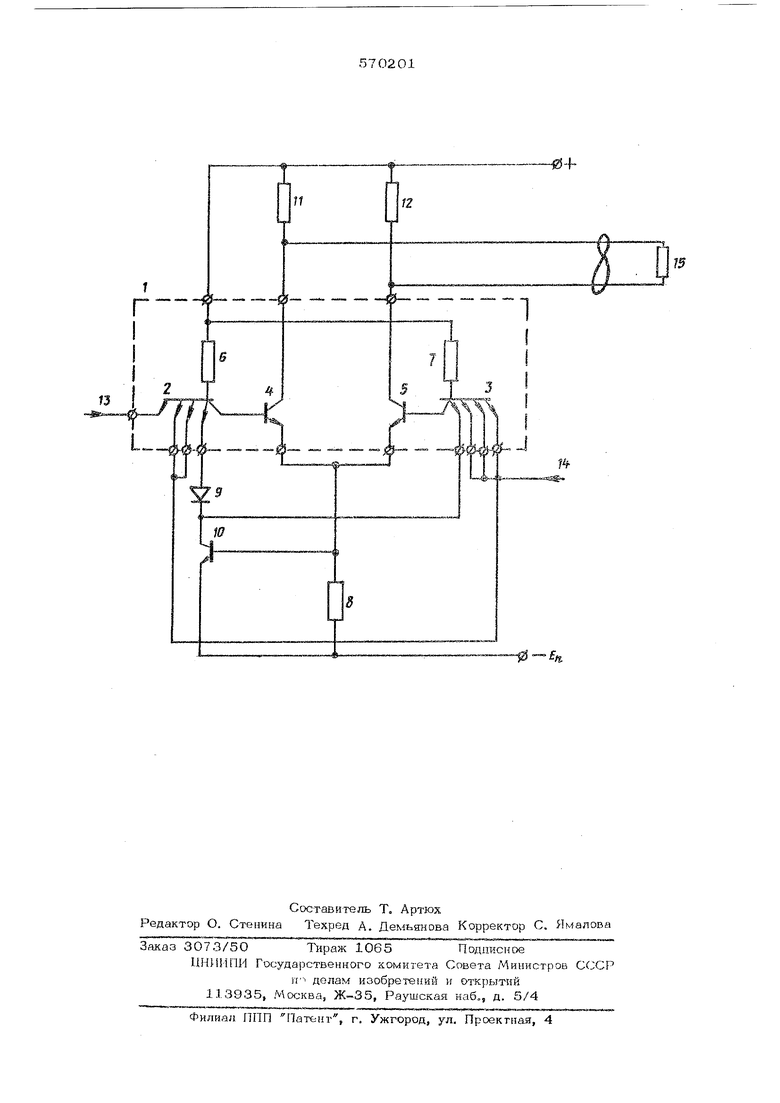

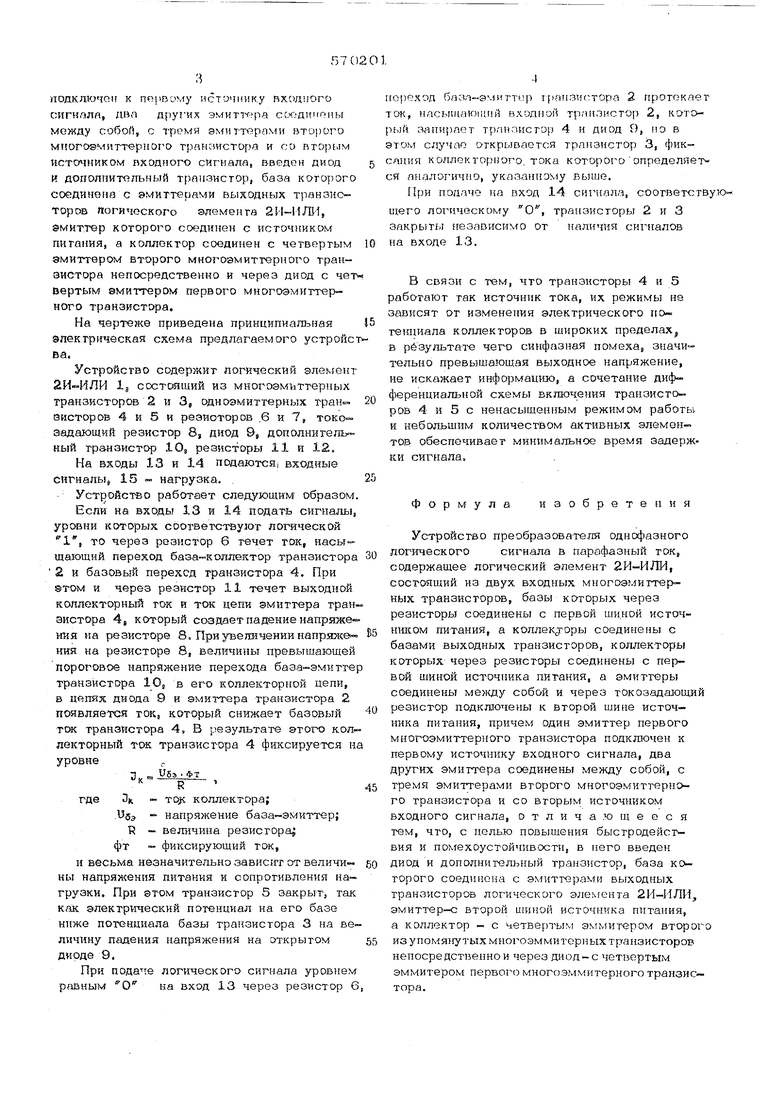

ОДНОФАЗНОГО ЛОГИЧЕСКОГО СИГНАЛА В ПАРАФАЗНЫЙ ТОК подключен к первому ист; чиику входного сигняла, друтих эмит7ч- ра ссюдниоиы между собой, с тремя эмитт-ерпми второго М огс 8м ттер1 0го трпкстстора и сч) вго|лым источником входного сигнала, введен диод к дополнительный транзистор, база которого соединена с эмиттерами выходных транзнс торов люгичоского элемента 2H-l1JTMs эмиттер которого соединен с источником пигания, а коллектор соединен с четвертым эмиттером второго многоэмиттерного транзистора непосредственно и через диод с чет вертым эмиттером первого многоэмиттер- ног-о транзистора. На чертеже приведена принципиальная электрическая схема предлагаемого устройс ва. Устройство содержит логический элемент Ij состш ший из мкогоэмьттерных транзисторов 2 и 3, одноэмиттерных трапэисторов 4 и 5 и реаиоторов .6 и 7, токозадающий резистор 8, диод 9, дополнигель™ ный трэнаистор lOj резисторы 11 и 12. На входы 13 и 14 подаются, входные снгналые 15 - нагрузка, . Уст{эойстБО работает следующим образом Если на входы 13 и 14 подать сигналы уровни которых соогветствузот логической 1, то через резистор 6 течет ток, насыщающий переход база-коллектор транзистора 2 и базовый переход транзистора 4, При STOM и через резистор 11 течет выходной коллекторный ток и ток цепи эмиттера тран зистора 4, который создает падение напряже 5-тя на резисторе 8. Приувепичениинапряже™ ния на резисторе 8, величины превышающей пороговое напряжение перехода база-эмитте транзистора Ю, в его коллекторной цепи, в цепях диода 9 и эмиттера транзистора 2 появляе-тся ток, который снижает базовый тсж транзистора 4, В результате этого кол лекторный ток транзисгора 4 фиксирувтся н уровне д Щэ.Фт R где 3fc - TQK коллектора; Vsa напряжение база-эмиттер; R - вел15чина резистора фт фиксирующий ток, и весьма незначительно завис гг от величи- ны напряжения питания и сопротивления на грузки. При этом транзистор 5 закрыт, так как электрггческий потенциал на его базе Н1гже потенциала базы транзистора 3 на ве личину падения напряжения на открытом диоде 9. При подаче логического сигнала уровнем р гвным О на вход 13 через резистор 6 ереход б/км-ЭМИгт(,р ifituoncTOpa 2 протекает ок, насыщаюшпй входной транзистор 2, котоый запирает траноистор 4 и диод 9, но в том случае открьшается TpafiaHCTOp 3, фикация коллекторного, тока которО оопределяетя аналогично, указанному выше. При подано на вход 14 сигнала, соответству.гощего логическому , транзисторы 2 и 3 закрыты независимо от наличия сигналов на входе 13. В связи с тем, что транзисторы 4 и 5 работают так источнтш тока, их режимы нэ зависят от изменения электрического потенциала коллекторов в щироких пределах, в рёзул1зтате чего синфазная помеха, значительно превышающая выходное напряжен1 е, не искажает информацию, а сочетание диф ференциальной схемы включения транзисторов 4 и 5 с ненасыщенным режимом работы и небольщим количеством активных элемер - тс© обеспечивает минимальное время задержки сигнала. Формула изобретения Устройство преобразователл однофазного логического сигнала в парафазный ток, содержащее логический элемент 2И-ИЛИ, состоящий из двух входных многоэмиттер- ных транзисторов, базы которых через резисторы соединены с первой ши.ной источншсом питания, а коллекторы соединены с базами выходных транзисторов, коллекторы которых через резисторы соединены с первой шиной источника питания, а эмиттеры соединены собой и через токозадаюишй резистор подключены к второй шине источника питания, причем один эмиттер первого многоэмиттерного транзистора подключен к первому источнику входного сигнала, два других эмиттера соединены между собой, с тремя эмиттерами второго многоэмиттерного транзистора и со вторь м источником входного сигнала, отличающееся тем, что, с целью повышения быстродействия и помехоустойчивости, в него введен диод и дополнительный транзтгстор, база которого соединена с эмиттерами выходных транзисторов логического элемента 2И-ПЛИ, эмиттер-с второй шиной источника питания, а коллектор - с четвертым эммитером второго из упомянутых многоэммитерных транзисторов непосредственной через диод-с четвертым эммитером первого многоэммитерного транзистора. 04

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ | 2022 |

|

RU2782474C1 |

| Интегральный динамический элемент | 1971 |

|

SU559381A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ЦИКЛИЧЕСКОЙ ИНВЕРСИИ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ (ВАРИАНТЫ) | 2024 |

|

RU2835664C1 |

| Одновибратор | 1978 |

|

SU733088A1 |

| Интегральная логическая схема | 1979 |

|

SU1001480A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ «И—ИЛИ—НЕ» и «И-ИЛИ» | 1970 |

|

SU260680A1 |

| Быстродействующий помехоустойчивыйлОгичЕСКий элЕМЕНТ и-или/ и-или-HE | 1978 |

|

SU849488A1 |

| Элемент троичной логики | 1980 |

|

SU892729A1 |

| Многопороговый логический элемент | 1983 |

|

SU1132366A2 |

| Многоканальный селектор импульсов по длительности | 1972 |

|

SU444313A1 |

Авторы

Даты

1977-08-25—Публикация

1976-04-23—Подача