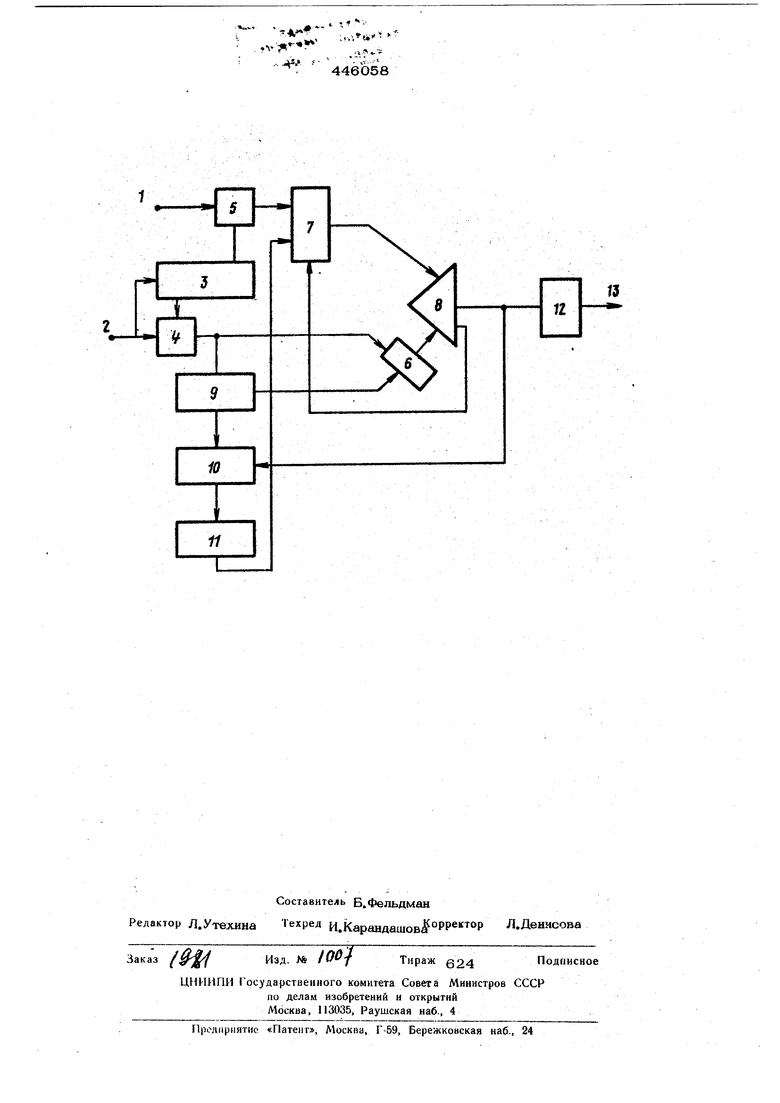

Изобретение относится к области вычисл тельной техники и может быть использовано при построении арифметических устройств. Известны устройства для ускорения деления, позволяющие ускорить двоичное деi пение в к раз с использованием для этого добавочного оборудования объемом порядка к ; Резкий рост количества оборудования при реализации ускоренного деления делает эти методы непригодными при сколько-ниI будь значительных величинах к. Известны алгоритмы ускоренного деле : ння в знакоразрядном представлении в - р, ичной системе, основанные на умножений : делимого и делителя на специально подобранные множители, зависящие от величины делителя таким образом, чтобы значения делителя оказались в диапазоне: ; ;i, р() p(p.i)J алгоритмы обладают недостаточным быстродействием. Целью предлагаемого изобретения является увеличение производительности вычислений. Предложенное устройство для ускоренно1-о деления отличается от известных тем, что с целью увеличения производительности,оно дополнительно содержит два блока умножения на цифру, блок анализа первой цифры делителя и операционное устройство. Выход последнего соединен с блоками умножения, формирования текущего остатка и формирования частного, а входы с выходом блока формирования текущего остатка и с выходами к старщих разрядов делителя, -к младщих разрядов которого соединены с другим входом блока умножения. Входы i блоков умножения на цифру подключены соответственно к щинам делимого и делителя, а управляющие входы этих блоков соединены с выходами блока анализа первой цифры делителя, вход которого соеди нен с шиной делиаеля. На чертеже приведена схема устройства. Оно содержит шину 1 делимого, шину 2 делителя, подключенную к блокам 3 и 4

анализа первой цифры делителя и умноже ния на цифру соответственно, блок 5 умножения на цифру, регистр 6 к старших разр5адов делителя, блок 7 формирования текущего остатка, выход которого соединен с. входом операционного устройства 8, регистр 9 младших разрядов делителя, выходы которго соединены с входами блока 10 умножения кодов, блок 11 накопления частичных произведений, блок 12 формирования частного и выходную шину 13

частного.

Блок анализа первой цифры делителя 3 проверяют ее на равенство единице. Блоки 4 и 5 обеспечивают учетверение делимого и делителя, если первая цифра делителя равна единице, в противном случае оба опоранда остаются без изменений. Регистр 6 сохраняет к старших разрядов делителя, блок 7 - старший разряд делимого на первом шаге или текущего остатка в последующем. Сигналы с блоков 6 и 7 поступают на вход операционного устройства 8. Число анализируемых комбинаций регистра 6 может быть ограниченным.

Устройство 8 вырабатывает двухзначный код Si , используемый для формирования частного в блоке 12 и для умнойсения на младшие разряды делителя в блоке 10. Кроме этого, устройство 8 вырабатывает выражение типа

:S,cA -i-10 cA2

(где в - старший разряд делимого или

текущего остатка; сЛ И сЛ„- два старших разряда делителя),

которое сразу используется в блоке форь. мирования текуш его остатка для ускорения операции.

Использование учетверения позволяет резко упростить операционное устройство за счет устранения значений делителя в диапазоне от 1,666. . до 1,333.. Кроме чхэго, умножение знакоразрядного кода на 4 не требует последующей коррекции.

Цифры частного определяются по формуле;-

6

(Е(:)

ю-сЛ

- код, используемый для формиро1

где вания частного; Е - наибольшее целое число, Meiib шее содержимого скобки; В,(Л соответствующие разряды делимого (текущего остатка) и Де лителя.

Частичные произведения накапливаются в блоке 11 и вместе с результатом, полученным в операционном устройстве, вычитаются из текущего остатка в блоке

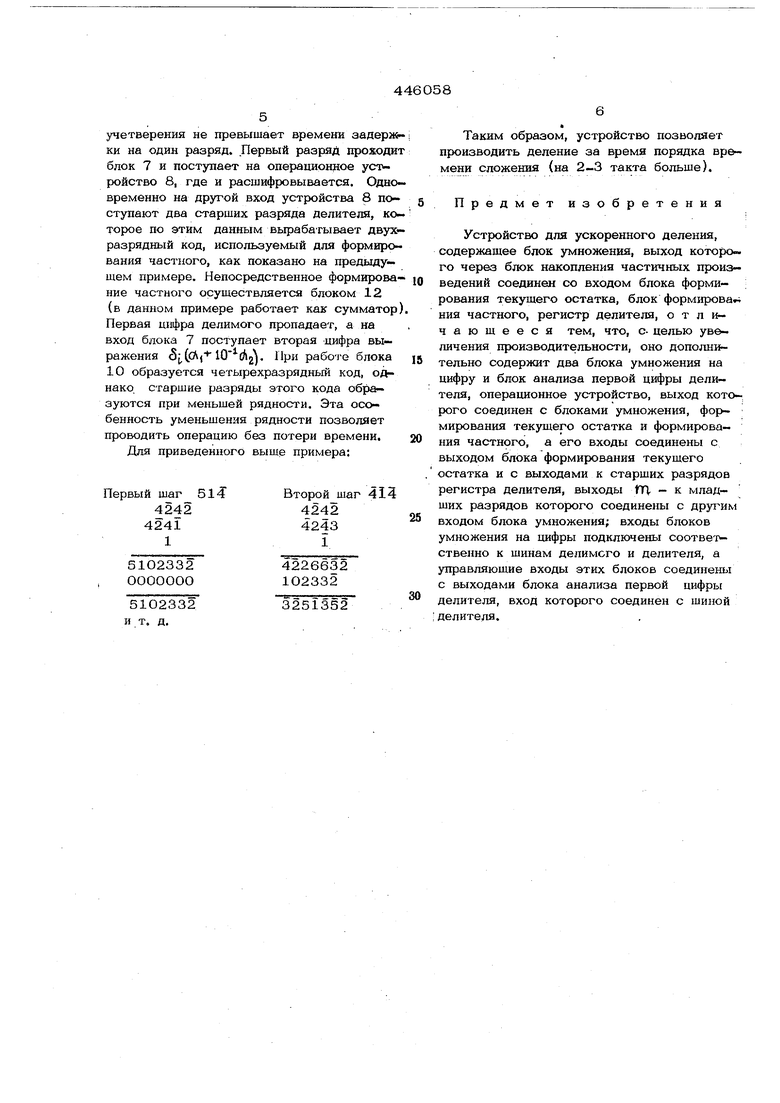

7Для примера 534542 : 232124

имеем

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел | 1990 |

|

SU1735844A1 |

| Устройство для деления чисел | 1985 |

|

SU1429109A1 |

| Устройство для деления | 1991 |

|

SU1783523A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018934C1 |

| Устройство для деления чисел | 1986 |

|

SU1417010A1 |

| Устройство для деления чисел | 1980 |

|

SU857977A1 |

| Устройство для деления | 1985 |

|

SU1282117A1 |

| Устройство для деления | 1985 |

|

SU1265763A1 |

| Устройство для деления чисел | 1985 |

|

SU1247862A1 |

| Устройство для деления | 1990 |

|

SU1803913A1 |

ЗО15012 533132

Устройство работает следующим образом.

Рассмотрим для простоты случай, когда делитель уже расположен в блоках 6 и 9.

Первый разряд делимого поступает на вход блока 5. Он учетверяется или проход дит без изменений в зависимости от значения старшего разряда делителя. Время учетверения не превышает времени задерж ки на один разряд. Первый разряд проходи блок 7 и поступает на операционное уст ройство 8, где и расшифровывается. Одно временно на другой вход устройства 8 по ступают два старших разряда делителя, ко торсе по этим данным вьфабатывает двух разрядный код, используемый для формиро вания частного, как показано на предыдущем примере. Непосредственное формирова ние частного осуществляется блоком 12 (в данном примере работает как сумматор Первая цифра делимого пропадает, а на вход блока 7 поступает вторая цифра выражения 5,(Л2). l- работе блока 10 образуется четырехразрядный код, однако, старшие разряды этого кода образуются при меньшей рядности. Эта особенность уменьшения рядности позволяет проводить операцию без потери времени. Для приведенного выше примера: Второй шаг 414 Первый шаг 51-С 4242 4242 4241 1 4243 1 51О2332 4226632 102332 ООООООО 5102332 3251352 и т. д. Таким образом, устройство позволяет производить деление за время порядка времени сложения (на 2-3 такта больше). Предмет изобретения Устройство для ускоренного деления, содержащее блок умножения, выход которого через блок накопления частичных произведений соединен со входом блока форми- ; рования текущего остатка, блок форм1фова ния частного, регистр делителя, отличающееся тем, что, с- целью увеличения производительности, оно дополнительно содержит два блока умножения на цифру и блок анализа первой цифры делителя, операционное устройство, выход которого соединен с блоками умножения, формирования текзтцего остатка и формирования частного, а его входы соединены с выходом блока формирования текущего остатка и с выходами к старших разрядов регистра делителя, выходы frv - к младших разрядов которого соединены с входом блока умножения; входы блоков умножения на цифры подключены соответственно к шинам делимого и делителя, а управляющие входы этих блоков соединены с выходами блока анализа первой цифры делителя, вход которого соединен с шиной делителя.

., ;, 446O58

,

Авторы

Даты

1974-10-05—Публикация

1971-02-11—Подача