1

Изобретение относится к об- I ласти аналоговой вычислительной техники и может быть использовано при моделировании на универсальных АБМ систем, содержащих звенья временного запаздывания ( в том числе и управляемого), в также при построении блоков запаздывания.

Известны устройства, имитирующие запаздывание путем воспроизведения с помощью четырех операционных усилителей первых трех членов разложения требуемой передаточной функции в ряд Паде. При этом часть передаточной функции звена запаздывания, предполагающая наличие дифференцирования, воспроизводится с помощью разности двух передаточных функций, что позволяет избежать явного дифференцирования.

Известны устройства указанного типа, обеспечивающие воспроизведение регулируемого запаздывания.

Однако в существующих устройствах вследствие использования раз1ности двух передаточных функций для достижения необходимой точности требуется строгий баланс ряда элементов схемы, нарушение которого приводит к существенным искажениям не только фазовой, но и амплитудной частотных характеристик устройства в определенных диапазонах частоты и амплитуды входного сигнала. Эти показания усугуб0ляются в схемах с управляемым запаздыванием.

Целью изобретения является повышение точности и имитации запаздывания за счет перестройки схемы

5 воспроизведения известной передаточной функции.

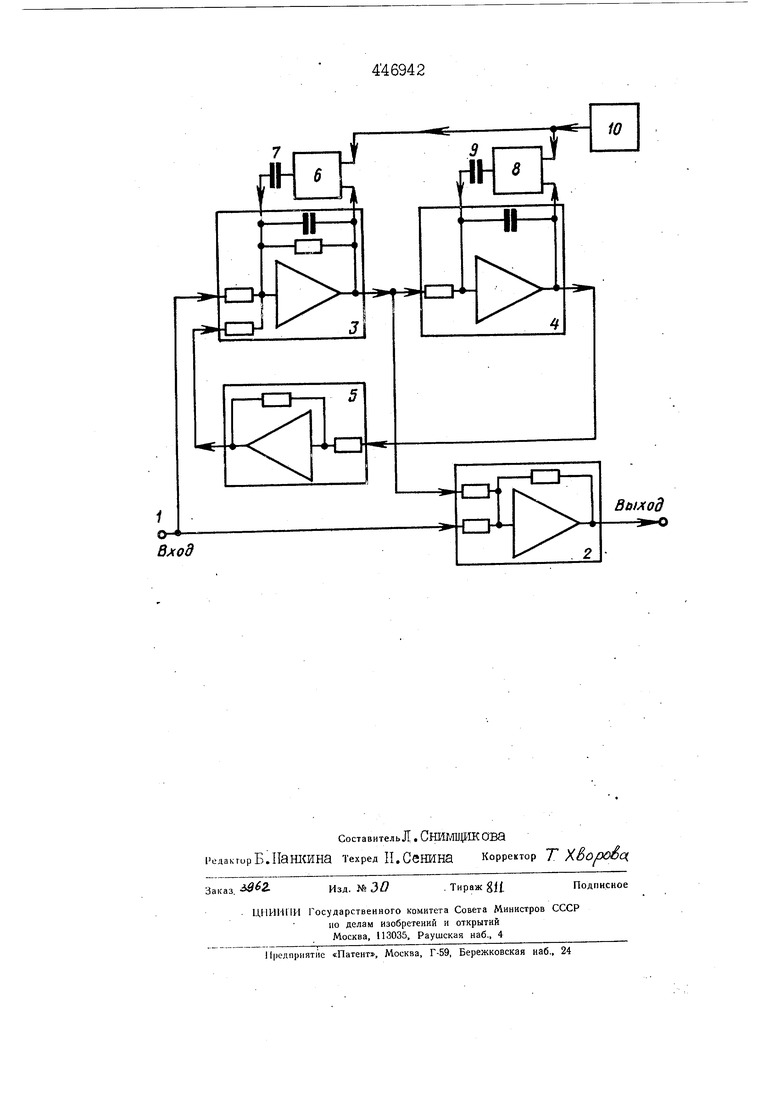

Указанная цель .достигается непосредственным воспроизведением части передаточной функции звена запаздывания путем соединения выхода апериодического звена с одним из входов сумматора. При этом в отличие от известных схем отсутствуют непосредственные связи входа Iустройства со входом интегрирующего звена и выхода последнего со вхо дом сумматора. Помимо повышения точ ности воспроизведения запаздывания это несколько упрощает схему устройства, уменьшает число и упрощает некоторые из уравнений, связывающих между собой ее параметры. На чертеже показана блок-схема устройства. Входная клемма I устройства соединена со входом сумматора 2 и со входом апериодического звена 3. Во внешнюю обратную связь апериодического звена между его выходом и одним входом включены последовательно соединенные интегратор 4 и инвертор 5. Все указанные звенья (апериодическое, интегрирующее, инвертор и сумматор) собраны по известным схемам на операционных усилителях постоянного тока, обладающих свойством инвертирования знака. Выход апериодического звена соединен непосредственно со вторым входом сумматора 2, В цепь обратной связи апериодического звена включена дополнительная параллельная ветвь, состоящая из последовательно соединенного множительного знака 6 и конденсатора 7; аналогичная ветвь, состоящая из множительного звена 8 и конденсатора 9 используется в цепи обратной связи интегратора. Вторые входы множительных звеньев соединены с источником 10 управляющего сигнала. Передаточная функция устройства при отключенном входе сумматора и постоянном управляющем сигнале имеет вид: i(f} аур + 0-3 р а, -постоянные коэффициенты, -оператор дифференцирования. Для реализации ее не потребовалось ни непосредственного дифференцирования, ни вычитания одной передаточной функции из другой, что обеспечивает в реальных условиях более точное выполнение определяемых ею преобразований сигнала по сравнению с известными устройствами. При соответствующим образом выбранных параметрах схемы общая передаточная функция предлагаемого устройстваW(P)( 12 2 где К -методическая ошибка; Т- время запаздывания, обеспечивает воспроизведение на его выходе сигнала с запаздыванием на величину 7 относительно входа с известной методической ошибкой. Величины постоянных времени апериодического звена и интегратора, а следоательно, и величина запаздывания Т, являются линейными функциями управляющего сигнала, поступающего с источника 10 на соответствущие входы множительных звеньев 6 и 8, ПРЕДМЕТ ИЗОБРЕТЕНИЯ Устройство запаздывания, содержащее сумматор и апериодическое звено, входы которых соединены с входной клеммой устройства, в обратную цепь апериодического звена включены последовательно соединенные интегрирущее звено и инвертор, блок управления, состоящий из множительных звеньев, включенных в обратную цепь апериодического звена и интегратора, а управляющие входи соединены с источником управляющего сигнала, отличающееся тем, что, с целью повышения точности работы устройства, выход апериодического звена подключен ко входу сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для защиты электропривода постоянного тока от перегрузок | 1988 |

|

SU1601688A1 |

| Устройство автоматического управления процессом обогащения | 1979 |

|

SU971473A1 |

| Датчик углового ускорения | 1975 |

|

SU523356A1 |

| Частотно-регулируемый электропривод | 1979 |

|

SU866681A1 |

| Устройство для автоматическогоупРАВлЕНия Об'ЕКТАМи C TPAHC-пОРТНыМ зАпАздыВАНиЕМ | 1979 |

|

SU796789A2 |

| Нелинейное корректирующее устройство с фазовым опережением | 1988 |

|

SU1718182A1 |

| УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ ХАРАКТЕРИСТИК СОЛНЕЧНЫХ БАТАРЕЙ | 2008 |

|

RU2357264C1 |

| Устройство для определения параметров объекта | 1987 |

|

SU1446602A1 |

| Самонастраивающаяся система комбинированного регулирования | 1986 |

|

SU1339494A1 |

| Система управления для объектов с запаздыванием | 1984 |

|

SU1239686A1 |

Авторы

Даты

1974-10-15—Публикация

1972-06-27—Подача