1

Изобретение относится к устройствам автоматики и вычислительной техники и может найти применение, например, для воспроизведения функций, определенных на конечном интервале аргумента. Результат аппроксимации получается в виде функционального напряжения, пропорционального аппроксимируемой функции.

Известен аппроксиматор, содержащий реверсивный счетчик, дешифратор, сдвигающий регистр и аналоговый сумматор, однако ему свойственна низкая точность представления функций, обусловленная ступенчатым характером функций, используемых для аппроксимации.

Предлагаемый аппроксиматор дпя повышения точности содержит цифро-аналоговый множительный блок, второй аналоговый сумматор и второй сдвигающий регистр, вход которого соединен с третьим входом и первым выходом реверсиБнсг;о счетчика, а выход через второй аналоговый сумматор подключен к первому входу цифро-аналогового множительного блока, второй вход которого соединен со вторым выходом реверсивного

счетчика и входом дешифратора, а третий вход соединен с выходом первого, аналогового сумматора; выход дифро-аналсжого множительного блока подключен к выходу

5 аппроксиматора.

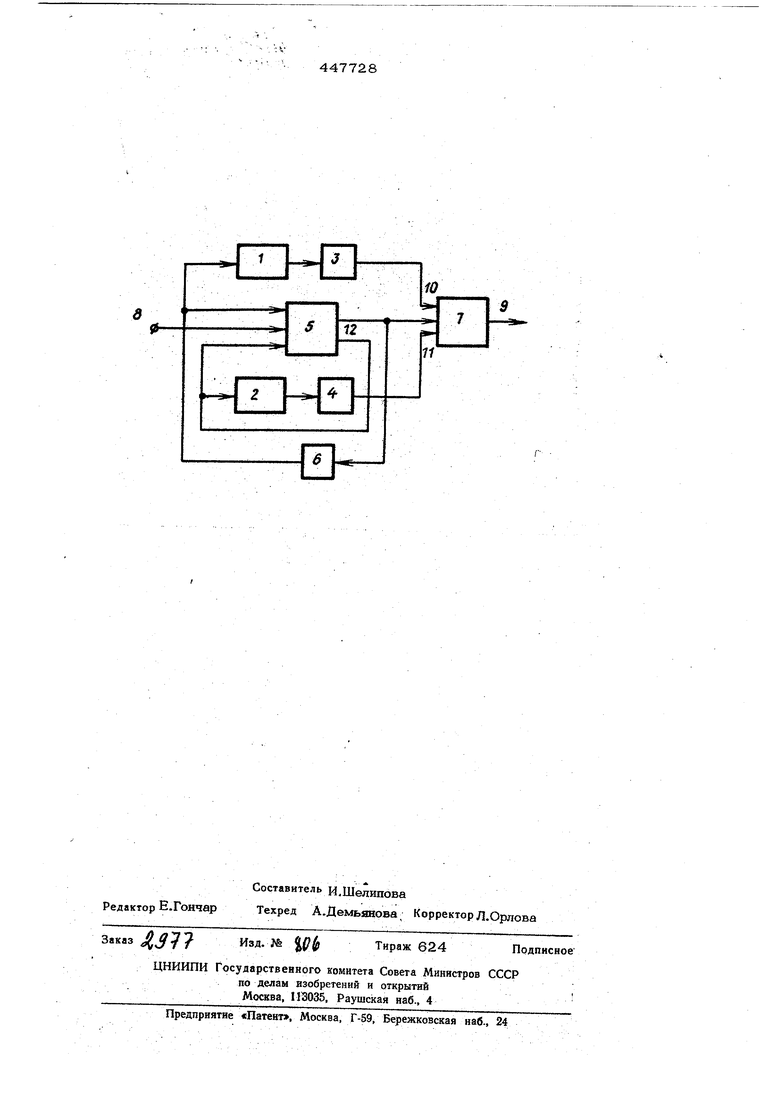

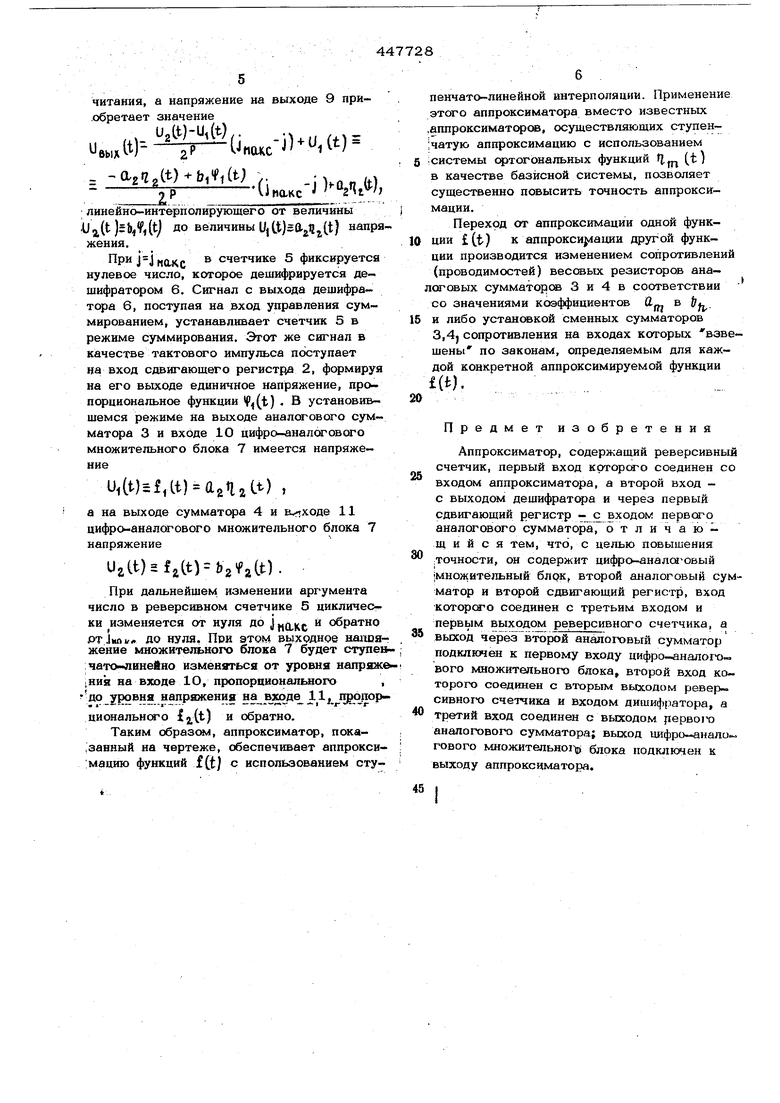

На чертеже представлена функциональная схема аппроксиматора.

Он содержит сдвигающие регистры 1 и 2, аналоговые сумматоры 3,4, реверсивный

10 счетчик 5 импульсов текущего значения аргумента, дешифратор 6 нулевого кода и щ фро-аналоговый множительный блок. 7. Вход 8 импульсов текущего значения аргумента t и выход 9 аппроксиматора, аналсг

15 вые входы 1О и 11 множительного блока 7 и выход 12 импульса переполнения счетчкка 5.

Сдвигающий регистр 1 предназначен для 20 формирования функций, имеющих форму прямоугольных импульсов длительностью ut . ч/и() и выходом связан с входом аналого вогб сумматора 3, а входом - с выходом ; ,, дещифратора 6 и входом управления сум25 . мнрованием реверсивного счетчика 5. Сдвигающий регистр 2 предназначен д формирования ступенчатых функций ,(.)-reciit J, , m-m-, ,2, ..., N-1 , (где л - порядковый номер, N - число интервалов аппроксимации) и выходом свя .„„.„„„,. зан с входом аналогового сумматора 4, а входом - с выходом импульса переполнени и входом управления вычитанием реверсив ного счетчика 5. Аналоговые сумматоры 3 и 4 предназначены для вессжого суммирсжания функ ций l(t} и ) с целью получения ступенчатых функций ijC) , 5шляющихся парой функций, аппроксимирующий функцию /t) Выходы сумматора 3 и 4 связань с аналоговыми входами 10 и 11 цифро-ан логового множительного блока 7. Цифро-аналоговый множительный блок используется в качестве линейного интерполятора и цифровым входом связан с выходом реверс1шного счетчика 5 и входом дешифратора 6 нулевого кода. Выход цифр аяало1ового множительного блока 7 подключ к вьЕходу 9 аппроксимирсванной функции. Реверсивный счетчик 5 предназначен для счета импульсов текущего значения аргумента, поступающих на .его счетный вход 8. Единичный выход триггера старшего разряда реверсивного счетчика 5 является одновременно выходом импульса переполнения при работе счетчика в режиме суммирования. По мере заполнения счетчика 5, работающего в режиме суммирования, импульсами текущего значения аргумента, число в нам увеличивается, стремясь к значению .- 1 напряжение на выходе 9 соответственно изменяется по закону u.,,.,,, , . .р достигая при J jMaKC -l величины s,,tt))-U.(t)«U,(t), jMib) - дискретность цифро-а„,„а-„во.о „реобразованн, (цв,а к.„аянТ,° S:7) При возрастании J, от нулевого до |максимального значений напряжение на выходе цифро-аналогового множительного блока 7 является линейно-интерполирующим (точнее, ступенчатолинейным интерполирующим) от Ц (t) до UnCtj напряжением, а само устройство 7 работает в режиме линейного интерполятора. По аналоги1а можно показать, что при последовательном уменьшении числа, содержащегося в счетчике 5, от максимата ного до нуля (т.е. при работе счетчика 5 в «. н наи1л-е л;четчика в режиме вычитания) цифро-аналоговый множительный блок 7 работает также в режиме линейнсго интерполятора, вырабатьюая линейно-интерполирующее от ) ДО U (i) напряжение. Аппроксиматор работает следующим образом. Когда в счетчике S имеется нулевое число и он установлен в режим суммирования, в ячейке перв.ого разряда сдвигающего регистра 1 установлена единица, а в сдвигающем регистре 2 все разрядные ячейки установлены в нулевое состояние. При этом на выходе регистра 1 имеется единичное напряжение, пропорциональное j(tj-1 J на выходе аналсгсшого сумматора 3 и входе 10 цифро аналса сжого множительного блока 7 имеется напряжение Ц (i-J , пропорциональное текущему значению функции f(t) ; на выходе регистра 2 все функции ff,(t):0 н выходе аналогового сумматора 4 к аа входе 11 цифро-аналогового множительного блока 7 имеет ся напряжение U (.1) , пропорциональное текущему значению функции о it) , а на выходе 9 аппроксиматора напряжение y6b.x(t)u,ct)f(t),it). При поступлении на вход 8 импульссж текущего значения аргумента, число J в счетчике 5 увеличивается, а на выходе 9 имеем интерполирующее напряжение ,, U2(t)-u,(t).fr,f,CtH,tt;tt; + ) , При JMQ-KC напряжение на выходе 9 e,,x{t) U2(t)s|2Ct) f,(t} , в счетчике 5 наступает переполнение. мпульс переполнения с выхода 12 постуает на вход управления вычитанием .счет ика 5 и в качестве тактсюсзго импульса а вход сдвигающего регистра 1, фиксируя „- -.----, ППГ-ттапиглч Ш™Г. прв э „мкГГ 7, tjT|«r С поступлением и рии импульсов текущего значТнияТгу ента счетчик 5 работает Р

чихания, а напряжение на выходе 9 приобретает значение

u...c-ibMt)V

,.Vt;.(..j,,,,

. -М-.--.., ,п Т1М1-ГМ11Г г,....,.;,

линейно-интерполирующего от величины

Ua(t)bi1,(t) до величины Ц С)(1) напряжения,

При),(кс счетчике 5 фиксируется нулевое число, которое дешифрируется дешифратором 6. Сигнал с выхода дешифратора 6, поступая на вход управления суммированием, устанавливает счетчик 5 в режиме суммирования. Этот же сигнал в качестве тактового импульса поступает на вход с;шигаюшего регистра 2, формируя на его выходе единичное напряжение, пропорциональное функции 4(t) . В установившемся режиме На выходе аналогового сумматора 3 и входе 10 цифро-анадсжового множительного блока 7 имеется напряжение

(t) f,tt) U2ll2C)

а на выходе сумматора 4 и 11 цифро-аналогового множительного блока 7 напряжение

UaCt)).jCt).

При дальнейшем изменении аргумента число в реверсивном счетчике 5 цикличесгки изменяется от нуля до JMQ, и обратно

PTJiuiv до НУЛЯ. Пен этом выходное ншшяжение множительного блока 7 будет ступе

: чато линейно Измен1ггься от уровня напряжеiНИИ на входе 10, пропорционального,

до уровня напряжения на входе 11, пропор

. ,--,-------.--„- --ч l,f,f.

циональнсго ) и обратно.

Таким обраасии, аппроксимат ф, пока.занный на чертеже, обеспечивает аппроксимацию функций f (t) с использованием ступенчато-линейной интерполяции. Применение этого аппроксиматора вместо известных .аппроксиматорсю, осуществляющих ступен чатую аппроксимацию с использованием

-системы с тогональных функций Ifn (t) в качестве базисной системы, позволяет существенно повысить точность аппроксимации.

Переход от аппроксимации одной функции (t) к аппрокси{лации другой функции производится изменением сопротивлений (провод им остей) весовых резисторов анаоговых сумматоре 3 и 4 в соответствии со значениями коэффициентов и в 4,.

и либо установкой сменных сумматоров

3,4j сопротивления на входах которых взвешены по законам, определяемым для каждой конкретной аппроксимируемой функции

т.

Предмет изобретения

Аппроксиматор, содержащий реверсивный счетчик, первый вход крторся о соединен со входом аппроксиматора, а второй вход с выходом дешифратфа и через первый сдвигающий регистр - входом первого аналогового сумматора, отличающийся тем, что, с целью повышения

;Точности, он содержит цифро-аналса овый множитёльный бл9к, второй аналоговый сумматор и второй сдвигающий регистр, вход которого соединен с третьим входом и первь1М вьгходо л реверсивного счетчика, а

выход через второй аналоговый сумматор подключен к первому входу цифро-аналогового множительного блока, второй вход которого соединен с вторым выходом реверсивногю счетчика и входом дишифратора, а

третий вход соединен с выходом рервого аналогового сумматора; выход иифро-анало гового множительно - блока подключен к выходу аппроксиматора.

I

а

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ АППРОКСИМАЦИИ ФУНКЦИЙ, ЗАДАННЫХ ЦИФРОВЫМ КОДОМ | 1971 |

|

SU427346A1 |

| Устройство для воспроизведения переменных во времени коэффициентов | 1981 |

|

SU1005087A1 |

| УСТРОЙСТВО для КУСОЧНО-КВАДРАТИЧНОЙ АППРОКСИМАЦИИ ФУНКЦИЙiS^,fi-\?-t "JP'ltpT^^ФУ-ЗД и ;i,'';^r «^'.) | 1973 |

|

SU408329A1 |

| Вычислительное устройство | 1981 |

|

SU1001114A1 |

| Устройство для воспроизведения переменных во времени коэффициентов | 1980 |

|

SU894737A1 |

| УСТРОЙСТВО ДЛЯ АППРОКСИЛ1АЦИИ ФУНКЦИЙ, ЗАДАННЫХ ЦИФРОВЫМ КОДОМ | 1972 |

|

SU419920A1 |

| Функциональный преобразователь | 1980 |

|

SU894748A1 |

| Гененратор функций | 1973 |

|

SU475614A1 |

| ПОЛИНОМИАЛЬНЫЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1972 |

|

SU425191A1 |

| УСТРОЙСТВО для КУСОЧНО-КВАДРАТИЧНОЙ АППРОКСИМАЦИИ ФУНКЦИЙ | 1973 |

|

SU374622A1 |

Авторы

Даты

1974-10-25—Публикация

1973-02-12—Подача