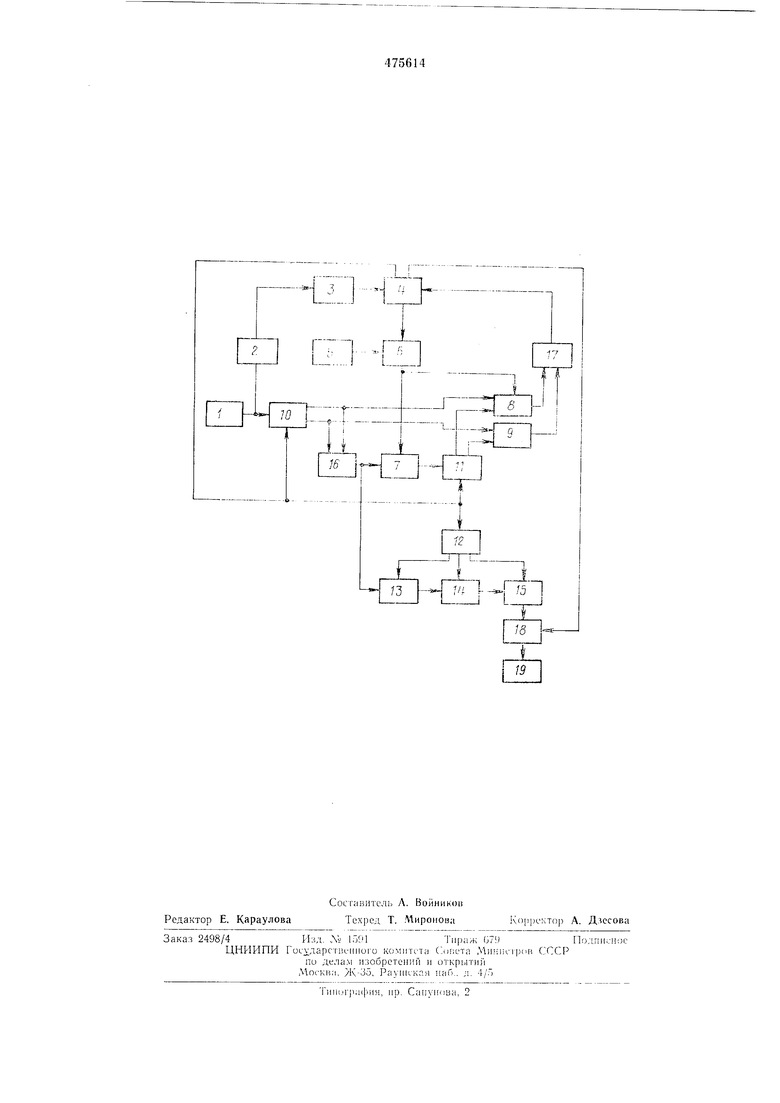

3 делитель 14 количеетва имиульеов, сумматор 15, схемы «ИЛИ 16 и 17, схема переноса 18, преобразователь «код- напряжение 19. Прпнцнп действня генератора заключается j еледуюи;ем. Пусть необходимо с()ормировать напряжение L(1). представляющее собой элементарную (|)упкни1о временн. В генераторах, основанных па ;1реобразованпи кода в аналог, в дейетвнтельпостн формируется ступенчатая крнвая L{1), б,1нзкая к заданной, п)ичем U(t,)/,-N,,(1) где и(ii) -днекретные значення выходного напряженияпреобразователя «код--напряжение в точках анпрокснмацнн ij, K,i - крутизна характернстикн выход- вход преобразователя «код-- нанряженне ;Л; - код пли числовой эквивалент формнруемого напряжения в точках аппроксимации. Код Л ,- связан с кодом tii аргумента А формируемой функции U(ii) разложением по степеням П1 Лг 2 щт , где т - чнсло членов ряда; а,- - коэффпциенты ряда, опреде.теипые по величине и знаку для каждой элементарной функции; некоторые из этих коэффициеитов могут быть равны нулю, например, при формировании напряжения L(t) 6макс51П (л1 равны нулю чбтные коэффициенты, а при формировании сигнала (г )0максС05 ш равиы нулю нечетные коэффициенты; Л; - код аргумента Xi в точках аппроксимации ti, нричем (р - величина, обратная дискретности представления аргумента в числовой форме). Для гармонических функций для экспоненциальной Xi a.ti и т. д. Очевидно, значения аргумента А ,- н их коды п, с точки зрения уирощения схемной реализации целееообразно задавать нх приращепнями:ii п, 2 , 2 р-(3) 1 Если обеспечить A/ZI -: A/Za - ... -: ДЯр :...:- . -; COOSt, Т. е. точки апироксимации выбрать равноотстоящими, то П1 - /А/г. Точки аннроксимации задаются генератором имиульсов 1, делителем частоты 2 и распреде4 .лггелем импульсов 3. В моме1ггы /, импульсы с 15ы. расп)еделителя 3 поступают в блок у|1р;11 леиия 4, который синх1)онизирует работу всех узлов генератора. Б иеходиом состояннн код Л/г записывается в регистр кода 5. По сигиалу блока управления 4 код через схему переноса 6 заиисывкется в множительный блок 7 и в ревереивпы11 счетчик 8 в дополнительном коде. Показан1 я счетчика 9 нулевые. Затем блоком уп1)ав.:е11ня 4 выдается сщ-пал на ключи 10, 11 и ком.мутатор 12 коэффициентов деления. Трехпозиционные ключи 10 и 11 устанавливаются в состояипя, при которых счетчик по входу суммироваипя подключается к генератору пмпульсов 1, а счетчик 9 по входу вычитания--к 1 ыходу множительного блока 7. Коммутатор 12 служит для уиравлеиия ключом 13, для измеиения коэффициента деления дсл1ггеля 14 количеетва импульсов и для уи|)авлення режимом работы сумматора 15 следу1они1М образом. 13 открывается выходным сигналом коммутатора 12, если , и закрывается, еели а/ 0; коэффициеит делеиия делителя 14 устанавливается равным gi - , если , и не пзмепяепся, если Режим работы еумматора 15 (вычитание или сложение) оп1)еделяется зиаком щ. Пуст) , тогда сигиалом коммутатора 12 ключ 13 открывается, в делитель 14 вводится коэф(|)ициеит делеиия gi, и еумматор 15 уста11авлнг;ается в режнм суммировання. Через ключ 10 имнульсы с генератора 1 ноCTynaiOT на счетчик 8 н через схему «ИЛИ 16 па мпож1ггельный блок 7 и через открытый ключ 13 на делитель 14 и дальше на сумматор 15. При постунлении на счетчик 8 числа импульсов «1 на его выходе появляется импульс переполнения, который через схему «ИЛИ 17 поступает в блок управления 4. К этому мо.мепту ij счетчик 9 на вычитание е выхода блоча / : оступаст п- импульсов, а в сумматор I - :гК) число им 1ульсов -i- airt|. Ьлок уиравлення 4 вырабатывает унравляющий сигнал, которым состоянне ключей 10 и 11 изменяется на протнвоноложиое и тем самым счетчик 9 по входу сложения иодключается к генератору 1, а счетчик 8 ио входу вычитания - к блоку 7; нз.мепяется состояние коМ Мутатора 12, иосредетвом которого, в свою очередь, управляются элемеиты 13, 14 и 15. Так, если , к.тюч 13 закрывается и запрещает нрохожденпе п.м.пульсов на делитель 14. Имнульсы с геиератора 1 через ключ 10 поступают на счетчик 9 на суммирование и через схе.му «ИЛИ 16 на блок 7. При ноетуилепии п имиульсов на счетчик 9 на его выходе появляется нмпулье переполнения, который через схему «ИЛИ 17 вводится в блок управ5лспня 4. К этому моменту в счетчик 8 с блока 7 поступает па вычптанпг чис.ю импульсов «j. Показания сумматора 15 не изменяются. Уиравляющин сигнал блока управления 4 выполняет следующие операции: возвращает ключи 10 и 11 в предыдущее состояние; воздействует на коммутатор 12, переключая его в следующее состояние. При этом, если . сигналом коммутатора 12 ключ 13 открывается, коэффициент деления делителя 14 устаиав1ливается равным 3 -. н су.мматор 1о устаанавливается в режим вычитания. В дальиейшем работа схемы повторяется, Первый цикл работы генератора, состоящий в получении кода Ai формируемой функции U (t) в первой точке аппроксимации ti, заканчивается после получения m слагаемых суммы (2), определяе.мым заданным числом членов разложения. В этот момент с блока управления 4 поступает сигнал схему переноса 18 для переноса кода .Vi с сумматора 15 в нреобразователь «код - напряжение 19, где формируется первая ступенька выходного напряжения. Второй и последующий циклы работы схемы задаются распределителем импульсов 3, выходные импульсы которого соответствуют точкам аппроксимации -tz, tg, ..., ti, ..., tr (г- число участков аппроксимации). Отличие каждого цикла от предыдущего состоит лишь в том, что с регистра кода 5 в множительный блок 7 и реверсивный счетчик 8 вводится новый код аргумента: «2, , , ь Если в разложении присутствует слагаемое , то оно вводится непосредственно в сумматор 15 перед каждым циклом формирования очередной ступеньки U(ti)После получения г импульсов с распределителя 3 иа выходе преобразователя 19 будет сформирована ступенчатая кривая L(ti, определяемая вы)ажением (1) и моделирующая заданную кривую U(t. Если необходимо формировать периодическую функцию U(i), то работа схемы повторяется. Предмет изобретения Генератор функций, содержащий последовательно соединенные генератор импульсов, делитель частоты, распределитель импульсов и блок у:1равления. : реобразователь «код - иа:)яжение, подключенный через первую схему переноса к выходам сумматора, два реверсивных счетчика, регистр кода, схемы «ИЛИ, ключи и множительный блок, отличающ 1 и с я тем, что, с целью расширения класса решаемых задач, он содержит делитель количества им:1ульсов и коммутатор коэфф1щиентов делення, первый, второй и третий выходы которого соединены соответственно с первыми входами первого ключа, делителя количества импульсов и сумматора, вход кото)ого подключен к выходу первого ключа через делитель количества импульсов, второй вход первого к.поча соединен не:1осредственно с входом множительного блока и через первую схему «ПЛИ с выходами второго ключа и суммирующими входами реверсивных счетчиков, выходы которых через вторую схему «ПЛП соединены с входом блока управления, а числовые входы поразрядно подключены к числовым входам множительного блока н через вто|ПК) схему :iepeHoca, у;1равляющий вход которой соедпн.ен с нервым выходом блока управления, к выходам регнстра кода, выход множительного блока соединен с первым входом третьего ключа, второй вход которого соединен с входом коммутатора коэффициентов деления, вторым входом второго ключа и с вторым выходом блока управления, третий выход которого соедипен с у: равляюпи1м входом :iepвой схемы :1ереноса, первый н BTOpoii выходы третьего ключа подключены соответственно к Bbi4HTaioHUiM вxoдa riepBoro н второго реверсивных счетчиков, а первый вход второго ключа соединен с выходом генератора им:1ульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ФАЗОМЕТР | 1973 |

|

SU385236A1 |

| Устройство для вычисления функций у=aRcSINx и у=aRccoSx | 1980 |

|

SU935949A1 |

| Устройство для цифрового функционального преобразования | 1981 |

|

SU985792A1 |

| Функциональный преобразователь | 1976 |

|

SU610137A1 |

| Устройство для определения характеристик случайного процесса | 1983 |

|

SU1100628A1 |

| Цифровой генератор спектра фурье | 1973 |

|

SU446063A1 |

| Преобразователь кода угла в коды синуса и косинуса | 1977 |

|

SU684554A1 |

| Цифровое устройство для вычисления гиперболических функций | 1977 |

|

SU684553A1 |

| АДАПТИВНЫЙ ВРЕМЕННОЙ ДИСКРЕТИЗАТОР | 2015 |

|

RU2583707C1 |

| Устройство для вычисления элементарных функций | 1982 |

|

SU1049901A1 |

Авторы

Даты

1975-06-30—Публикация

1973-02-06—Подача