1

|-1:юбрете11не относится к области цнфроиой вычислительной тсхпнки и может быть иснользовано в любы.х ui(l)po)bix накопителя.х n.iii аналнзаторах.

П.чвсстпы запомпнаюгцнс устронстса, содержащие блок памяти, блок управления, преобразователь код-напряженно, преобра; оватсль напряженно-код, построенный по методу заряда и разряда емкости.

Однако в нзгзсстны.х запомнна он|их устронстиах отсутствует режим интегрирования накоплен нон нпформацпп.

1,.слыо предлагаемого изобретения является создание запоминающего устройства с интегрированием иакопленион информации без введения в состав прибора дополнительных блоков.

Указанная цель достигается за счет введения дополнительной связи выхода преобразователя код-напряжение со входом преобразователя напряжение-код и использования его зарядпон емкости в качестве промежуточного и запоминающего устройства.

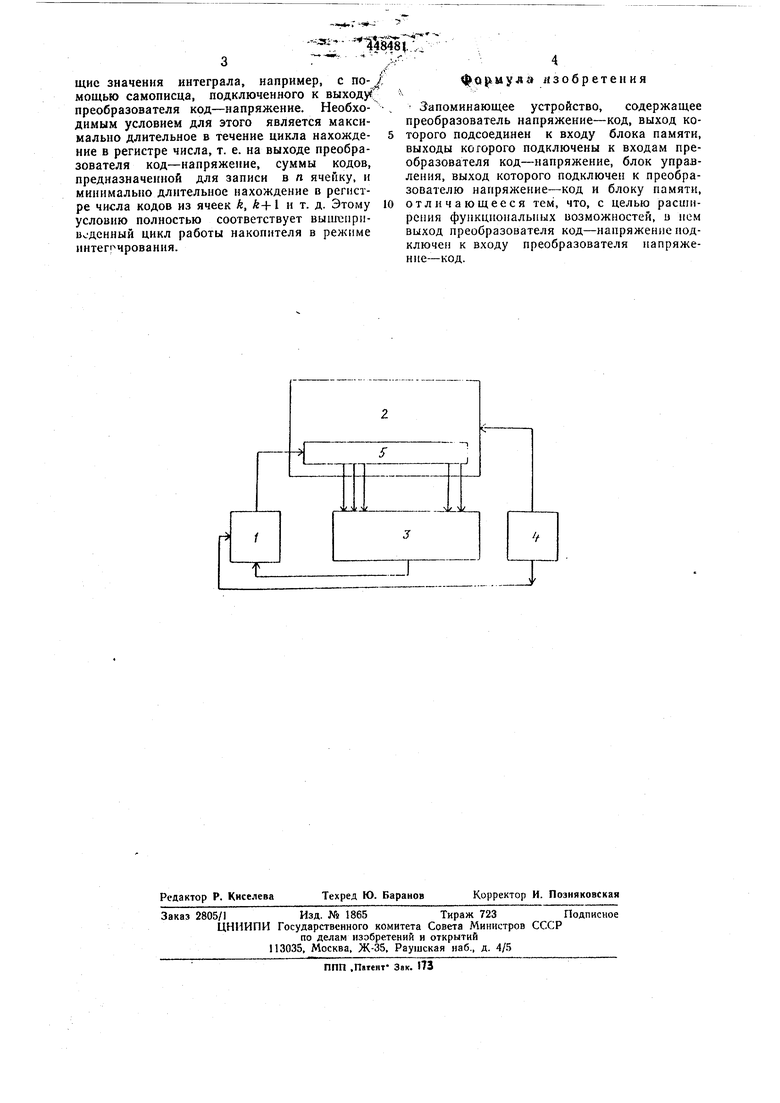

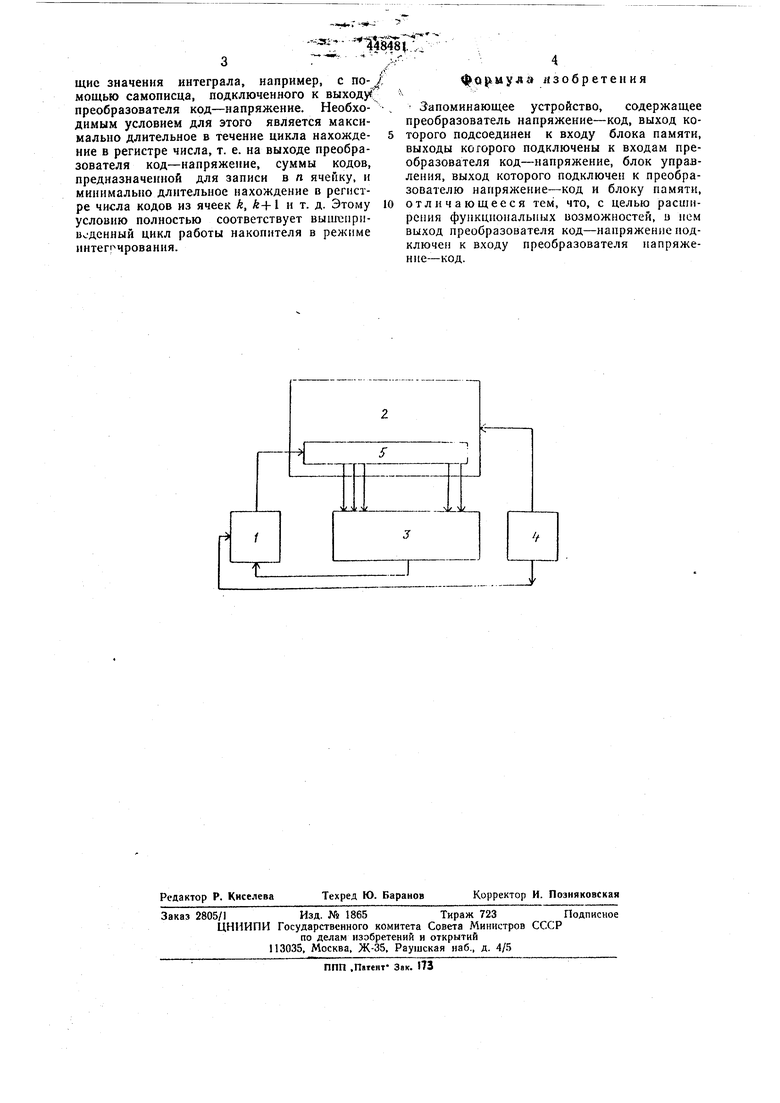

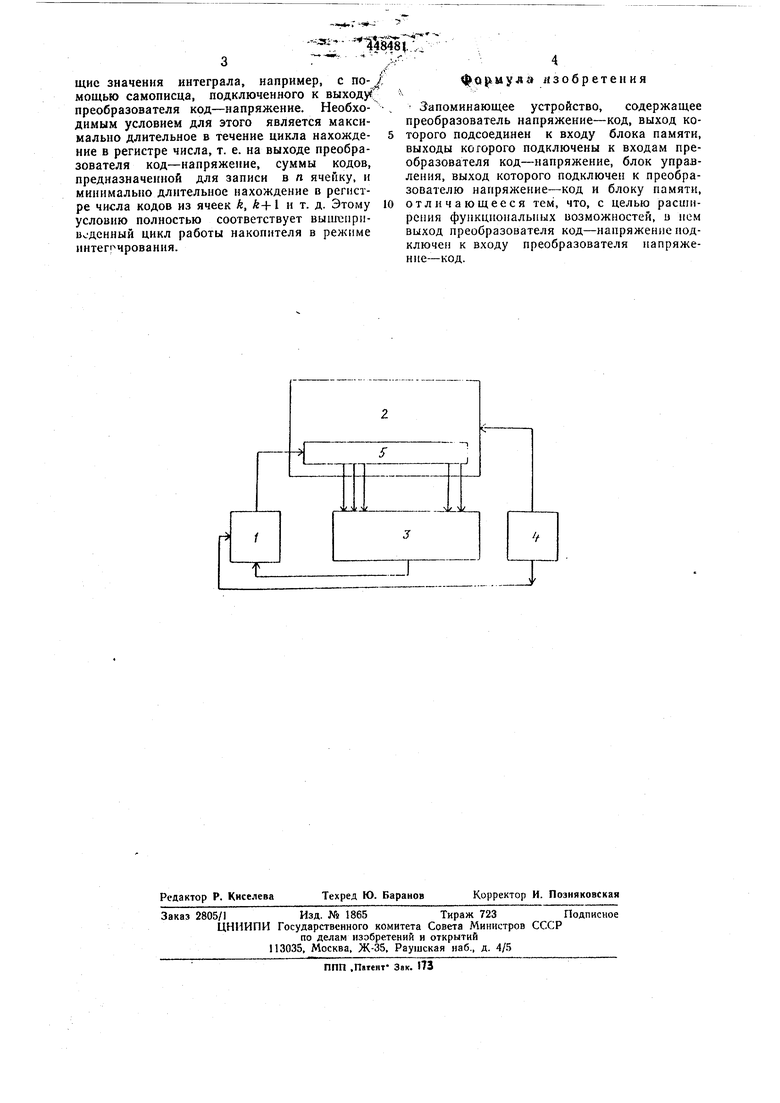

На чертеже представлена блок-схема запоминающего устройства. Схема состоит из преобразователя 1 напряжение-код, блока 2 памяти, преобразователя 3 код-напряжение, блока 4 управления, регистра 5 числа.

В блоке 2 памяти отводится одна ячейка

памяти II для хранения текущ1 х значении интеграла. По команде «считывание информация из k ячейки па.мятп заносится в регистр 5 числа и поступает на преобразователь 3

код-напряжение, с выхода которого напряжение, пропорциоиальиое коду регистра числа, поступает на вход преобразователя напряжение-код. По команде, управляющей работой преобразователя 1, входиое напряжение

запоминается иа его зарядной емкости. За время храие 1ия на зарядной емкости напряжения, пропорционального ходу ячейки к памяти, Б блоке памяти происходит регенерация кода ячейки k (чтобы при интегрировании не

уничтожилась накопленная информация) и считывание в регистр числа кода, хранящегося в ячейке п памяти. После этого в преобразователе I начинается изменение величины напряжения, хранящегося на зарядной емкости, и выдается на счетный вход регистра числа последовательность импульсов, количество которых соответствует коду, хранящемуся в k ячейке памяти. В результате в регистре числа получаем сумму кодов k и п ячеек. Полученная сумма записывается в п ячейку, после чего цикл повторяется для fe-f 1 и п ячеек и т. д.

Задавая соответствующую скорость повторения циклов, можно регистрировать текущис значения интеграла, например, с по- / мощью самописца, подключенного к выходу преобразователя код-напряжение. Необходимым условием для этого является максимально длительное в течение цикла нахожде- 5 ние в регистре числа, т. е. на выходе преобразователя код-напряжение, суммы кодов, предназначеииой для записи в п ячейку, и минимально длительное нахождение в регистре числа кодов из ячеек k, k+ I н т. д. Этому 10 условию полностью соответствует вышеприведенный цикл работы накопителя в режиме интегрирования.

изобретения

Запоминающее устройство, содержащее преобразователь напряжение-код, выход которого подсоединен к входу блока памяти, выходы которого подключены к входам преобразователя код-напряжение, блок управления, выход которого подключен к преобразователю напряжение-код и блоку памяти, отличающееся тем, что, с целью расширения функциональных возможностей, и нем выход преобразователя код-напряжение подключен к входу преобразователя напряжение-код.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1973 |

|

SU368605A1 |

| Устройство для демонстрации шахматной игры на телевизионных приемниках | 1980 |

|

SU951380A1 |

| ЦИФРОВОЙ ИНТЕГРАТОР | 2018 |

|

RU2670389C1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР | 1969 |

|

SU255658A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ИЗМЕНЕНИЯ СВОЙСТВ СЛУЧАЙНОГО СИГНАЛА | 1972 |

|

SU355617A1 |

| УСТРОЙСТВО для ОПРЕДЕЛЕНИЯ ЗАКОНА УПРАВЛЯЮЩЕГО ВОЗДЕЙСТВИЯ | 1969 |

|

SU255659A1 |

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| КОМБИНИРОВАННАЯ ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1966 |

|

SU224910A1 |

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1525607A1 |

| Устройство для определения граничных точек хроматографического пика | 1986 |

|

SU1456973A1 |

Авторы

Даты

1974-10-30—Публикация

1971-09-24—Подача