1

Изобретение относится к области импульсной техники.

Известно устройство для синхронизации импульсов, содержащее триггер, схему совпадения, логические схемы «ИЛИ, «И - НЕ и инвертор.

Целью изобретения является уменьшение критичности к длительности импульсов. , Эта цель достигается за счет введения в предложенное устройство дополнительного триггера и дополнительной схемы совпадения.

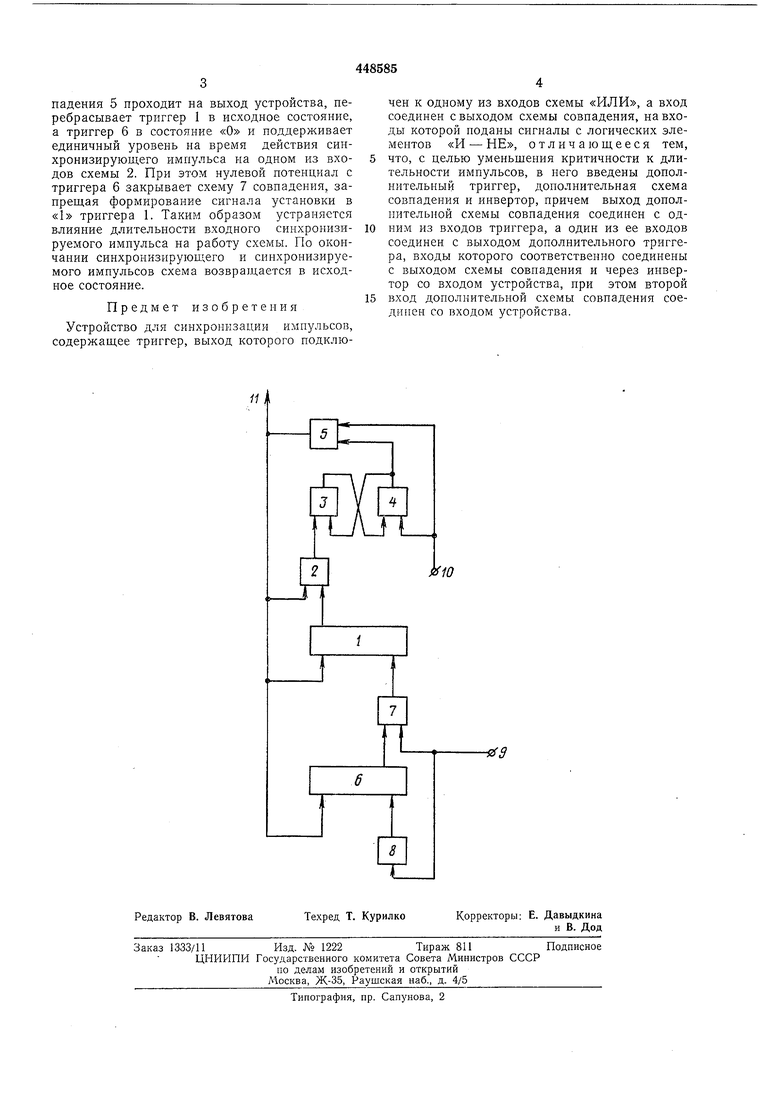

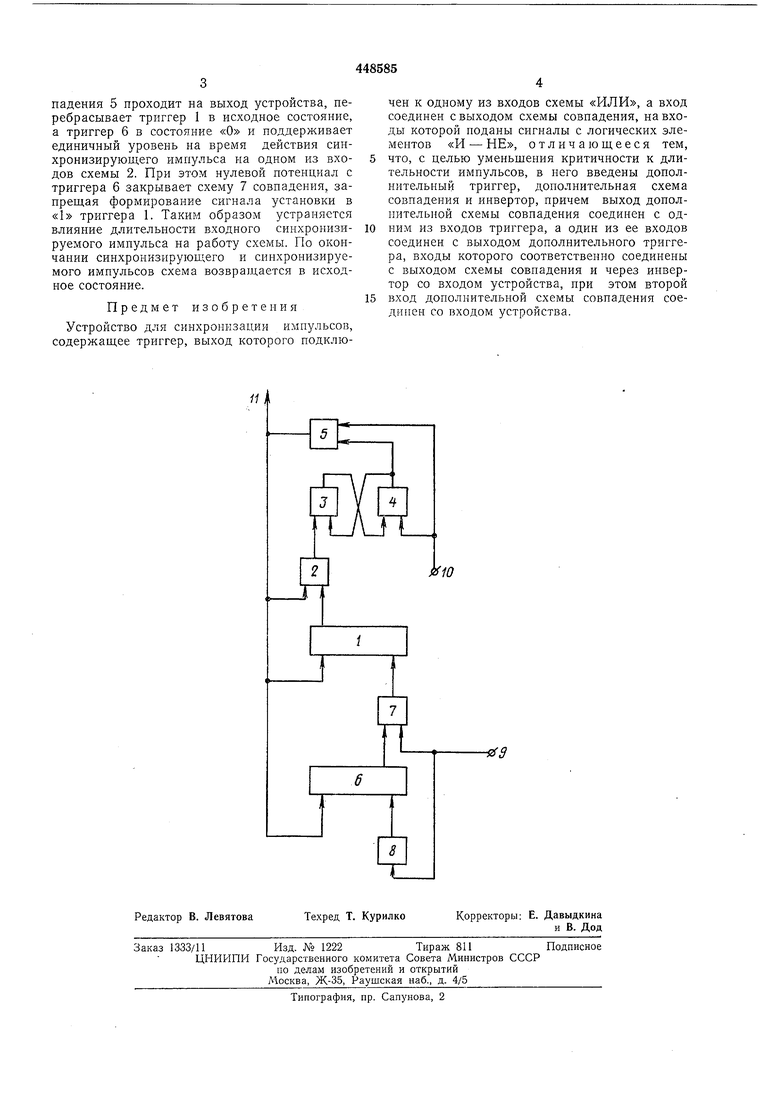

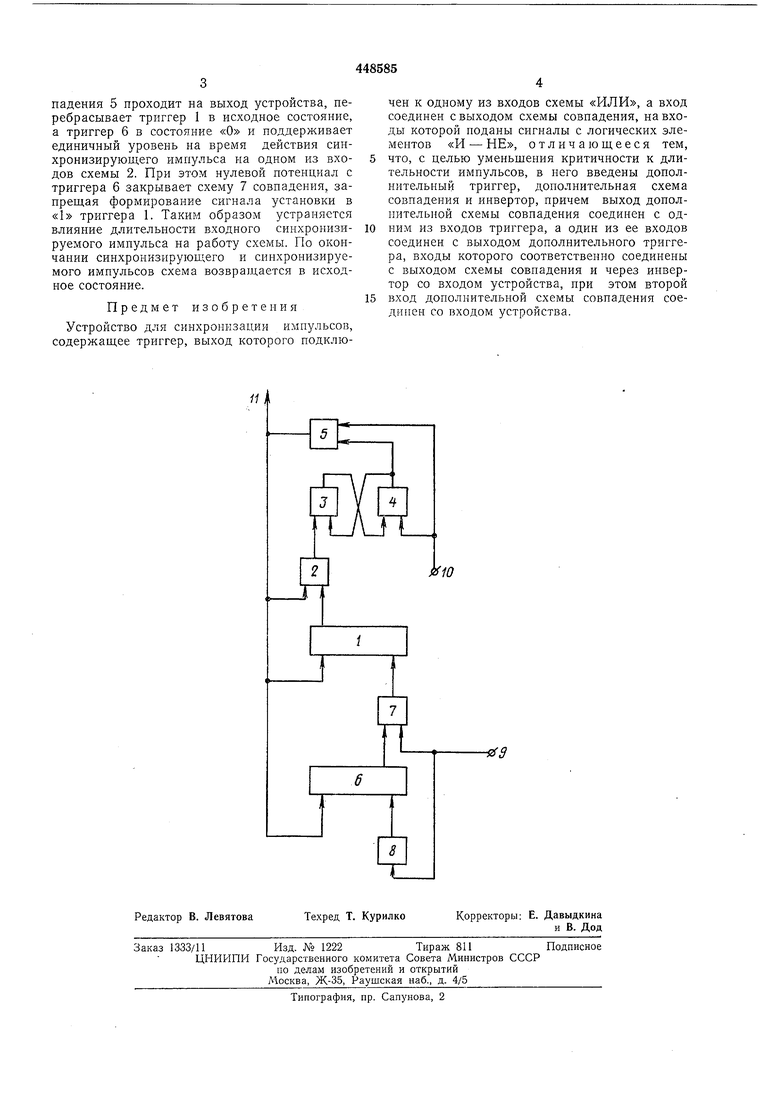

Блок-схема описываемого устройства приведена па чертеже.

Устройство содержит триггер 1, схему 2 «ИЛИ, логические элементы 3, 4 «И - НЕ схему 5 совпадения, дополнительный триггер 6, дополнительную схему 7 совпадения и инвертор 8.

Устройство работает следующим образом.

Синхронизируемые сигналы поступают через вход 9 на один из входов схемы совпадения 7 и вход инвертора 8. В исходном состоянии триггер 1 находится в состоянии «О. Иотенциал с выхода триггера 1 поступает на один из входов схемы «ИЛИ, которая выполняет функцию дизъюнкции двух единичных сигналов. Единичный потенциал с выхода триггера 6 поступает на один из входов схемы 7.

При отсутствии синхронизирующего импульса на входе 10 с выхода элемента 4 снимается единичный потенциал, поступающий на входы схемы совпадения 5 и логического

элемента 3. На выходе схемы 5, а следовательно, и на выходе 11 устройства - нулевой потенциал. Нулевой потенциал с выхода устройства поступает на установочный вход триггеров 1 и 6 и на один из входов схемы 2. ТаКИМ образом, в исходном состоянии с выхода элемента 3 снимается единичный потенциал. Триггер 6 в исходном состоянии находится в состоянии «1 под действием сигнала установки в «1 с выхода инвертора 8 при отсутстВИИ синхронизирующего импульса. Единичный потенциал с выхода триггера 6 ноступает на один из входов схемы 7.

Асинхронный импульс, поступивший на вход 9, проходит через открытую схему 7 совпадения и опрокидывает триггер 1 в «единицу. Единичный потенциал с выхода триггера через схему 2 «ИЛИ поступает на вход элемента 3 и устанавливает на его выходе нулевой потенциал, который запирает элемент 4.

Одновременно на выходе инвертора 8 возникает нулевой потенциал, что соответствует пропаданию сигнала установки в «1 триггера 6.

Поступивший затем на вход 10 синхронизирующий импульс через открытую схему сов

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ИМПУЛЬСОВ | 1972 |

|

SU434581A1 |

| Устройство для формирования одиночного импульса | 1973 |

|

SU738131A1 |

| Устройство для синхронизации импульсов | 1977 |

|

SU660229A2 |

| Генератор одиночных импульсов | 1978 |

|

SU743178A1 |

| Устройство для интегрирования произведения двух случайных сигналов | 1972 |

|

SU454558A1 |

| Устройство для генерации одиночных импульсов | 1977 |

|

SU711670A1 |

| Устройство для контроля и диагностики цифровых устройств | 1988 |

|

SU1583886A2 |

| Устройство для синхронизации импульсов | 1985 |

|

SU1275746A1 |

| Формирователь импульсов | 1986 |

|

SU1383468A1 |

| Устройство для выполнения логических операций при решении дифференциальных уравнений | 1980 |

|

SU955081A1 |

Авторы

Даты

1974-10-30—Публикация

1973-01-05—Подача