12

00 00 00 4 05 DO

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь интервалов времени в цифровой код | 1984 |

|

SU1255984A2 |

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1992 |

|

RU2024186C1 |

| Система стабилизации задержки | 1981 |

|

SU957422A1 |

| Устройство для считывания графической информации | 1986 |

|

SU1354225A1 |

| УСТРОЙСТВО ДЛЯ РЕГЕНЕРАЦИИ ИНФОРМАЦИИ ДИНАМИЧЕСКОЙ ПАМЯТИ | 1992 |

|

RU2049363C1 |

| УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 2000 |

|

RU2182358C2 |

| Преобразователь двоичного кода в код с произвольным весом младшего разряда | 1985 |

|

SU1325708A1 |

| Термографический регистратор | 1984 |

|

SU1174288A1 |

| Устройство определения временного положения импульсных сигналов | 1988 |

|

SU1596301A1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ШКАЛЫ ВРЕМЕНИ | 1995 |

|

RU2082216C1 |

Изобретение относится к радиотехнике, в частности к аппаратуре для контроля дальномерных систем. и предназначено для задания формы импульсов. Изобретение позволяет повысить быстродействие формирователя, что достигается введением в него триггера -3, инвертора 5, фазосдвигаю- щего блока 4, блока 8 управления, ,делителя 10 и блока 9 выделения. Устройство, кроме того, содержит входную шину 1, генератор 2 тактовых импульсов, счетчик 6, запоминающее устройство 7, цифроаналоговый преобразователь 11, выходную шину 12. Возможность работы устройства при внешнем запуске осуществляется изменением режима работы устройства. 1 з.п. ф-лы, 5 ил. SS

Фиг.1

Изобретение относится к радиотехнике, в частности к аппаратуре для контроля дальномерных систем, и предназначено для задания формы импульсов.

Целью изобретения является повьше- ние быстродействия.

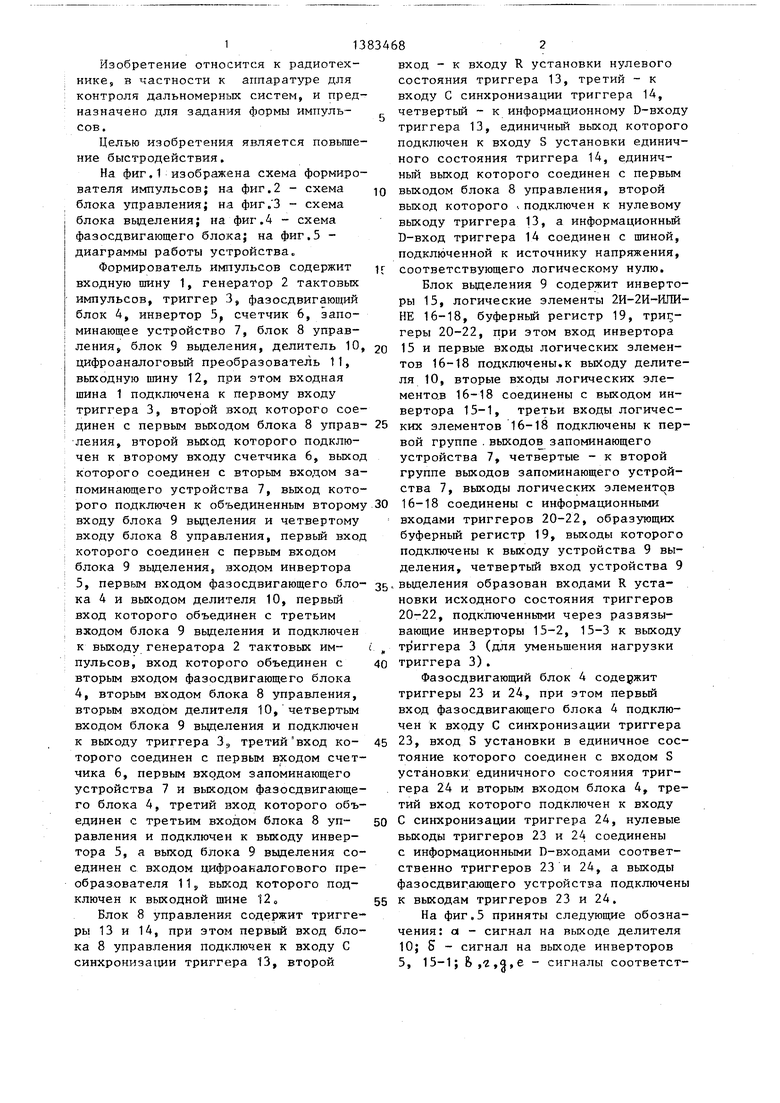

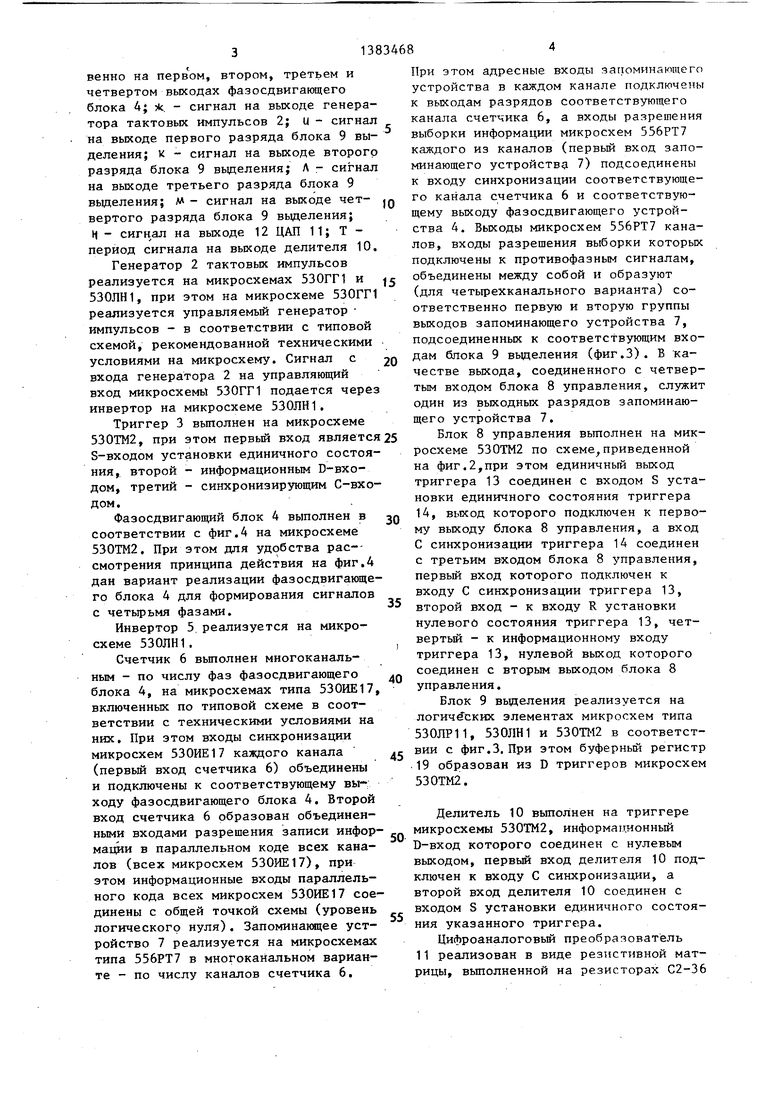

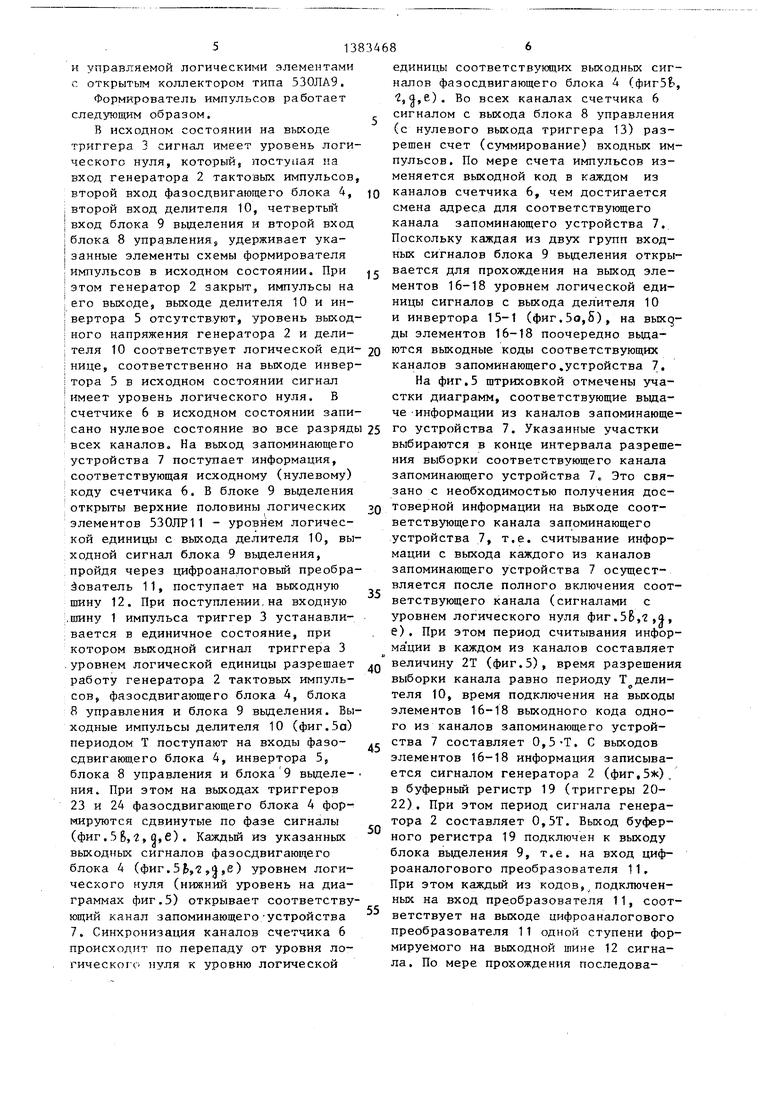

На фиг,1 изобр;зжена схема формирователя импульсов; на фиг,2 - схема блока управления; на фиг, 3 - схема блока вьщеления; на фиг,4 - схема фазосдвигающего блока; на фиг,5 - диаграммы работы устройства

Формирователь импульсов содержит входную шину 1, генератор 2 тактовых импульсов, триггер 3, фазосдвигающий блок 4, инвертор 5 счетчик 6, запоминающее устройство 7, блок 8 управления, блок 9 выделения, делитель 10, 2о 15 и первые входы логических злемен- цифроаналоговый преобразователь 11, тов 16-18 подключены.к выходу делите- выкодную шину 12, при этом входная шина 1 подключена к первому входу

ля 10, вторые входы логических элементов 16-18 соединены с выходом инвертора 15-1, третьи входы логичестриггера 3, второй вход которого соединен с первым выходом блока 8 управ- 25 ких элементов 16-18 подключены к пер- ления, второй выход которого подклю- вой группе.выходов запоминающего чен к второму входу счетчика 6, выход устройства 7, четвертые - к второй которого соединен с вторым входом за- группе выходов запоминающего устрой- поминающего устройства 7, выход кото- ства 7, выходы логических элементов рого подключен к объединенным второму 30 16-18 соединены с информационными входу блока 9 вьщеления и четвертому входу блока 8 управления, первьй вход которого соединен с первым входом блока 9 выделения, входом инвертора

входами триггеров 20-22, образующих буферньй регистр 19, выходы которого подключены к выходу устройства 9 выделения, четвертьй вход устройства 9

5, первым входом фазосдвигающего бло- ЗБ выделения образован входами R уста- ка 4 и выходом делителя 10, первьй новки исходного состояния триггеров вход которого объ€ динен с третьим 20-22, подключенными через развязывающие инверторы 15-2, 15-3 к выходу , триггера 3 (для уменьшения нагрузки

входом блока 9 вьщеления и подключен к выходу генератора 2 тактовых импульсов, вход которого объединен с вторым входом фазосдвигающего блока 4, вторым входом блока 8 управления, вторым входом делитсшя 10, четвертым входом блока 9 вьщеления и подключен к выходу триггера 3,, третий вход которого соединен с первым входом счетчика 6, первьм входом запоминающего устройства 7 и выходом фазосдвигающего блока 4, третий вход которого объединен с третьим входом блока 8 управления и подключен к выходу инвертора 5, а выход блока 9 вьщеления соединен с входом цифроакалогового преобразователя 11J вьпсод которого подключен к выходной шине 12„

Блок 8 управления содержит триггеры 13 и 14, при этом первьй вход блока 8 управления подключен к входу С синхронизации триггера 13, второй

40 триггера 3),

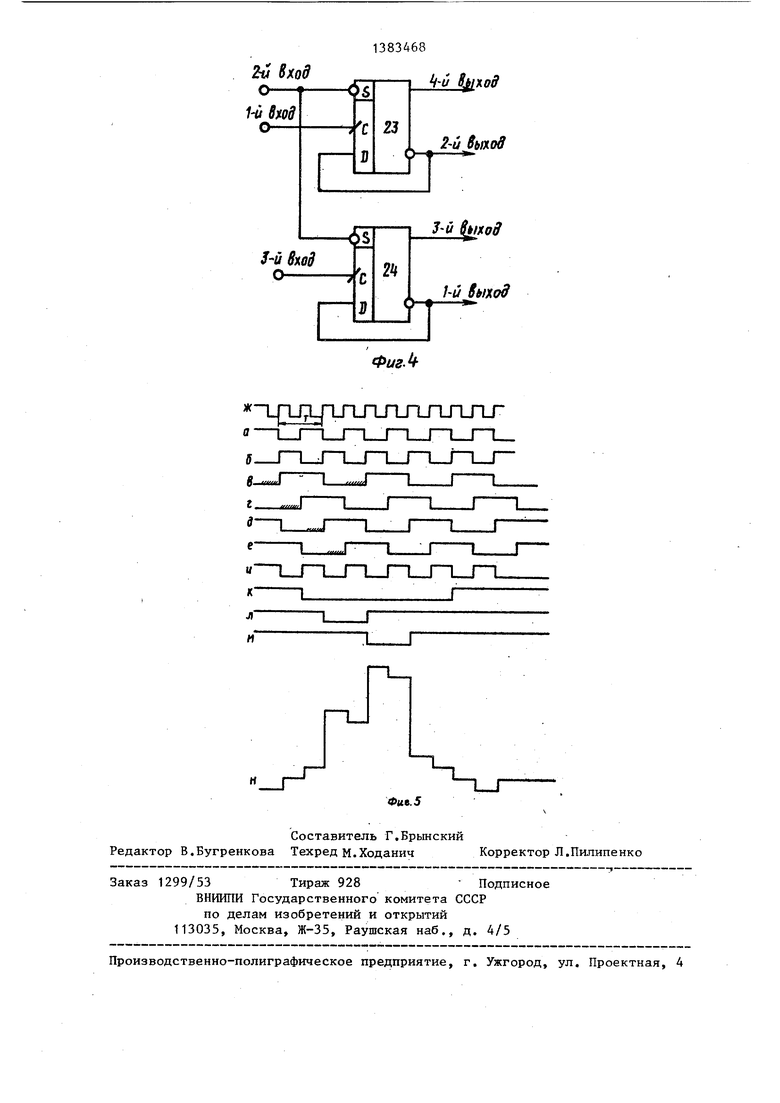

Фазосдвигающий блок 4 содержит триггеры 23 и 24, при этом первьй вход фазосдвигающего блока 4 подключен к входу С синхронизации триггера

45 23, вход S установки в единичное состояние которого соединен с входом S установки единичного состояния триггера 24 и вторым входом блока 4, третий вход которого подключен к входу

50 С синхронизации триггера 24, нулевые выходы триггеров 23 и 24 соединены с информационными D-входами соответственно триггеров 23 и 24, а выходы фазосдвигающего устройства подключены

55 к выходам триггеров 23 и 24,

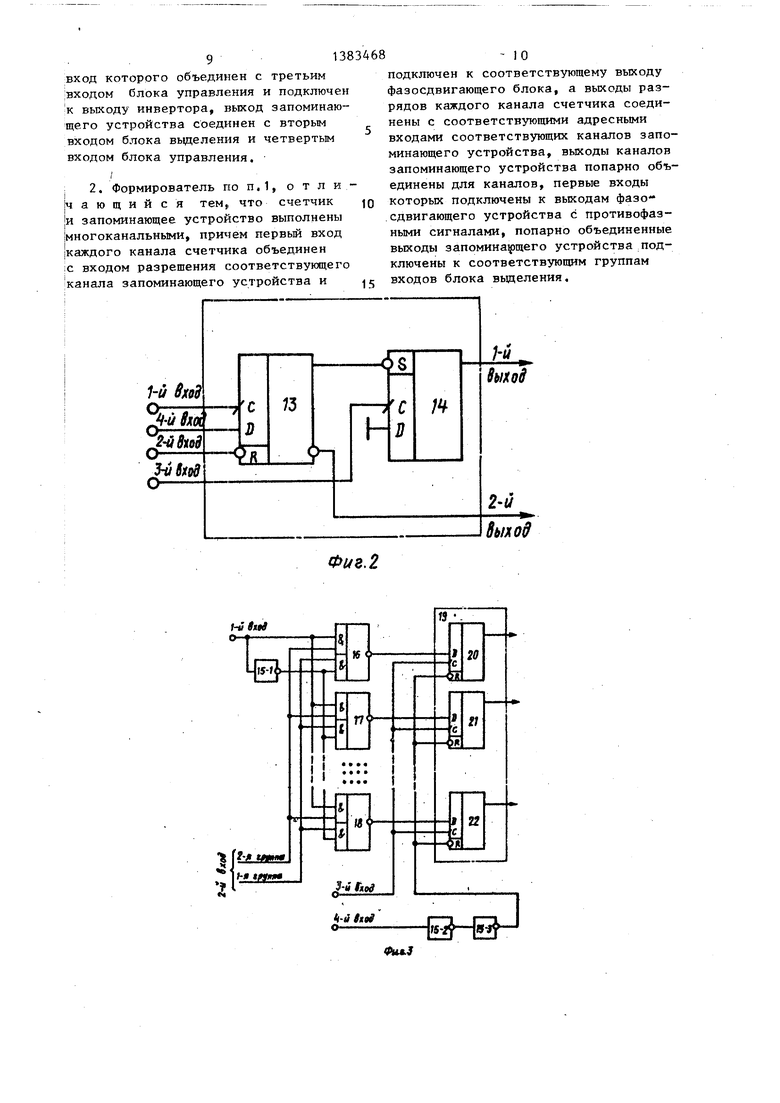

На фиг, 5 приняты cлeдyюшJ e обозначения: а - сигнал на выходе делителя 10; 5 - сигнал на выходе инверторов 5, 15-1; & , Z,4,e - сигналы соответствход - к входу R установки нулевого состояния триггера 13, третий - к входу С синхронизации триггера 14, четвертый - к информационному D-входу триггера 13, единичный выход которого подключен к входу S установки единичного состояния триггера 14, единич- ньй выход которого соединен с первым

выходом блока 8 управления, второй выход которого подключен к нулевому выходу триггера 13, а информационньй D-вход триггера 14 соединен с шиной, подключенной к источнику напряжения,

соответствующего логическому нулю.

Блок вьделения 9 содержит инверторы 15, логические элементы 2И-2И-ИЛИ- НЕ 16-18, буферньй регистр 19, геры 20-22, при этом вход инвертора

15 и первые входы логических злемен- тов 16-18 подключены.к выходу делите-

ля 10, вторые входы логических элементов 16-18 соединены с выходом инвертора 15-1, третьи входы логических элементов 16-18 подключены к пер- вой группе.выходов запоминающего устройства 7, четвертые - к второй группе выходов запоминающего устрой- ства 7, выходы логических элементов 16-18 соединены с информационными

входами триггеров 20-22, образующих буферньй регистр 19, выходы которого подключены к выходу устройства 9 выделения, четвертьй вход устройства 9

триггера 3),

Фазосдвигающий блок 4 содержит триггеры 23 и 24, при этом первьй вход фазосдвигающего блока 4 подключен к входу С синхронизации триггера

23, вход S установки в единичное состояние которого соединен с входом S установки единичного состояния триггера 24 и вторым входом блока 4, третий вход которого подключен к входу

С синхронизации триггера 24, нулевые выходы триггеров 23 и 24 соединены с информационными D-входами соответственно триггеров 23 и 24, а выходы фазосдвигающего устройства подключены

к выходам триггеров 23 и 24,

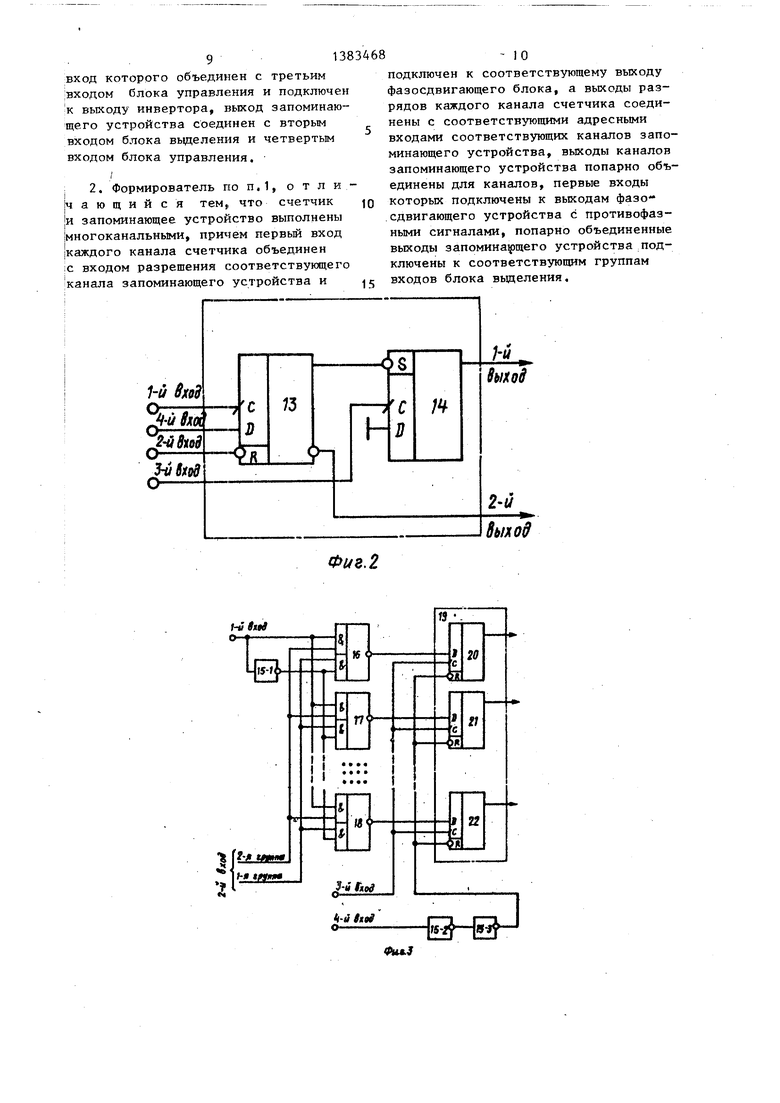

На фиг, 5 приняты cлeдyюшJ e обозначения: а - сигнал на выходе делителя 10; 5 - сигнал на выходе инверторов 5, 15-1; & , Z,4,e - сигналы соответст

венно на первом, втором, третьем и четвертом выходах фазосдвигающего блока 4; )k. - сигнал на выходе генератора тактовых импульсов 2; U - сигнал на выходе первого разряда блока 9 выделения; к - сигнал на выходе второго разряда блока 9 выделения; Л - сигнал на выходе третьего разряда блока 9 вьщеления; м - сигнал на выходе четвертого разряда блока 9 выделения; Н - на выходе 12 ЦАП 11; Т - период сигнала на выходе делителя 10.

Генератор 2 тактовых импульсов реализуется на микросхемах 530ГГ1 и 530ЛН1, при этом на микросхеме 530ГГ1 реализуется управляемый генератор импульсов - в соответствии с типовой схемой, рекомендованной техническими условиями на микросхему. Сигнал с входа генератора 2 на управляющий вход микросхемы 530ГГ1 подается через инвертор на микросхеме 530ЛН1.

Триггер 3 выполнен на микросхеме 530ТМ2, при этом первый вход является S-входом установки единичного состояния, второй - информационным D-BXO- дом, третий - синхронизирующим С-вхоДОМ.

Фазосдвигающий блок 4 выполнен в соответствии с фиг.4 на микросхеме 530ТМ2. При этом для удобства рас-- смотрения принципа действия на фиг,4 дан вариант реализации фазосдвигающего блока 4 для формирования сигналов с четырьмя фазами.

Инвертор 5, реализуется на микросхеме 530ЛН1.

Счетчик 6 выполнен многоканальным - по числу фаз фазосдвигающего блока 4, на микросхемах типа 530ИЕ17, включенных по типовой схеме в соответствии с техническими условиями на них. При этом входы синхронизации микросхем 530ИЕ17 каждого канала (первый вход счетчика 6) объединены и подключены к соответствующему вы-; ходу фазосдвигающего блока 4. Второй вход счетчика 6 образован объединенными входами разрешения записи инфор- мащ1и в параллельном коде всех каналов (всех микросхем 530ИЕ17), при этом информационные входы параллельного кода всех микросхем 530ИЕ17 соединены с общей точкой схемы (уровень логического нуля). Запоминающее устройство 7 реализуется на микросхемах типа 556РТ7 в многоканальном варианте - по числу каналов счетчика 6.

При этом адресные входы загюминакнпего устройства в каждом канале подключены к выходам разрядов соответствующего канала счетчика 6, а входы разрешения выборки информации микросхем 556РТ7 каждого из каналов (первый вход запоминающего устройства 7) подсоединены к входу синхронизации соответствующего канала счетчика 6 и соответствующему выходу фазосдвигающего устройства 4. Выходы микросхем 556РТ7 каналов, входы разрешения выборки которых подключены к противофазным сигналам, объединены между собой и образуют (для четырехканального варианта) соответственно первую и вторую группы выходов запоминающего устройства 7, подсоединенных к cooтвeтctвyющим входам блока 9 вьоделения (фиг.З). В качестве выхода, соединенного с четвертым входом блока 8 управления, служит один из выходных разрядов запоминающего устройства 7.

Блок 8 управления вьтолнен на микросхеме 530ТМ2 по схеме приведенной на фиг.2,при этом единичный выход триггера 13 соединен с входом S установки единичного состояния триггера 14, вькод которого подключен к первому выходу блока 8 управления, а вход С синхронизации триггера 14 соединен с третьим входом блока 8 управления, первый вход которого подключен к входу С синхронизации триггера 13, второй вход - к входу R установки нулевого состояния триггера 13, чет- вертьш - к информационному входу триггера 13, нулевой выход которого соединен с вторым выходом блока 8 управления.

Блок 9 вьщеления реализуется на логичё ских элементах микросхем типа 530ЛР11, 530ЛН1 и 530ТМ2 в соответствии с фиг.З. При этом буферный регистр 19 образован из D триггеров микросхем 530ТМ2.

Делитель 10 вьтолнен на триггере микросхемы 530ТМ2, информационный D-вход которого соединен с нулевым выходом, первый вход делителя Ю подключен к входу С синхронизации, а второй вход делителя 10 соединен с входом S установки единичного состояния указанного триггера.

Цифроаналоговьш преобразователь 11 реализован в виде резистнвной матрицы, вьшолненной на резисторах С2-36

513

и управляемой логическими элементами с. открытым коллектором типа 530ЛА9.

Формирователь импульсов работает следующим образом,

В исходном состоянии на выходе триггера 3 сигнал имеет уровень логического нуля, КОТОРЫ-Й5 поступая на вход генератора 2 тактовых импульсов второй вход фазосдвигающего блока 4, второй вход делителя 10, четвертьй вход блока 9 вьщеления и второй вход блока 8 упра.вления, удерживает указанные элементы схемы формирователя Импульсов в исходном состоянии. При этом генератор 2 закрыт, импульсы на его выходе, выходе делителя 10 и инвертора 5 отсутствуют, уровень выходного напряжения генератора 2 и дели

теля 10 соответствует логической еди- 20 ются выходные коды соответствующих

нице, соответственно на выходе инвертора 5 в исходном состоянии сигнал имеет уровень логического нуля. В счетчике 6 в исходном состоянии запи сано нулевое состояние во все разряды 25 г о устройства 7. Указанные участки

всех каналов. На выход запоминающего устройства 7 поступает информация, соответствующая исходному (нулевому)

коду счетчика 6, В блоке 9 вьщеления открыты верхние половины логических элементов 530ЛР11 - уровнем логической единицы с выхода делителя 10, выходной сигнал блока 9 выделения, пройдя через цифроаналоговьй преобра- йователь 11, поступает на выходную шину 12, При поступлении,на входную

:.шину 1 импульса триггер 3 устанавливается в единичное состояние, при котором выходной сигнал триггера 3

.уровнем логической единицы разрешает работу генератора 2 тактовых импульсов, фазосдвигающего блока 4, блока 8 управления и блока 9 выделения. Выходные импульсы делителя 10 (фиг,5а) периодом Т поступают на входы фазо- сдвигаюш,его блока 4, инвертора 5, блока 8 управления и блока 9 вьщеле- ния. При этом на выходах триггеров 23 и 24 фазосдвигающего блока 4 формируются сдвинутые по фазе сигналы (фиг, 5 &,, Q,e) , Каждый из указанных выходных сигналов фазосдвигающего блока 4 (фиг,5Ь, г , 1 ,е) уровнем логического нуля (нижний уровень на диаграммах фиг,5) открывает соответствующий канал запоминающего/устройства 7, Синхронизация каналов счетчика 6 происходит по перепаду от уровня ло- гическотч нуля к уровню логической

0

5

единицы соответствующих выходных сигналов фазосдвигающего блока 4 (, )- Во всех каналах счетчика 6 сигналом с выхода блока 8 управления (с нулевого выхода триггера 13) разрешен счет (суммирование) входных импульсов. По мере счета импульсов изменяется выходной код в каждом из каналов счетчика 6, чем достигается смена адрес.а для соответствующего канала запоминающего устройства 7. Поскольку каждая из двух групп входных сигналов блока 9 вьвделения открывается для прохождения на выход элементов 16-18 уровнем логической единицы сигналов с выхода делителя 10 и инвертора 15-1 (фиг,5о,5), на выхд- ды элементов 16-18 поочередно вьщаканалов запоминающего.устройства 7,

На фиг.5 штриховкой отмечены участки диаграмм, соответствующие вьща- че -информации из каналов запоминающе5

0

выбираются в конце интервала разрешения выборки соответствующего канала запоминающего устройства 7. Это связано с необходимостью получения дос- 0 товерной информации на выходе соответствующего канала запоминающего устройства 7, т,е, считывание информации с выхода каждого из каналов запоминающего устройства 7 осуществляется после полного включения соответствующего канала (сигналами с уровнем логического нуля фиг,56,7,4, е), При этом период считывания инфор- ма ции в каждом из каналов составляет величину 2Т (фиг,5), время разрешения выборки канала равно периоду Т делиО

теля 10, время подключения на выходы элементов 16-18 выходного кода одного из каналов запоминающего устройства 7 составляет 0,5-1, С выходов элементов 16-18 информация записывается сигналом генератора 2 (фиг,5ж), в буферный регистр 19 (триггеры 20- 22), При этом период сигнала генератора 2 составляет 0,5Т, Выход буферного регистра 19 подключен к выходу блока вьщеления 9, т,е, на вход циф- роаналогового преобразователя 11, При этом каждый из кодов, подключенных на вход преобразователя 11, соответствует на выходе цифроаналогового преобразователя 11 одной ступени формируемого на выходной шине 12 сигнала. По мере прохождения последова5

0

5

7138

тельных состояний счетчика 6 на выходе цифроаналогового преобразователя 11 формируется импульс в соответствии с кодами, хранимыми в запоминающем устройстве 7. При достижении состояния, соответствующего моменту окончания формирования на выход одного из разрядов запоминающего устройства 7 (в четвертом канале) вьздается сигнал с уровнем логической единицы, которая синхронизирующим перепадом сигнала на выходе делителя 10 (фиг.Зск) от уровня ло гического нуля к уровню логической единицы записывается в три1- гер 13 устройства 8 управления. Триггер 13 освобождает триггер 14, удерживаемый ранее сигналом с уровнем логического нуля с единичного выхода триггера 13, и одновременно с нулевого выхода триггера 13 вьщается сигнал с уровнем логического нуля, который, поступив на второй вход счетчика 6, разрешает запись нулевой информации в параллельном коде :в указанный счетчик. Ближайший к моменту записи логической единицы в триггер 13 синхронизирующий перепад: на выходе инвертора 5 устанавливает триггер 14 в нулевое состояние через 0,5Т после появления сигнала разрешения парал- лельной записи счетчика 6 на нулевом выходе триггера 13. При этом на информационный D-вход триггера 3 с выхода триггера 14 вьщается сигнал с уровнем логического нуля, которьй разрешает запись исходного (нулевого) состояния в триггер 3. На синхронизирующий вход триггера 3 подан сигнал с выхода фазосдвигающего блока 4 - , из четвертого канала (фиг.5е). Далее в течение времени 2Т происходит запись исходного (нулевого) состояния во все каналы счетчика 6 сигналами с соответствующих выходов фазосдвигающего блока 4 (фиг.5 Б,г,а,е) . В , конце указанного интервала 2Т происходит запись исходного (нулевого) состояния в триггер 3, Выходной сигнал триггера 3 приводит в исходное состояние генератор тактовых импульсов 2, фазосдвигающий блок 4, блок 8 управления и блок 9 выделения.

Значение минимальной длительности выходного кода блока 9 вьщеления определяет быстродействие формирователя импульсов. При этом минимальная длительность равна (фиг.5).

e.f. ми ч

-О,5 Тмин

8

где CCT, ,и - минимальная длительность; мич минимальный период сигнала на вьсходе делителя 10.

Значение Т f определено задержкой в прохождении сигналов в цепях фазосдвигающего блока 4, запоминающего устройства 7 и блока 9.

- Kiiii -A D t/

де

fc

B.p

мин -«.P

задержка сигнала в фазо- сдвигающем блоке 4; время выборки разрешения микросхем запоминающего устройства 7; задержка сигнала в блоке выделения,

S При этом

в

ex

где - в задержка от входа блока 9 до информационных входов триггеров 20-22; время разрешения триггеров 20-22.

Р25

ю

Формула изобретени

цифроаналоговый преобразователь и

счетчик, соединенньй по выходу с входом запоминающего устройства, отличающийся тем, что, с целью повьш1ения быстродействия, в него введены триггер, инвертор, фазосдвигающий блок, блок управления, делитель и блок вьщеления, выход кото- рого соединен с входом цифроаналогового преобразователя, первый вход

блока вьщеления объединен с первыми входами фазосдвигающего блЪка, блока управления, входом инвертора и подключен к выходу делителя, первый вход которого соединен с третьим входом блока вьщеления и выходом генератора тактовых импульсов, вход которого объединен с вторыми входами фазосдвигающего блока, блока управления, делителя, четвертым входом блока

ю

З

0

вьщеления и подключен к выходу триггера, первьш вход которого соединен с входной щиной, а второй вход триггера подключен к первому в ыходу блока управления, второй выход которого соединен с вторым входом счетчика, первый вход которого соединен с входом разрешения запоминающего устройства, третьим входом триггера и выходом фазосдвигающего блока, третий

91383468

вход кот(5рого объединен с третьим входом блока управления и подключен к выходу инвертора, выход запоминающего устройства соединен с вторым входом блока вьщеления и четвертым входом блока управления.

: 2. Формирователь по п,1, о т л и - ч а ю щ и и с я тем,, что счетчик |и запоминающее устройство выполнены Многоканальными, причем первьй вход |каждого канала счетчика объединен :с входом разрешения соответствующего ;канала запоминающего устройства и

Фие.2

- 10

подключен к соответствующему выходу фазосдвигающего блока, а выходы разрядов каждого канала счетчика соединены с соответствующими адресными входами соответствующих каналов запоминающего устройства, выходы каналов запоминающего устройства попарно объединены для каналов, первые входы которых подключены к выходам фазо сдвигающего устройства с противофазными сигналами, попарно объединенные выходы запоминающего устройства подключены к соответствующим группам входов блока вьзделения.

л-pJ;l-fLПJlJlJ JlJlЛ-Г

ФигЛ

| Горшков Б.И | |||

| Радиоэлектронные устройства | |||

| - М.: Радио и связь, 1984, с | |||

| Нож для надрезывания подошвы рантовой обуви | 1917 |

|

SU269A1 |

| Гнатек Ю.Р | |||

| Справочник по цифро- аналоговым и аналого-цифровым преобразователям | |||

| - М.: Радио и связь,- 1982, с.259, рис.4.129. | |||

Авторы

Даты

1988-03-23—Публикация

1986-07-31—Подача