1

Изобретение относится к электроизмерительной технике и предназначено для деления чисел, представленных в число-импульсных кодах, в частности, может быть использовано в устройствах обработки информации автоматических систем контроля и управления.

Известно устройство для деления чисел, представленных в число-импульсных кодах, содержащее два реверсивных счетчика, выходы которых подключены ко входам соответствующих схем сравнения, другие входы которых соединены с выходами счетчика делителя, а выходы подключены к нулевым входам соответствующих реверсивных счетчиков, два делителя импульсов на десять, тактовый генератор, распределительный блок, блок приема результата, два триггера управления реверсом, логические схемы «И, «ИЛИ.

Недостатком известного устройства является то, что время вычисления прямо пропорционально требуемой точности получения результата.

С целью повыщения быстродействия устройства выход тактового генератора подключен ко входу первой схемы «И, другой вход которой соединен с выходом распределительного блока, а выход подключен к первым входам второй и третьей схем «И, второй вход второй схемы «И соединен с выходом первого триггера управления реверсом, со вторым входом второго триггера управления реверсом и входом распределительного блока; второй вход третьей схемы «И соединен с выходом второго триггера управления реверсом, со входом распределительного блока и со входом первой схемы «ИЛИ, другой вход которой соединен со входом «Окончание записи устройства, а выход подключен

ко второму входу первого триггера управления реверсом; третий вход второй схемы «И подключен к нулевому выходу первого реверсивного счетчика и к первому входу первого триггера управления реверсом; третий вход

третьей схемы «РЬ подключен к нулевому выходу второго реверсивного счетчика и к первому входу второго триггера управления реверсом, выход второй схемы «И подключен ко второму входу второй схемы «ИЛИ,

выход которой соединен со входом второго реверсивного счетчика, а через делитель импульсов на десять - к третьему входу третьей схемы «ИЛИ, выход которой соединен со входом первого реверсивного счетчика; выход третьей схемы «И подключен к первому входу третьей схемы «ИЛИ, второй вход которой соединен со входом делимого устройства, а выход подключен к входу первого реверсивного счетчика и через другой

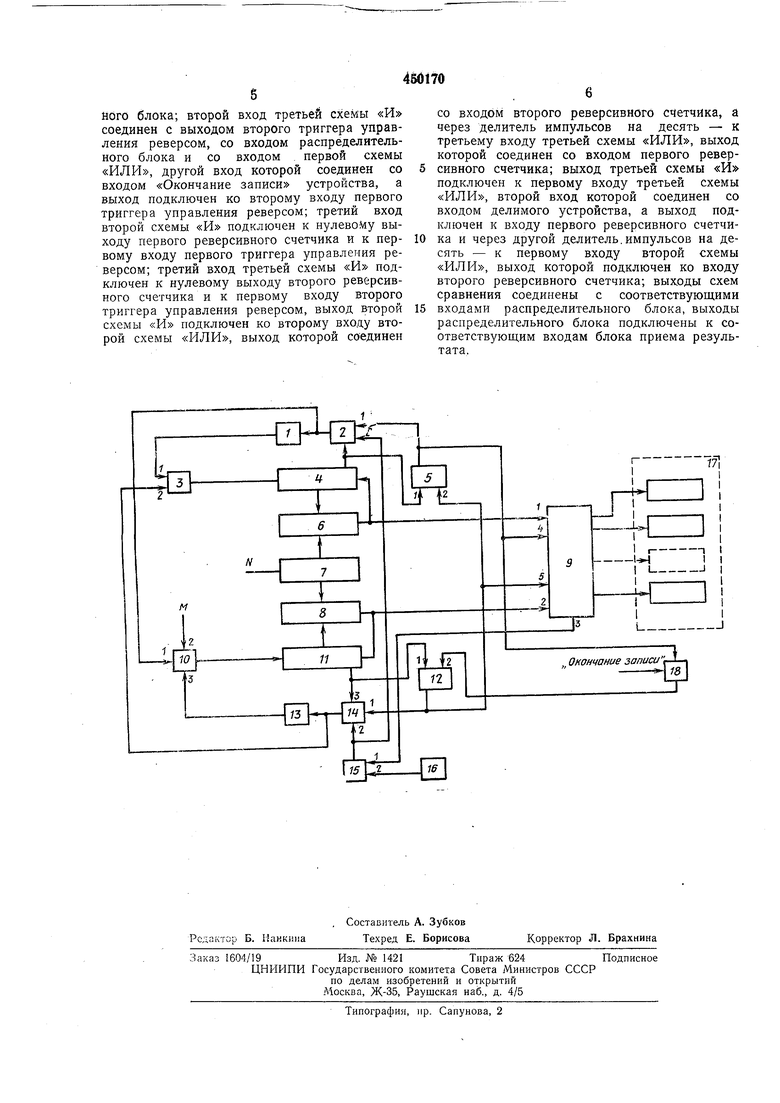

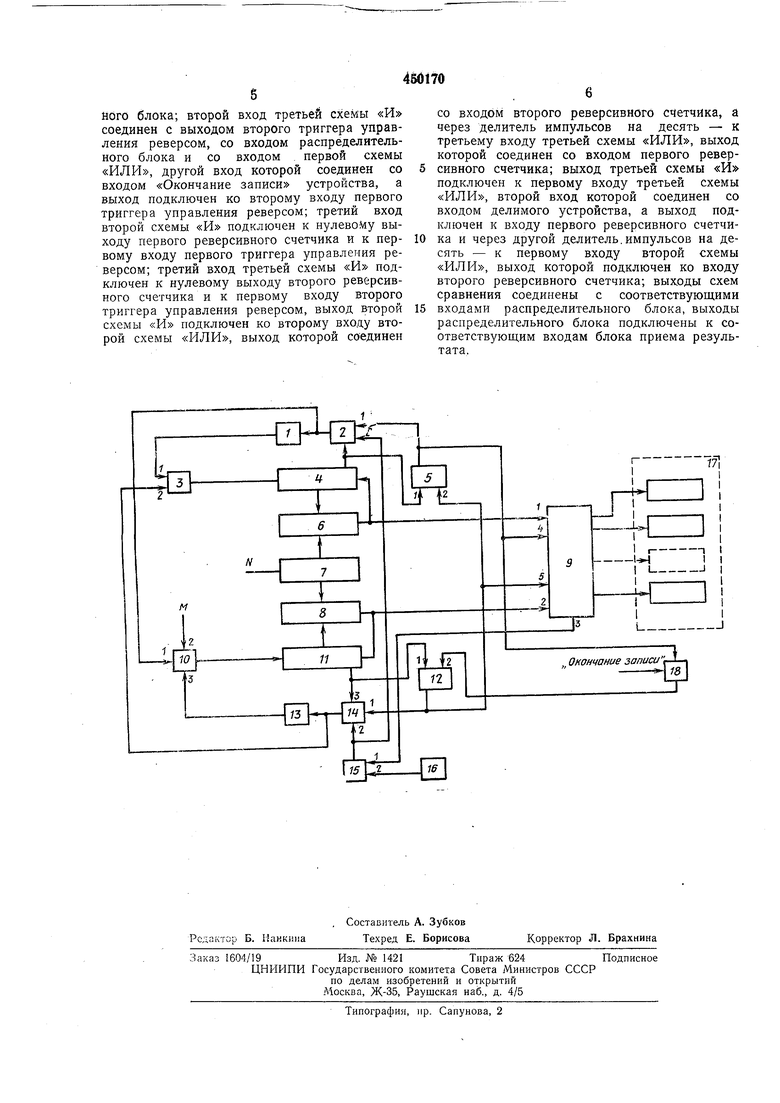

делитель импульсов на десять - к первому 3 входу второй схемы «ИЛИ, выход которой подключен ко входу второго реверсивного счетчика; выходы схем сравнения соединены с соответствующими входами распределительного блока, выходы распределительного5 блока подключены к соответствующим входам блока приема результата. Сущность изобретения заключается в том, что в устройстве не числитель умножается на число, кратное десяти, для повыщенияЮ точности операции деления, а остаток от деления числителя на знаменатель, что дает существенный выигрыщ в быстродействии. На чертеже изображена блок-схема изобретения, где:15 1 - делитель импульсов на десять; 2 - логическая схема 3 - логическая схема 4 - реверсивный счетчик; 5 - триггер управления реверсом; 6 - схема сравнения; 7 - счетчик делителя; 8 - схема срав-20 нения; 9 - распределительный блок; 10- логическая схема 11 - реверсивный счетчик; 12 - триггер управления реверсом; 13- делитель импульсов на десять; 14 - логическая схема 15 - логическая схема25 16-тактовый генератор; 17-блок приема результата; 18-логическая схема «ИЛИ. Работа устройства заключается в следующем.30 В исходном состоянии реверсивные счетчики 4, 11 обнулены и находятся в режиме суммирования. На схему «И 15 поступает сигнал разрещения с выхода 3 распределительного блока 9. Схемы «И 2, 14 закрыты по35 первым входам. На вход двоичного счетчика 7 поступает число-импульсный код делителя N. После записи делителя на вход схемы «ИЛИ 10 поступает число-импульсный код делимого40 М. Двоичный счетчик 7, схема сравнения 8 и реверсивный счетчик 11 образуют пересчетную схему с коэффициентом пересчета 1 : Л. С выхода схемы сравнения 8 снимается целочисленное значение результата деления45 Y - и заносится через распределительЛ г г Iный блок 9 в декады целой части блока приема результата. После окончания поступления число-импульсного кода делимого М50 вырабатывается импульс «Окончание записи, который перебрасывает триггер 12 управления реверсом, в результате чего реверсивный счетчик И переключается в режим вычитания и схема «И 14 открывается по55 первому входу. На третий вход схемы 14поступает сигнал разрешения при наличии в счетчике 11 остатка от деления. При отсутствии остатка деление прекращается. При наличии остатка импульсы с выхода60 схемы «И 14 поступают на вход реверсивного счетчика 4 и через делитель 13 импульсов на десять - на вход реверсивного счетчика И. С приходом в счетчик 11 количества импульсов, численно равного остатку AI,65 4 схема «И 14 закрывается по третьему входу, а триггер 12 перебрасывается в исходное состояние. Во время умножения остатка Ai на десять счетчик 7, схема сравнения 6 и реверсивный счетчик 4 работают как пересчетпая схема с коэффициентом пересчета 1 : N. Результат деления остатка Ai У, -- поступает N с выхода схемы сравнения 6 на вход распределительного блока 9, с выхода которого заносится в соответствующую декаду дробной части блока приема результата. Переброс триггера 12 воздействует на триггер 5 и вызывает переключение его в противоположное исходному состояние, в результате чего реверсивный счетчик 4 переключается в режим вычитания и схема «И 2 открывается по первому входу. При наличии остатка от деления в счетчике 4 на третий вход схемы «И 2 подается сигнал разрещения, и импульсы с выхода схемы «И 2 поступают на вход реверсивного счетчика 11 и через делитель 1 импульсов на десять - на вход реверсивного счетчика 4. Пусть остаток от де YI - равен АЗ. Число N поступает на вход пересчетной схемы (пози у, 8, И). Результат от деления Y,с выхода схемы сравнения 8 поступает через распределительный блок 9 в более младшую декаду дробной части блока приема результата. С приходом в счетчик 4 количества импульсов, равного остатку А2, схема «И 2 закрывается, а триггер 5 перебрасывается в исходное состояние, что вызывает переключение триггера 12 и при наличии остатка Аз начинается следующий цикл деления. Процесс деления прекращается с приходом сигнала запрета на вход схемы «И 15. П р ед м ет изоб р етени я .. Устройство для деления чисел, представленных в число-импульсных кодах, содержа реверсивных счетчика, выходы котоpj j, подключены ко входам соответствующих схем сравнения, другие входы которых соединены с выходами счетчика делителя, а выходы подключены к нулевым входам соответствующих реверсивных счетчиков, два делителя импульсов на десять, тактовый генератор, распределительный блок, блок приема результата, два триггера управления реверсом, логические схемы «И, «ИЛИ, отличающееся тем, что, с целью повыщения быстродействия, выход тактового генератора подключен ко входу первой схемы «И, другой вход которой соединен с выходом распределительного блока, а выход подключен к первым входам второй и третьей схем «И, второй вход второй схемы «И соединен с выходом первого триггера управления реверсом, со вторым входом второго триггера управления реверсом и входом распределительного блока; второй вход третьей схемы «И соединен с выходом второго триггера управления реверсом, со входом распределительного блока и со входом первой схемы «ИЛИ, другой вход которой соединен со входом «Окончание записи устройства, а выход подключен ко второму входу первого триггера управления реверсом; третий вход второй схемы «И подключен к пулевому выходу первого реверсивного счетчика и к первому входу первого триггера управления реверсом; третий вход третьей схемы «И подключен к нулевому выходу второго реверсивного счетчика и к первому входу второго триггера управления реверсом, выход второй схемы «И подключен ко второму входу второй схемы «ИЛИ, выход которой соединен

со входом второго реверсивного счетчика, а через делитель импульсов на десять - к третьему входу третьей схемы «ИЛИ, выход которой соединен со входом первого реверсивного счетчика; выход третьей схемы «И подключен к первому входу третьей схемы «ИЛИ, второй вход которой соединен со входом делимого устройства, а выход подключен к входу первого реверсивного счетчика и через другой делитель.импульсов на десять - к первому входу второй схемы «ИЛИ, выход которой подключен ко входу второго реверсивного счетчика; выходы схем сравнения соединены с соответствующими

входами распределительного блока, выходы распределительного блока подключепы к соответствующим входам блока приема результата.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1980 |

|

SU886254A2 |

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| Система для распределения печатной продукции по пунктам назначения | 1987 |

|

SU1618715A1 |

| Синтезатор частот | 1976 |

|

SU799101A1 |

| Устройство для проверки цифровых приборов | 1988 |

|

SU1599817A2 |

| Устройство для программного управления | 1981 |

|

SU987579A1 |

| МНОГОКАНАЛЬНЫЙ ЗНАКОВЫЙ КОРРЕЛОМЕТР | 1999 |

|

RU2177637C2 |

| Устройство тактовой синхронизации | 1980 |

|

SU906016A1 |

| Генератор случайных процессов | 1981 |

|

SU955048A1 |

| ПРОТИВОУГОННАЯ СИСТЕМА | 1995 |

|

RU2086437C1 |

Авторы

Даты

1974-11-15—Публикация

1973-01-08—Подача