Изобретение относится к синтезато рам частот и может использоваться в приемо-передающих и радиоизмерител ных устройствах. По основному авт.св. К 799101 известен синтезатор частот, содержащий опорный генератор (ОТ), делитель частоты с фиксированным коэффициен-. том деления (ДФКД), фазовый детектор СФД), первый фильтр нижних частот (ФНЧ), генератор, управляемый напряжением (ГУН) делитель частоты с переменным коэффициентом деления (ДПКД) и логический элемент И-2 И-2Ш1И, включенные в кольцо-фазовой автоподстройки частоты (ФАПЧ}, а также устройство для автопоиска, включенное параллельно кольцу ФАПЧ и состоящее из последовательно соединенных блока для выделения разностной частоты, первого Й5 триггера реверсивного счетчика (PCj, цифроаналогового преобразователя (ЦАГр и второго фильтра нижних частот ;(ФНЧ), а также первый, второй, тре;Тий и четвертый логические злемен- ты И-НЕ, второй и третий Я5-триггеры и ЗК-триггер ГО. Однако такой синтезатор частот обладает ограниченньтм быстродействием. Цель изобретения - повышение быстродействия . Указанная цель достигается тем, что в синтезатор частот, содержащий опорный генератор, делитель частоты с фиксированным коэффициентом деления, фазовый детектор, первый фильтр нижних частот, генератор, управляемый напряжением, делитель частоты с переменным коэффициентом деления и логический элемент И-2И-2ИЛИ, включенные в кольцо фазовой автоподстройки частоты СФАПЧ , а устройство для автоприска, вклв чеяное параллельно кольцу ФАПЧ и состоящее из последовательно соединенных блока для выдёлтения разностной частоты.

первого й5-григгера, реверсивного счетчику, цифроаналогового преобразователя и второго фильтра нижних частот, а также первьй, второй, третий и четвертый логические элемеиТы И-НЕ, второй и третий RS -триггеры и JK-триггер, введен также блок управления сбросом, между инверным выходом четвертого Й5-триггера и i -входом управлякнцего JK-триггера введены последовательно соединенные дополнительньй реверсивный счетчик с переменным коэффициентом пересчета, второй вход которого подключен к первому выходу блока управления сбросом, и дешифратор, а между четвертым выходом делителя частоты с фиксированным коэффициентом деления и тактовым входом дополнительног реверсивного счетчика с переменным коэффициентом пересчета, введен пятый логический элемент И-НЕ, второй вход которого соединен с R-входом третьего RS-триггера, с первым входом блока управления сбросом и с прямым выходом управляющего Л К-триггера. При этом второй и третий входы блока управления сбросом соединены соответственно с первым и вторым выходами блока для выделения разностной частоты, второй вход дешиф19атора подключен к инверсному выходу четвертого RS-триггера, а третий - ко второму выходу блока управления сбросом

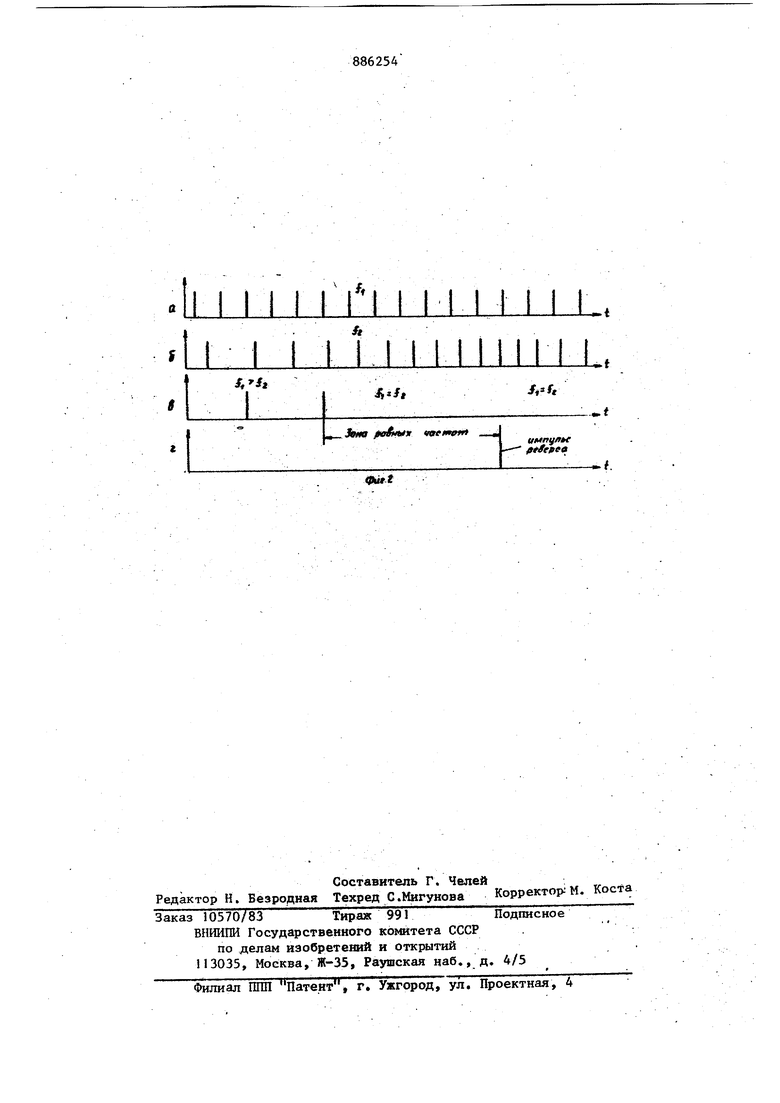

На фиг.1 представлена структурная электрическая схема предлагаемого синтезатора частот: на фиг,2 - временные диаграммы, поясняющие его работу.

Синтезатор частот содержит опорньй генератор 1, делитель 2 частоты с фисированным коэффициентом деления, фазовый детектор 3, первый фильтр 4 НИЖ1ШХ частот, генератор 5,управляемый напряжением, делитель 6 частоты с переменным коэффициентом деления и логический элемент Й-2И-2ИЛИ 7, включенные в кольцо ФАПЧ, устройство для автопоиска, включенное параллельно кольцу ФАЛЧ и состоящее из последовательно соед 1неннык блока 8 для вьщеления разностной частоты, первого RS-триггера 9, реверсивного счетчика 10, цифроаналогового преобразователя 11 и второго фильтра 12 нижних частот, а также первый, второй, третий, четвертый и пятый логические элементы И-НЕ 13,14,15, 16 и 17, второй, третий и четвертый

RS-триггеры 18,19 и 20, блок 21 уп равления сбросом, дополнительны реверсивный счетчик 22, дешифратор. 23 и управляющий JK-триггер 24,

Устройство работает следующим образом.

При нарушении синхронизма первый же импульс с одного из выходов блока 8,для выделения разностной частоты поступит на второй или третий вход блока 21 управления сбросом и заблокирует прохождение через третий или второй вход импульсов с другого выхода блока 8 дпя выделения разностной частоты,

Одновременно этот же импульс пройдет через первьй выход блока 21 управления сбросом на второй вход дополнительного реверсивного счетчика 22 и сбросит его в начальное состояние. После этого дополнительный реверсивный счетчик 22 тактовыми импульсами, поступакнцими на его тактовый вход через открытый пятый логический элемент И-НЕ 17 с четвертого выхода ДФКД 2, заполняется до сброса очередным импульсом разностной частоты, который приходит с того же выхода блока 8 для выделения

J разностной частоты через блок 21 управления сбросом, Дополнительньй реверсивный счетчик 22 с двумя фиксированными значениями коэффициента пересчета осуществляет деление входной тактовой частоты либо на больший N 5 (при сложении, либо меньщий }(д (при выдатании) коэффициент пересчета. Причем . При работе дополнительного реверсивного счетчика 22 на сложе1ше на выходе его получается двоичное число, пропорциональное интервалу между импульсами разностной частоты (импульсами сброса) ,-Частота тактовых импульсов,йоступаюпщх на второй вход дополнительного реверсивного счетчика 22 У( значительно больше частот импульсов с первого и третьегсР выходов ДФКД 2, Заполнение и сброс дополнитепьного реверсивного счетчика 22 продолжается до тех пор, пока система не войдет в зону отсутствия импульсов разностной частоты ({.и i частоты сигналов на входах блока 8 дли выделения разностной частоты

на фиг.2«||5, зона равных частот на фиг,28,О и появится импульс реверса, С поступлением импульса реверса с выхода RS-триггеpa 20 на первый вход дополнительного реверсивного счетчика 22 последний не сбрасывается, а изменяет направление счета со сложения на вычитание и одновременно уменьшается его коэффициент пересчета в 2 раза (с Ng на f). От импульса реверса ,RS-триггер 9 опрокинется в противоположное состояние и подаст на реверсивный счетчик 10 команду счета в обратном направлении, вследствие чего ЦАП 11 будет выдавать на второй вход ГУН 5 такое управляющее .напряжение, при котором соотношение частот на входах блока 8 для выделения разностной частоты будет изменяться от состояния перерегулировани к состоянию равенства частот (фиг.25 Поскольку коэффициент пересчета дополнительного реверсивного счетчика 22уменьшился в два раза, то при том же числе тактовых импульсов, которое раньше поступило на его вход в режиме сложения в интервале от последнего импульса сброса до импуль са реверса (т.е. в интервале зоны равных частот), дополнительный реверсивный счетчик 22 придет в началь ное состояние в момент,когда система окажется в середине зоны равных частот. Импульс реверса,поступающий также на первый вход дешифратора 23, разрешает выход сигнала О, который формируется дешифратором 23 в момент прихода дополнительного реверсивного счетчика 22 в начальное состояние Логический О с выхода дешифратора 23поступает на Д-вход управляющего ЭК-триггера 24 и опрокидывает его в состояние О на прямом выходе. Этот О, поступая на первый вход блока 21 управления сбросом, снимает блокировку по второму или третьему его входу и формирует на его втором выходе команду, которая поступает на третий вход дешифратора 23 и запр щает выход сигнала Логический О, Управляющий ЦК-триггер 24 отключает автопоиск и включает кольцо ФАПЧ в момент, когда система находится в се редине зоны равных частот. Использование предлагаемого синтезатора частот обеспечивает значи тельный вьшгрыш во времени установления синхронизма по сравнению с известным. В известном синтезаторе частот уменьшить время работы кольца ФАШ1 можно было, если бы автопоис останавливался в зоне равных частот 4С (точнее в ее середине, но при этом нет никаких данных для его остановки, так как в этой зоне отсутствуют импульсы разностной частоты. Поэтому система уходит из зоны равных частот в зону перерегулирования, пока не появляется импульс реверса. Автопоиск отключается и система с помощью ФАПЧ возвращается в состояние синхронизма. При этом получается выигрьш во времени установления синхронизма, так как общее время вхождения в синхронизм складывается из двух составляющих:1о5,. ЧАПЧ - время работы автопоиска; 1(, время работы ФАПЧ. Поскольку д «fcфдf , то можно C4HTaTb-fc(5jr j A;-fcjj)n4 . Причем можно разделить на две составляющие ±. J 4t ФАПЧ время работы кольца ФАПЧ от состояния перерегулирования до прихода в середину зо1зы равных частот; время работы кольца ФАПЧ с момента прихода системы в середину зоны равных частот до установления синхронизма (т.е. подстройка по фазе) . На практике обычно-Ьфд .Тогда в известном синтезатоPe-to{rai,.K e tiAfl4+ iAn4.,,i н предлагаемом -to6iu, td6r Oтcюдaio5|ц . Таким образом,-в предложенном синтезаторе частот увеличено быстродействие. Формула изобретения Синтезатор.частот по авт.св. № 799101, отличающийся тем, -что, с целью повьшгения быстродействия, в него введен блок управления сбросом, между инверсным выходом четвертого RS-триггера и R-входом управляющего ЗК-триггера введены последовательно соединенные дополнительный реверсивный счетчик с переменным коэффициентом пересчета, второй вход которого подключен к первому выходу блока управления сбросом, и дешифратор, а между четвертым выходом делителя частоты с фиксированным коэффициентом деления и тактовым входом дополнительного реверсивного счетчика с переменным коэффициентом пересчета, введен также . пятый логический элемент Й-НЕ., второй вход которого соединен с входом третьего RS-триггера,с пер.вым входом блока управления сбросом .и с пря№1м выходом управляющего JKтриггера, при этом второй и третий входы блока управления сбросом соединены соответственно с первым и вторым выходами блока для выделения разностной частоты, второй вход дешифратора подключен к инверсному выходу четвертого RS-триггера, а .третий - ко второму выходу блока управления сбросом.

Источники информации, принятые во внимание при экспертизе

I. Авторское свидетельство СССР № 799101, кл. Н 03 В 21/02, 26.11.76

.|| I III Г IM I III III.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1976 |

|

SU799101A1 |

| Синтезатор частот | 1979 |

|

SU879733A2 |

| Синтезатор частот | 1977 |

|

SU758528A1 |

| Цифровой синтезатор частот | 1987 |

|

SU1469554A1 |

| Цифровой синтезатор частот | 1987 |

|

SU1510080A1 |

| СИНТЕЗАТОР ЧАСТОТ | 2010 |

|

RU2434322C1 |

| УСТРОЙСТВО КОНТРОЛЯ СИНХРОНИЗМА КОЛЬЦА ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ | 1993 |

|

RU2057395C1 |

| Умножитель частоты | 1990 |

|

SU1797113A1 |

| Умножитель частоты следования импульсов | 1987 |

|

SU1636983A1 |

| Способ определения частотной характеристики испытуемого объекта и устройство для его осуществления | 1984 |

|

SU1223074A1 |

Авторы

Даты

1981-11-30—Публикация

1980-01-14—Подача