1

Изобретение относится к преобразователям перемещения в коды, использующим метод последовательного счета элементарных приращений кодируемых величин.

Известен «-канальный преобразователь перемещения в код, содержащий п пар датчиков перемещения, коммутатор, два триггера, вход каждого из которых соединен с выходом одного из каждой пары датчиков, два вентиля, подключенные к выходам триггеров, два регистра сдвига и блок управления, один из выходов которого подключен к входу коммутатора, а второй - ко входам вентилей.

Быстродействие известного преобразователя ограничено условием, чтобы за время, равное периоду опроса датчиков, любое из перемещепий изменялось не более, чем па четверть щага прямоугольного сигнала датчика.

Кроме того, известный преобразователь неравномерно потребляет ток от источника питания, поскольку коды перемещений, циркулирующие в регистрах сдвига, меняются произвольным образом.

С целью увеличения скорости преобразования и повышения равномерности потребления питания в преобразователь введены вычитателн, инверторы, вентили, сумматор по модулю 2 и элементы задерл ки, причем выход каждого вентиля через последовательно включенные вычитатель, регистр сдвига, дополнительный вентиль и элемент задержки соединен со входом другого триггера, выход каждого регистра сдвига через инвертор соединен со вторым входом вычитателя, включенного на входе другого регистра сдвига, один из входов сумматора соединен с выходом вычитателя непосредственно, а другой вход сумматора соединен с выходом другого вычитателя через последовательно включенные регистр сдвига, дополнительный вентиль и третий элемент задержки, а другие входы дополнительных вентилей, инверторов и третьи входы вычитателей соединены с выходами блока управления.

Предлагаемый преобразователь обладает быстродействием, нревыщающим вдвое быстродействие известного преобразователя при одинаковой разрещающей способности и одинаковой частоте опроса - датчиков, содержит

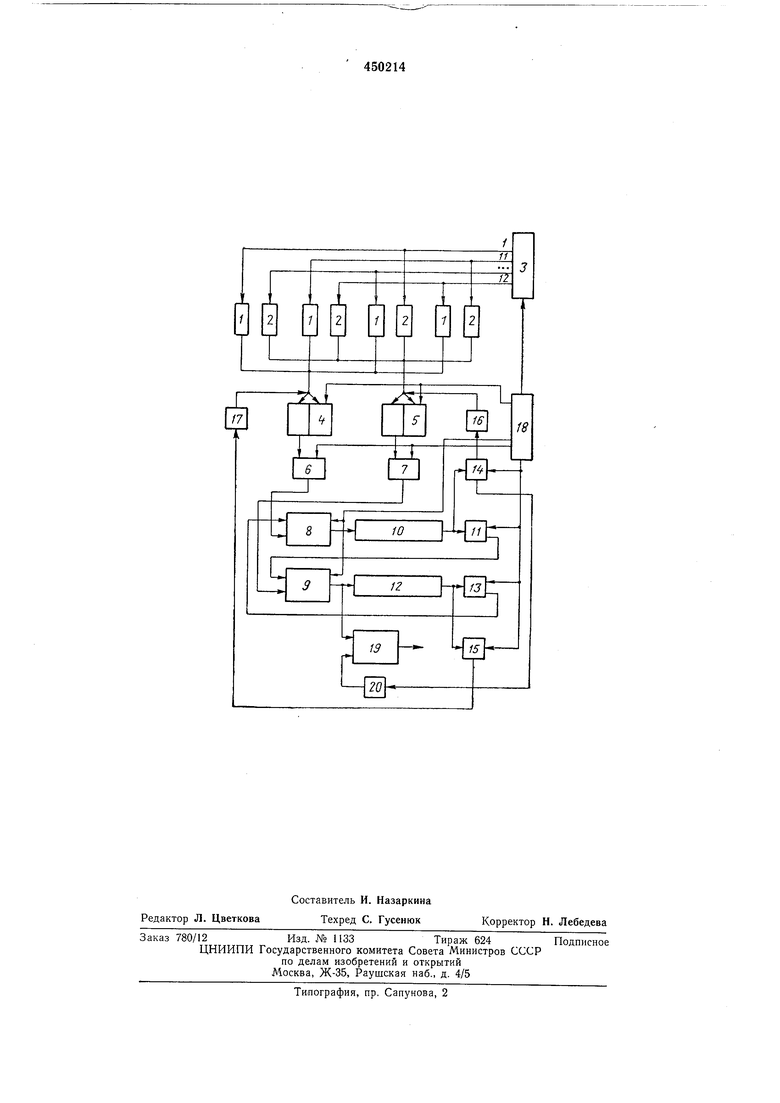

на 2л запоминающих элементов меньше, чем известный, и равномерно потребляет ток, что позволяет снизить мощность источника питания. Блок-схема предлагаемого «.-канального

преобразователя перемещений в коды изображена на чертеже.

Преобразователь включает «-датчиков перемещений 1 и п датчиков перемещений 2, причем каждому перемещению соответствует пара датчиков, состоящая из датчика 1 и датчика 2. Датчик 1 из т-пары подключен к твыходу коммутатора 3, а датчик 2 из этой же

. я / п пары - к выходу с номером т + -( т1

(при нумерации выходов коммутатора по порядку следования выходных сигналов). Выходы всех датчиков 1 объединены и подключены к счетному входу триггера 4. Выходы всех датчиков 2 также объединены и нодключены к счетному входу триггера 5. Выходы триггеров через вентили 6 и 7 соединены с первыми входами вычитателей 8 и 9. Выход вычитателя 8 через последовательно соединенные регистр сдвига 10 и инвертор 11 подключен к второму входу вычитателя 9, а выход вычитателя 9 через носледовательно соединенные регистр сдвига 12 и инвертор 13 подключен к второму входу вычитателя 8. Выходы регистров сдвига 10 н 12, кроме -того, подключены соответственно через вентили 14 и 15 и последовательно соединенные с ними элементы задержки 16 и 17 к счетным входам триггеров 5 и 4. Вход коммутатора, другие входы триггеров, инверторов, вентилей и третьи входы вычитателей соединены с выходами блока управления 18. Сумматор 19 одним из входов подключен непосредственно к выходу вычитателя 9, а другой вход сумматора через элемент задержки 20 подключен к выходу вентиля 14, соединенного с выходом регистра сдвига 10.

Преобразователь работает следующим образом.

Моменты опроса любого датчика 1 сдвинуты относительно моментов опроса датчика 2 того же канала на половину периода опроса. Состояния датчиков 1 поочередно фиксируются триггером 4, а состояния датчиков 2 фиксируются другим триггером 5. С выходов триггеров двоичные последовательности состояний датчиков подаются через вентили б и 7 и вычитатели 8 и 9 на входы регистров сдвига 10 и 12 и задерживаются в этих регистрах на половину периода опроса. С выходов регистров сдвига последовательности состояний датчиков поступают на инверторы 11 и 13 и вентили 14 и 15 с элементами задержки 16 и 17. Сигналы с выхода блока унравления 18 гасят в инверторах информацию о состояниях датчиков и разрешают прохождение этой информации через вентили на счетные входы триггеров 4 и 5. При этом последовательность состояний датчиков, сформированная одним из триггеров, пройдя через регистр сдвига, поступает на счетный вход другого триггера. Триггеры, кроме указанной выше операции формирования двоичных последовательностей состояний датчиков, производят также суммирование по модулю 2 состояний датчиков 1 с задержанными в регистрах сдвига (на половину периода опроса) состояниями датчиков 2 и состояний датчиков 2 с задержанными состояниями датчиков 1. В регистрах сдвига 10 и 12 хранятся /7-разрядные носледовательные коды перемещений п-каналов, причем первые

разряды кодов используются для запоминания состояний датчиков.

Цикл работы преобразователя соответствует одному периоду коммутатора, в течение которого происходит опрос всех датчиков и формирование кодов приращений во всех каналах. Процесс формирования кодов перемещений удобно рассмотреть на примере одного канала в течение одного цикла.

Перед опросом датчиков сигнал с блока 18 производит установку в «О триггеров 4 и 5. Сигнал коммутатора 3 опрашивает состояние датчика 1, и результат опроса фиксируется в триггере 4. Через вентиль 6 состояние триггера 4 поступает на первый вход вычитателя 8. Па второй вход вычитателя 8 с выхода регистра 12 через инвертор 13 поступает первый разряд кода данного перемещения, в котором было записано состояние датчика 2 этого же канала в середине предыдущего цикла. Поскольку на инверторе 13 первый разряд кода стирается сигналом с блока 18, то в данном также на второй вход вычитателя 8 всегда поступает код «О, и в первый разряд записывается состояние датчика 1. В этом же такте первый разряд кода через вентиль 15 поступает на вход элемента задержки 17. Во втором такте выходной сигнал элемента задержки 17 поступает на счетный вход триггера 4. При этом происходит суммирование по модулю 2 кода текущего состояния датчика 1 с кодом предыдущего состояния датчика 2. Результат суммирования через вентиль 6 поступает на первый вход вычитателя. Па второй вход вычитателя 8 в качестве уменьшаемого поступает второй разряд кода перемещения с выхода регистра 12 через инвертор 13. При этом вентиль 15 закрыт. В следующих тактах на второй вход вычитателя 8 последовательно поступают остальные разряды кода перемещения данного канала, складываясь в вычитателе с единицами засма, если они получаются при формированни второго разряда кода перемещения, при этом вентиль 6 остается закрытым. С выхода вычитателя 8 разряды кода перемещения последовательно поступают в регистр сдвига 10. Единица заема при формировании последнего разряда кода гасится сигналом, поступающим на третий вход вычитателя с выхода блока 18.

Далее аналогичным образом опрашивается датчик 1 следующего канала и т. д.

Через ноловину периода работы коммутатора, когда младший разряд кода рассматриваемого канала появится на выходе регистра 10, происходит опрос датчика 2 этого же канала. Результат опроса фиксируется в триггере 5 и через вентиль 7 и вычитатель 9 записывается в младший разряд кода перемещения, формируемого в регистре 12, вместо кода, соответствующего датчику 1 в начале цикла.

Аналогично описанному выше процессу происходит сложение по модулю 2 состояния датчика 2 с состоянием датчика 1 в начале цикла. Результат сложения вычитается из второго разряда кода перемещения в вычитателе 9, а единица заема вычитается из старших разрядов этого кода и гасится при формировании последнего разряда.

Следующий цикл начинается опросом датчика 1 рассматриваемого капала в момент появления па выходе регистра 12 младщего разряда кода данного перемещения.

В сумматоре 19 производится уточнение кодов перемещений путем сложения по модулю 2 состояния датчика 2, соответствующего средине цикла с состоянием датчика 1, соответствующего началу цикла, и записи результата в первый разряд выходного кода. Все старщие разряды кода, начиная со второго, ггереписываются с выхода вычитателя 9 в сумматор 19 без изменения, так как в это время вентиль 14 закрыт. Выход сумматора является выходом преобразователя.

Преобразователь устроен так, что одновременно с опросом датчика 1 канала т происходит опрос датчика 2 канала т-{.

Инверторы 11 и 13 предназначены для преобразования прямых кодов в обратные и наоборот. В результате двойного инвертирования кодов в течение цикла работы преобразователя в одном из регистров хранятся прямые коды перемещений, а в другом - обратные, т. е. каждая «I кода половину своего нути проходит в виде «О, а «О - в виде «1. При построении регистров сдвига на импульсных элементах (например, ферротранзисторных модулях) введение инверторов приводит к выравниванию потребления тока от источника питания.

Предмет изобретения

Многоканальный преобразователь перемен рния в код, содержащий в каждом канале два датчика перемещения, входы которых соединены с коммутатором, а выходы - со входами триггеров, вентили, подключенные к выходам триггеров, регистры сдвига и блок управления, один из выходов которого подключен ко входу коммутатора, а второй - ко входам вентилей, отличающийся тем, что, с целью увеличения скорости преобразования и повышения равномерностн потребления питания, в него введены вычитатели, инверторы вентили, сумматор по модулю 2 и элементы задержки, причем выход каждого вентиля через последовательно включенные вычитатель, регистр сдвига, дополнительный вентиль и элемент задержки соединен со входом другого триггера, выход каждого регистра сдвига через инвертор соединен со вторым входом вычитателя, включенного на входе другого регистра сдвига, один из входов сумматора соединен с выходом вычитателя непосредственно, а другой вход сумматора соединен с выходом другого вычитателя через последовательно включенные регистр сдвига, дополнительный вентиль и третий элемент задержки, вторые входы дополнительных вентилей, инверторов и третьи входы вычитателей соединены с выходами блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный преобразователь разности частот в код | 1975 |

|

SU590849A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| Спектроанализатор кардиосигналов | 1984 |

|

SU1170371A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2006 |

|

RU2309430C1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2004 |

|

RU2260195C1 |

| Устройство для отображения информации | 1972 |

|

SU458004A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2019 |

|

RU2713624C1 |

| Фазометр | 1991 |

|

SU1817037A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Преобразователь код-сдвиг фазы | 1972 |

|

SU439917A1 |

Авторы

Даты

1974-11-15—Публикация

1972-11-27—Подача