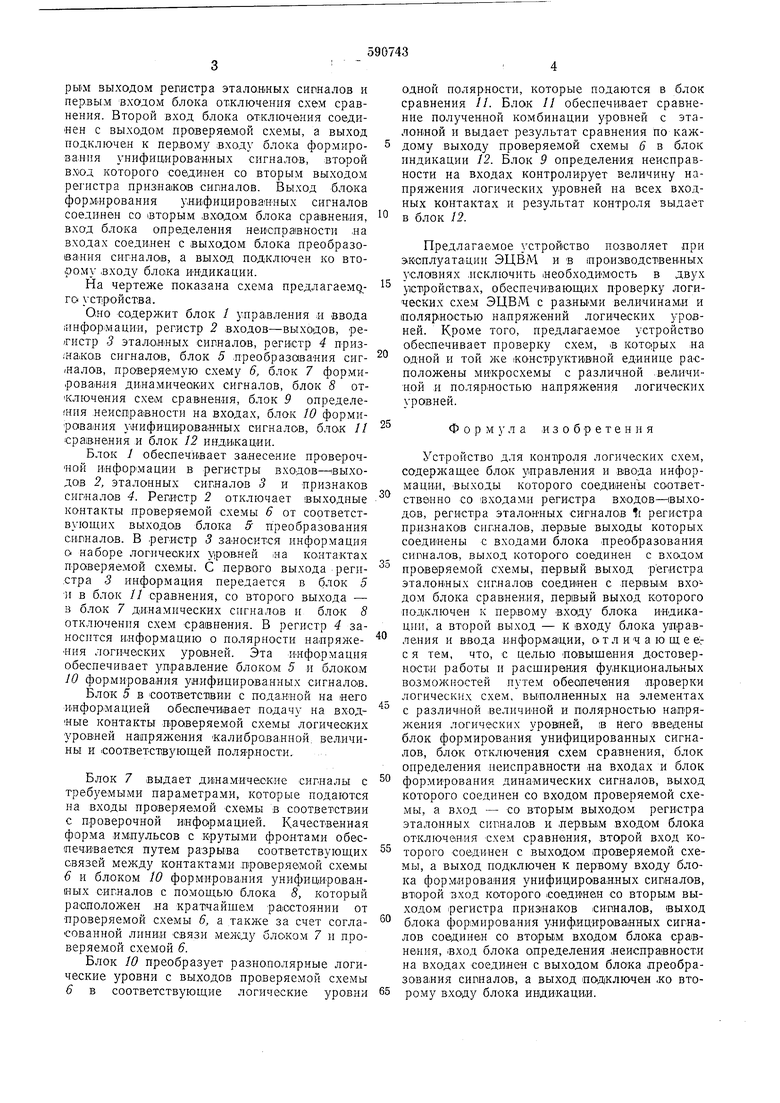

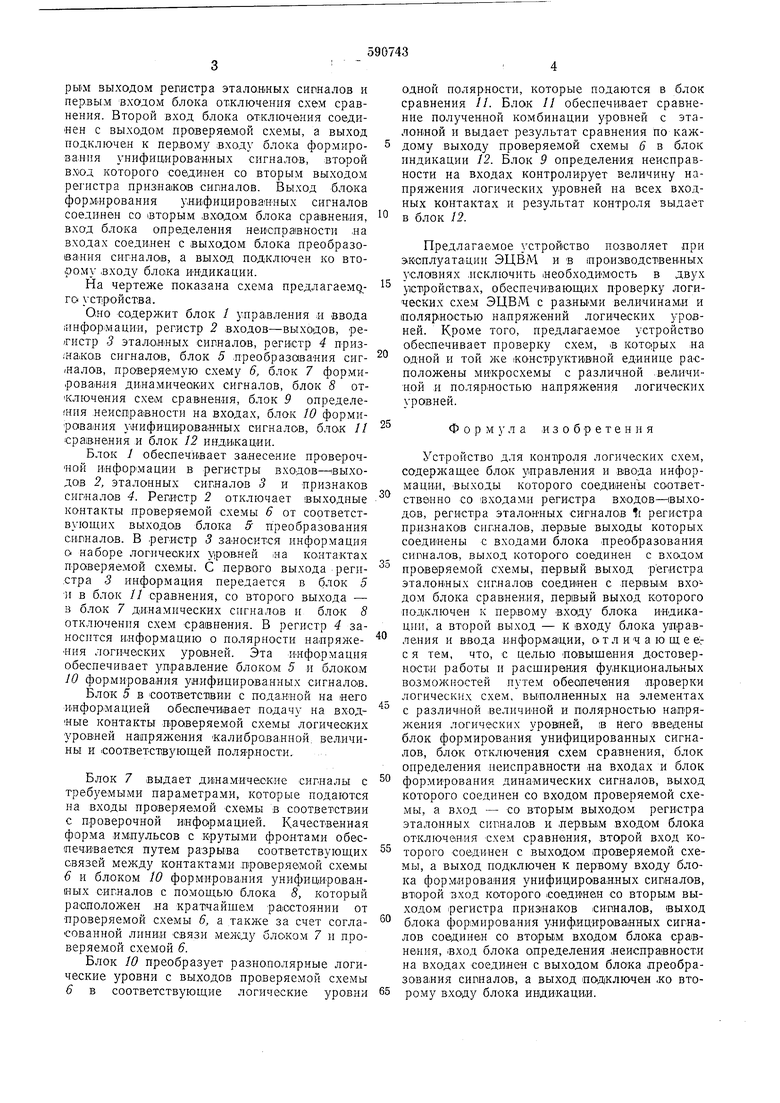

Изо|бретение относится к области вычислительной техники и может быть использовано для nipOiBepKH испраВНости и ремонта логических цифровых схем. Известно устройство для контроля работы дискретных объектов, содержащее блок ввода, блок управления, блок формирования входных воздействий, ко.ммутатор, блок сопряжения, блок анал.иза н результатов контроля, генератор имлульсов, распределитель сигналов, распределитель импульсов, ключи, блО|К коММутации и сборку 1. Это устройство не позволяет проверять логические схемы .на элементах с различ«ой величиной и полярностью напряжения логических уровней. Известно устройство контроля дискретных логических схем, содержащее двоичный счетчик, генератор импульсов, разделительные схемы, триггер неисправности, индикаторные элементы, два элемента И, формирователь стробирующих импулвсов, два элемента ИЛИ, комларатор, схему контроля уровней, нреобразователь и элемент ИЛИ-НЕ 2. Для работы такого зстройства необходимо иметь иоправиую логическую схему, аналогичную проверяемой. Из известных устройств наиболее близким к изобретению является устройство для нахождения неиспра1вностей в электронных схемах, содержащее блок управления ,и ввода и.нформацин, вы.ходы которого соединены с входами регистра входов-выходов, регистра эталонных сигналов и регистра признаков сигналов. Первые выходы регистров соединены хо вх1одам,и блока лреобразования сигналов, выход которого соединен со входо.м проверяемой схемы. Первый выход регистра эталонных сигналов соединен с нервым входо-м блока сравнения, лервый выход которого подключен к перво.му вхо1ду блока индикации, а второй выход - к входу блока управления и ввода информацни 3. Это устройство также не позволяет проверять логические схе,мы, выполненные на элементах с различной величиной и полярностью напряжения логических уровней. Пелью изобретения является повышение достоверности работы и расширение функциональных возможностей путем обеспечения проверки логических схем, выполненных на элементах с различной величиной и полярностью напряжения логических уровней. Поставленная цель достигается тем, что в устройство введены блок формирования унифицированных сигналов, блок отключения схем сравнения, блок определения неисправности на входах и блок формирования динамических сигналов, выход которого соединен со входом проверяемой схемы, а вход - со вторым выходом регистра эталолных сипналов и первы.м входом блока отключения схем сравнения. Второй вход блока 01тключвния соединен с выходом проверяемой схемы, а выход подключен к первому входу блока формирования унифицированных сигналов, второй вход которого соединен со вторым выходом регистра ирпз:на1кав сипналов. Выход бло«а форм ирования унифицироваиных сигналов соединен со вторым входам блока сравнения, вход блока определения неисправности ,на входах соединен с выходом блока преобразования сигналов, а выход подключен ко второму входу блока индикации. На чертеже показана схема предлагаемдго уст;р1ойства. Оло содержит блок / управления и ввода 1инфор мации, регистр 2 входов-выходов, ре)гистр 3 эталоиных сигналов, регистр 4 призiHaiKOB сигналов, блок 5 .преобразования сигналов, проверяемую схему 6, блок 7 форми.ровайия динамических сигналов, блок 8 от ключения cxeiM сравиения, блок 9 определения .неисправности на входах, блок 10 формирования унифицированных сигналов, блок // сра1внения и блок 12 индикации. Блок 1 обеспечивает занесение проверочной инфор|мации в регистры входов- выходов 2, эталонных сигналов 3 и признаков сигналов 4. Регистр 2 отключает выходные контакты проверяемой схемы 6 от соответствующих выходов блока 5 преобразования сипналов. В регистр 3 заносится информация о наборе логических уровней 1на контактах проверяемой схемы. С первого выхода регистра 3 информация передается в блок 5 и в блок 11 сравнения, со второго выхода - в блок 7 динамических сигналов и бло-к 5 отключения схем сравнения. В регистр 4 заносится информацию о полярности напряжения логических уровней. Эта информацпя обеспечивает управление блоком 5 и блоком 10 формирования унифицированных сигналов. Блок 5 в соответст1ви.и с пода.нной на него информацией обеспечивает подачу на входные контакты проверяемой схемы логических уровней напряжения калиброванной, величины и соответст1вующей поляр.ност.и. Блок 7 выдает динамические сигналы с требуемыми пара.метрами, которые подаются на входы проверяемой схемы в соответствии с проверочной информацией. Качественная форма импульсов с крутыми фронтами обеспечивается путем разрыва соответствующих связей между контактами .праверяемой схемы 6 и блоком 10 формирования унифицированных сигналов с помощью блока 8, который расположен .на кратчайщем расстоянии от проверяемой схемы 6, а за счет согласованной линии связи между блоком 7 и проверяемой схемой 6. Блок 10 преобразует разно.полярные логические уровни с выходов проверяемой схемы 6 в соответствующие логические уровни одной полярности, которые подаются в блок сравнения //. Блок // обеспечивает сравнение полученной комбинации уровней с эталонной и выдает результат сравнения по каждому выходу проверяемой схемы 6 в блок индикации 12. Блок 9 определения неисправности на входах контролирует величину напряжения логических уровней на всех входных контактах и результат контроля выдает в блок 12. Предлагаемое устройство позволяет при эксплуатации ЭЦВ.М и в производственных условиях .исключить необходимость в двух устройствах, обеспечивающ.их проверку логических схем ЭЦВМ с разными вел.ичинами и полярностью напряжений логических уровней. Кроме того, предлагаемое устройство обеспечивает проверку схем, в которых на одной и той же конструктивной единице расположены микросхемы с различной .величиной и полярностью напряжения логических уровней. Формула изобретения Устройство для ко.нт1роля логических схем, содержащее блок управления и ввода информации, выходы которого соединень соответственно со входами регистра входов- выходов, регистра эталонных сигналов fi регистра пр.пзнаков сипналов, первые выходы которых соединены с входами блока преобразования сигналов, выход которого соединен с входом проверяемой схемы, первый выход регистра эталонных сигналов соединен с первым входом блока сравнения, первый выход которого подключен к первому входу блока индикации, а второй выход - к входу блока управления и ввода инфopiмalции, атл ич а ю щ е вг с я тем, что, с целью повышепня достоверности работы и расщирення функциональных возможностей путем обеспечения проверки логических схем, выполненных на элементах с различ ной величиной и поляр.ностью напряжения логических уровней, в него введены блок формирования унифицированных сигналов, блок отключения схем сравнения, блок определения неисправности на входах и блок формирования динамических сигналов, выход которого соединен со входом проверяемой схемы, а вход - со вторым выходом регистра эталонных сигналов к лервым входом блока отключения схем сравнения, второй вход которого соединен с выход.ом проверяемой схемы, а выход подключен к первому входу блока формирования унифицирова.н.ных сиг|На.лов, второй вход которого соединен со вторым выходом регистра признаков сипналов, выход бло.ка формирования унифицированных сигналов соединен со вторым входом блока сравнения, вход блока опре.деления неисправности на входах соединен с выходом блока преобразования сипналов, а выход подключен ко второму входу блока индикации.

Источники и.нформаци|И, принятые во Внимание при экспертизе:

1. Авторское свидетельство СССР № 416668, кл. G 05 В 23/02, 1974.

2.Авторское свидетельствоСССР № 378852, кл. G06F 11/00, 1973.

3.Авторское свидетельство СССР № 451994, кл. G 06 F 11/00, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового диагностирования логических блоков | 1976 |

|

SU661552A1 |

| Устройство для диагностирования логических схем | 1988 |

|

SU1684757A1 |

| Устройство для контроля цифровых узлов | 1986 |

|

SU1518906A2 |

| Устройство для обмена информацией между эвм и магнитным накопителем | 1984 |

|

SU1218391A1 |

| Устройство для контроля микропроцессорных программных блоков | 1983 |

|

SU1267424A1 |

| Устройство для контроля цифровых узлов | 1982 |

|

SU1059576A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для контроля счетчиков импульсов | 1985 |

|

SU1248061A1 |

| Устройство для контроля логических блоков | 1983 |

|

SU1180904A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

Авторы

Даты

1978-01-30—Публикация

1976-04-29—Подача