; 11 Изобретение относится к вычислительной технике и предназначено для контроля цифровых узлов. Известно устройство для контроля логических схем, содержащее генератор импульсов, счетчик,вход которого соединен с выходом генератора импульсов, дешифратор, входы которого соединены с нулевым и еданичным выхо даьм разрядов .счетчика, .блок элементов совпадения, табло индикации, входы которого соединены с выходами блока элементов срвп.адения ij . Наиболее близким к предлагаемому является устройство для контроля дис кретных логических схем, содержащее генератор импульсов, счетчик, разделительные элементы, схему контроля уровней, преобразователь уровней компаратор, формирователь стробируюших импульсов, два элемента И, элемент ИЛИ, триггер, кнопку Пуск, дв индикаторных элемента, причем выход генератора импульсов соединен с входом формирователя стробирующих импульсов и со счетным входом счетчика .выходы которого соединены соответственно с входами разделительных элементов, первые выходы которых соединены соответственно с входами проверяемого блока и с входакм элемента ИЛИ-НЕ, выход которого соединен с первым входом первого элемента И, второй вход которого соединен с выхо дом элемента ИШ, входы которого соединены соответственно с вторыми .выходами разделительных элементов и с входами эталонного блока, выходы проверяемого блока соединены с входами схемы контроля уровней, выход которого соединен с первым входом компаратора, второй эход которого соединен с выходом преобразователя уровня, входы которого соединены с выходами эталонного блока, выход ком паратора соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом первого элемента И, выход элемента ИЛИ соединен с пер вым входом второго элемента И, второй вход которого соединен с выходом формирователя стробиругацих импульсов выход элемента И соединен с единичным входом триггера, выход кнопки Пуск соединен с нулевым входом триггера, прямой и инверсный выходы триггера соединены с входами соотI2ветственно первого и второго индикаторных элементов 2j . Однако в известных устройствах время контроля логических блоков, имекицих различное число входов, постоянно н равно времени контроля Логи еских блоков, имеющих допустимое максимальное число входов, которое обусловлено временем полного цикла двоичного счетчк1ка. Цель изобретения - повьшение быстродействия. Поставленная цель достигается тем, что в устройство для контроля цифровых узлов, содержащее генератор импульсов, счетчик, блок сравнения, блок компараторов напряжения, элемент И, элемент ИЛИ, триггер, причем выход генератора импульсов соединен со счетным входом счетчика и с первым входом элемента И, второй вход которого соединен с выходом элемента ИЛИ, выход элемента И соединен с единичным входом триггера, прямой и инверсный выходы триггера соединены с входами соответственно первого и второго индикаторов, введен блок перекл1ачат12лей, два компаратора, причем выходы группы выходов блока переключат(2лей соединены соответственно с установочными вхо- : нами счетчика и с управляющими входами первого и второго комм таторов, группа выходов разрядов счетчика соединена соответственно с первой группой информационных входов первого коммутатора и с первой группой информационных входов второго коммутатора, выходы проверяемого узла соединены соответственно с второй группой информационных входов первого коммутатора и с первой группой входов блока компараторов напряжения, группа выходов эталонного узла соединена с второй группой информационных входов второго коммутатора, первая группа выходов :которого соединена с первой группой входов блока сравнения, вторая группа входов которого соединена с первой группой выходов первого коммутатора, вторая группа выходов которого соединена с группой входов проверяемого узла и с второй группой входов бЛока компараторов напряжения, вторая группа выходов второго коммутатора соединена с группой входов эта-, лонного узла, выход блока компара3

торов напряжения соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом блока сравнения, выход блока переключателей соединен с нулевым входом три гера и с входом сброса счетчика.

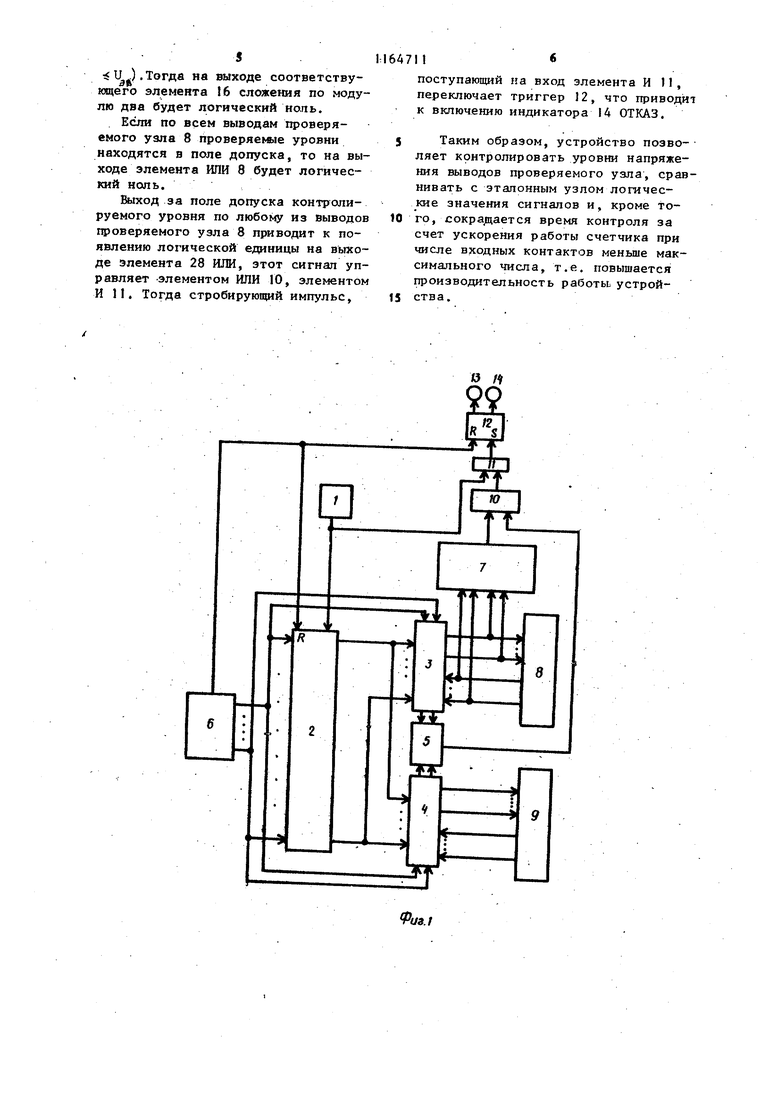

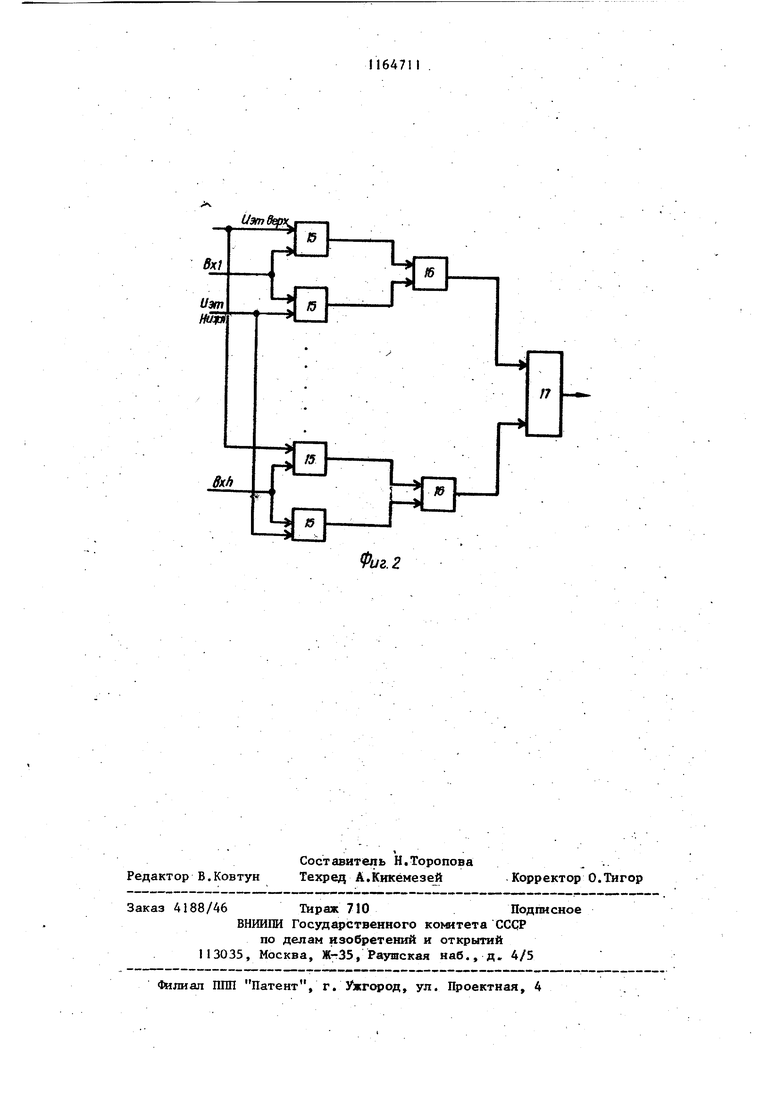

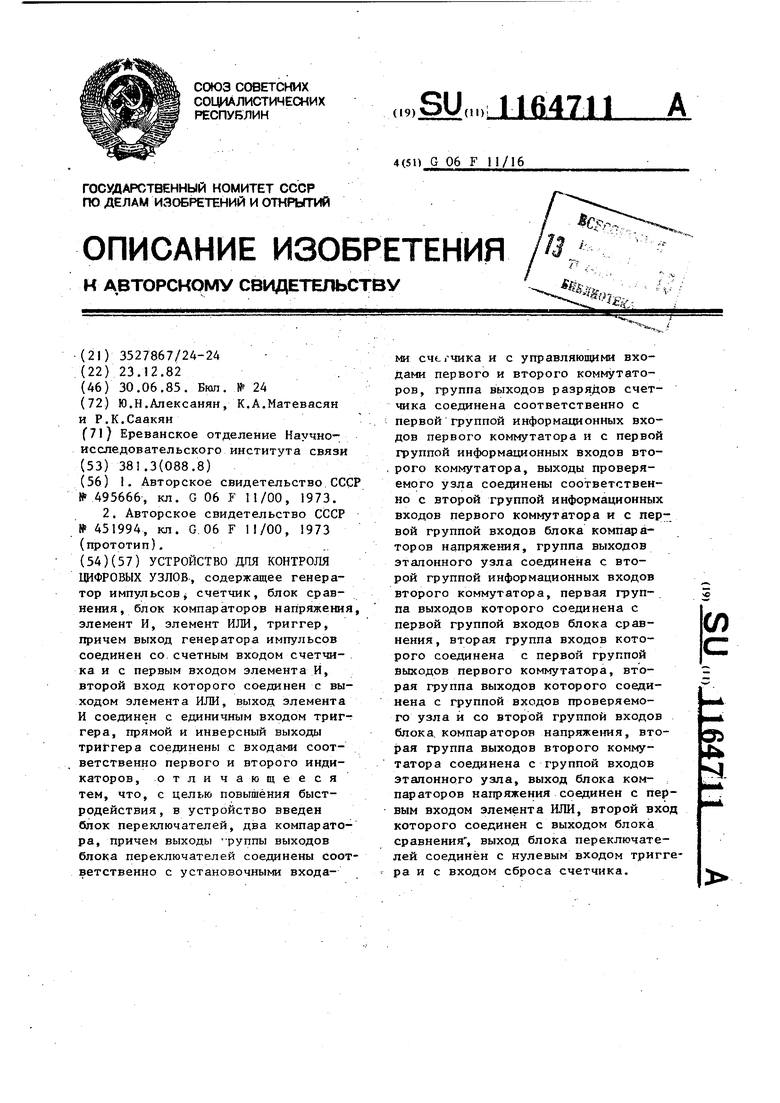

На фиг. 1 приведена схема предлагаемого устройства; на ijsir. 2 блок компараторов напряжения.

Устройство, содержит генератор 1 импульсов, счетчик 2, коммутаторы 3 и 4, блок 5 сравнения, блок 6 переключателей, блок 7 компараторов напряжения, проверяемый узел 8, эталонный узел 9, элемент ИЛИ 10, элемент И II, триггер 12, индикаторы 13 и 14.

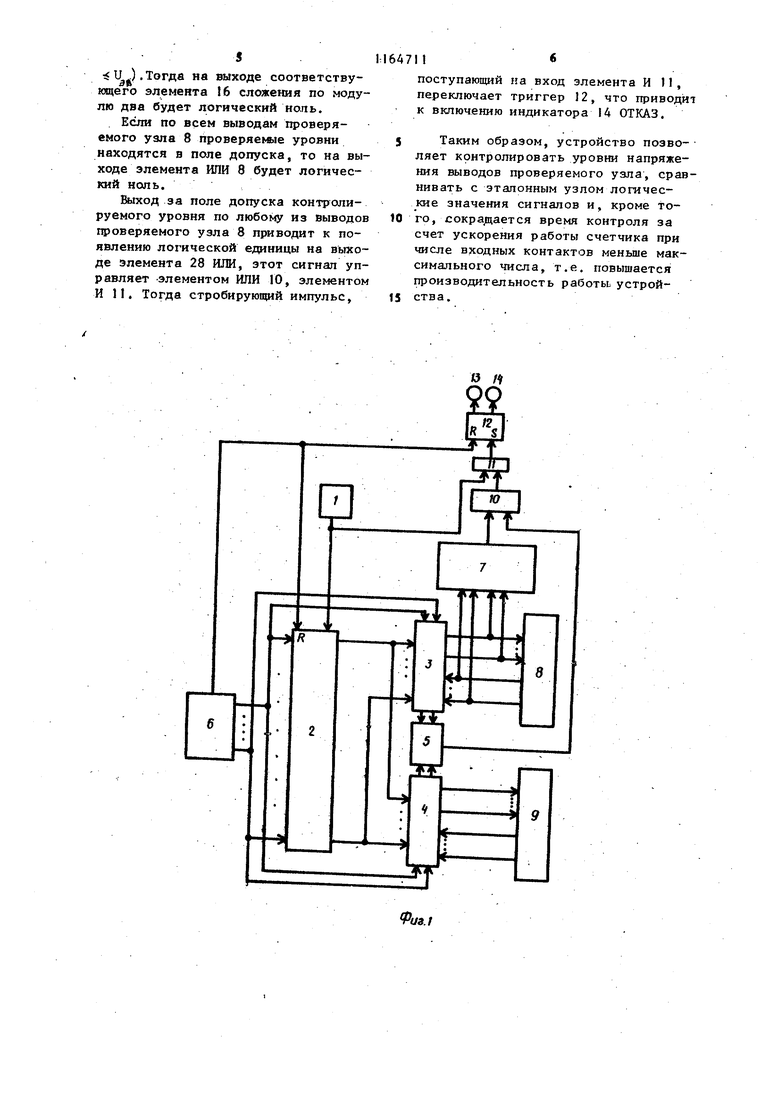

Блок 7 компараторов напряжения с держит компаратор 15, элементы 16 сложения по модулю два, элемент ИЛИ 17..

Работа устройства основана на принципе сравнения выходов проверяного.уэла 8 и эталонного узла 9 при подаче на одноименные входы обоих узлов идентичных возможных комбин.аций, одновременно осущестЕшяется контроль уровней проверяемого узла 8. При несовпадении.логических уровней на одноименных выходах узлов 8 и 9 или при обнаружении, что входно или выходной уровень проверяемого уэла 8 вышел за пределы допуска, включается индикатор 14 ОТКАЗ.

Если же проверяемый узел 8 исправлен, индикаторный элемент 13 ИСПРАВНО остается включенным.

С выхода переключателя 6 триггер 12 устанавливается в нулевое состояние, что соответствует включению индикаторного элемента 13 ИСПРАВНО, кроме того этим .сигналом сбрасывается в ноль счетчик 2.

Двоичный параллельный счетчик 2 запускается от генератора 1 импульсов.

При испытании различных логических узлов число одновременно проверяемых входов (выхцов) может меняться в пределах от 0(п) до (п-1). Установка входов (выходов)в устройстве производится посредством переключателей блока 6 переключателей.

При подаче единичных уровней с выходов группы выходов блока 6 переключателей на управляющие входы коммутаторов 3 и 4, что соответству647П4

ет входам проверяемого узла 8, коммутатор 3 осуществляет коммутацию выходов счетчика 2 .на входы проверяемого узла 8 и эталонного узла 5 9. При этом одновременно соответствующие разряды счетчиков устанавливаются в единицу.

При подаче логического нуля на управляющие входы коммутаторов 3 и 10 4 последние подключают выходы проверяемого узла 8 и эталонного узла 9 на входы блока 5 сравнения. Число выходов на время Контроля не влияет, так как контроль всех f5 выходов производится одновременно при каждом изменении входной тестовой комбинации. Время контроля зависит от количества входов испытуемых логических узлов, опреде20 ляющих длину контроль.ного теста. Максимально возможное число входов п определяет необходимое число разрядов параллельного счетчика.

При установке разрядов счетчи25 ка, соответствующих входу проверяемого узла 8, в единицу лишние для данного испытания разряды двоичного параллельного счетчика выключаются из состава счетчика (т-.е, соответственно уменьшается разрядность счетчика), и в процессе контроля эти разряды не принимают участие.

В результате, цикл счета счет35 чика сокращается, следовательно, сокращается и время контроля проверяемого узла.

Блок 7 компараторов напряжения работает следующим образом.

40Эталонные значения U, и Ug уровней напряжения подаются на первые входы компараторов 15. На вторые входы компараторов 15 поступают контролируемые уровни с выводов прове5 ряёмого узла 8,

Если UQ: и, то на выходах компараторов 15 будет логическая единица, если же Ug Ug, то на выходах компараторов 15 будет логический

0 ноль.

Таким образом, в каждом такте проверки по каждому выводу в случае, когда контролируемый уровень напряжения Ug находится в поле допуска, соответствующие выходные уровни компараторов 15 будут иметь логическую единицу (Ue U, , Ug, 1-U) либо логический ноль (,, Ug ),Тогда на выходе соответствуjon/ro элемента 16 сложения по модулю два будет логический ноль. Если по всем выводам проверяемого узла 8 проверяеьвые уровни находятся в поле допуска, то на выходе элемента ИЛИ 8 будет логический ноль. Выход за поле допуска контролируемого уровня по любому из выводов проверяемого узла 8 приводит к появлению логической единицы на выхо де элемента 28 ИЛИ, этот сигнал уп равляет элементом ИЛИ 10, элементо И П. Тогда стробирующий импульс. 1 поступающий на вход элемента И 11, переключает триггер 12, что приводит к включению индикатора 14 ОТКАЗ. Таким обраэом, устройство позволяет крнтролировать уровни напряжения выводов проверяемого узла, сравнивать с эталонным узлом логические значения сигналов и, кроме того, сокра;цается время контроля за счет ускорения работы счетчика при числе входных контактов меньше максимального числа, т.е. повышается производительность работы, устройства.

Фиг. г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для локализации неисправностей | 1980 |

|

SU903888A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU1012263A1 |

| Устройство для контроля микросхем | 1985 |

|

SU1322289A1 |

| Устройство для контроля цифровых узлов | 1982 |

|

SU1059576A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1067453A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1985 |

|

SU1302220A2 |

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1140065A1 |

| Устройство для контроля многовыходных цифровых узлов | 1984 |

|

SU1176333A1 |

УСТРОЙСТВО ДПЯ КОНТРОЛЯ ЦИФРОШХ УЗЛОВ, содержащее генератор импульсовj счетчик, блок сравнения, блок компараторов напряжения, элемент И, элемент ИЛИ, триггер, причем выход генератора импульсов соединен со. счетным входом счетчи- . ка и с первым входом элемента И, второй вход которого соединен с выходом элемента ИЛИ, выход элемента И соединен с единичным входом триггера, прямой и инверсный выходы триггера соединены с входами соответственно первого и второго индикаторов, о т л и чающееся тем, что, с целью повышения быстродействия, в устройство введен блок переключателей, два компаратора, причем выходы руппы выходов блока переключателей соединены соответственно с установочными входа -../ ми счсгчика и с управляющими входами первого и второго коммутаторов, группа выходов разрядов счетчика соединена соответственно с первой группой информационных входов первого коммутатора и с первой группой информационных входов вто, рого коммутатора, выходы проверяемого узла соединены соответственно с второй группой информационных входов первого коммутатора и с первой группой входов блока компараторов напряжения, группа выходов эталонного узла соединена с второй группой информационных входов второго коммутатора, первая груп- . па выходов которого соединена с (Л первой группой входов блока сравнения, вторая группа входов которого соединена с первой группой выходов первого коммутатора, вторая группа выходов которого соединена с группой входов проверяемого узла и со второй группой входов блока, компараторов напряжения, втосп 4: Ы рая группа выходов второго коммутатора соединена с группой входов эталонного узла, выход блока ком- , параторов напряжения соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом блока сравнения , выход блока переключателей соединён с нулевым входом триггера и с входом сброса счетчика.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля комбинационных схем | 1973 |

|

SU495666A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля дискретных логических схем | 1973 |

|

SU451994A1 |

| G | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-06-30—Публикация

1982-12-23—Подача