1

И.зобретение относится к области автоматики и вычислительной техники. В частности, оно может быть применено в схемах управления установками иепрерывного транспорта.

Известны устройства динамической памяти, построенные на трех или более элементах, например, феррит-транзисторных и работающие под воздействием тактовых имиульсов. Они имеют два устойчивых состояния, различающиеся генерацией или отсутствием геиерации сигнала на входе.

Для построения динамической памяти с двумя устойчивыми состояииями требуется ие менее трех элементов, а для получения устройства с п устойчивыми состояииями - несколько соединенных в схему счетчика устройств дииадМической памяти и дещифратор.

Цель изобретеиия - расширение функциональных возможностей устройства.

Это достигается тем, что выходы всех эле.меитов объединены и соединены с вторыми считывающими входами каждого из элементов.

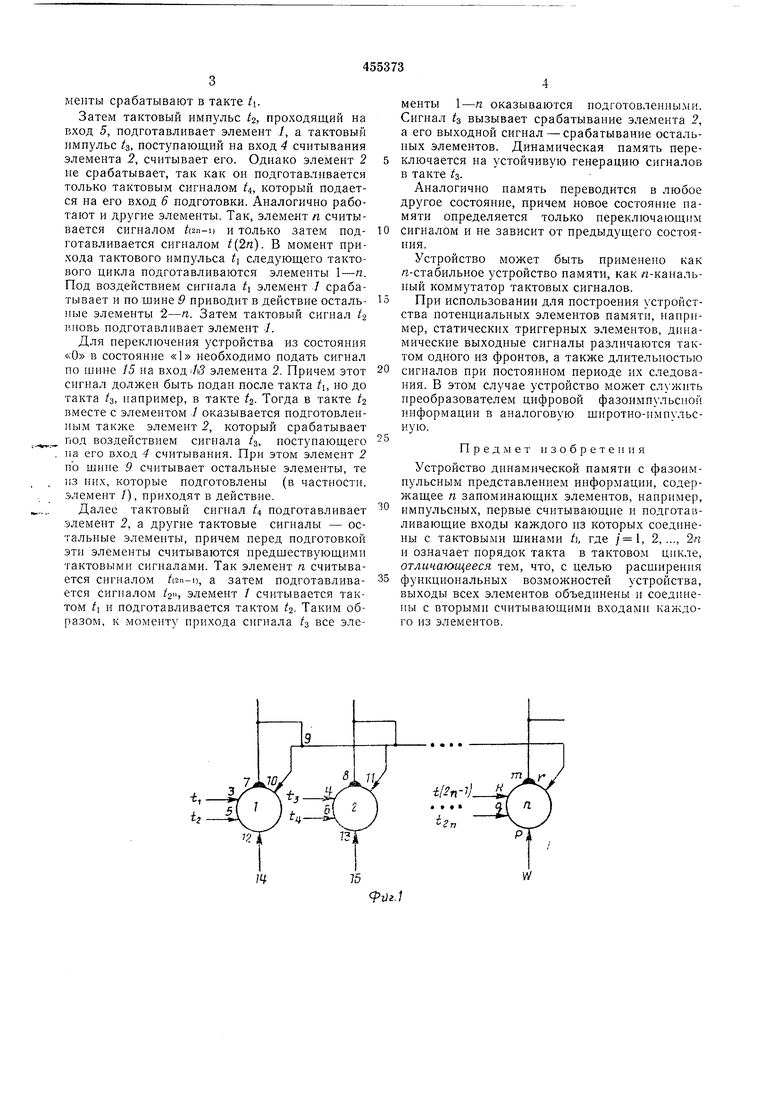

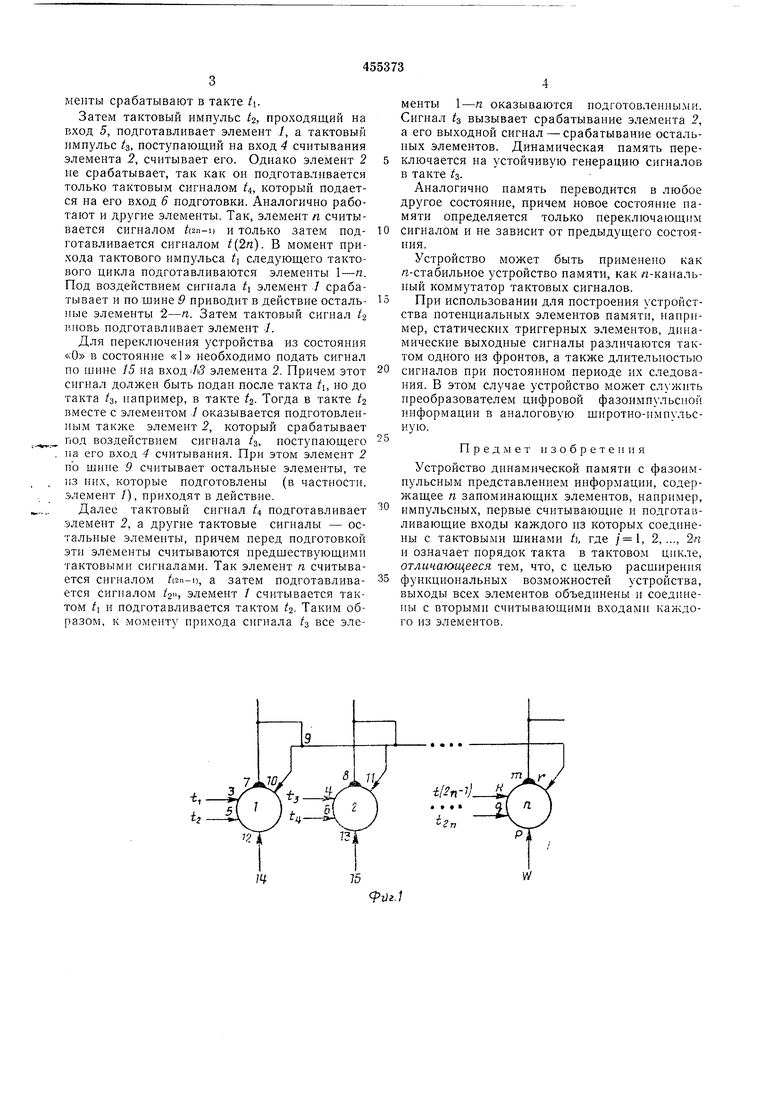

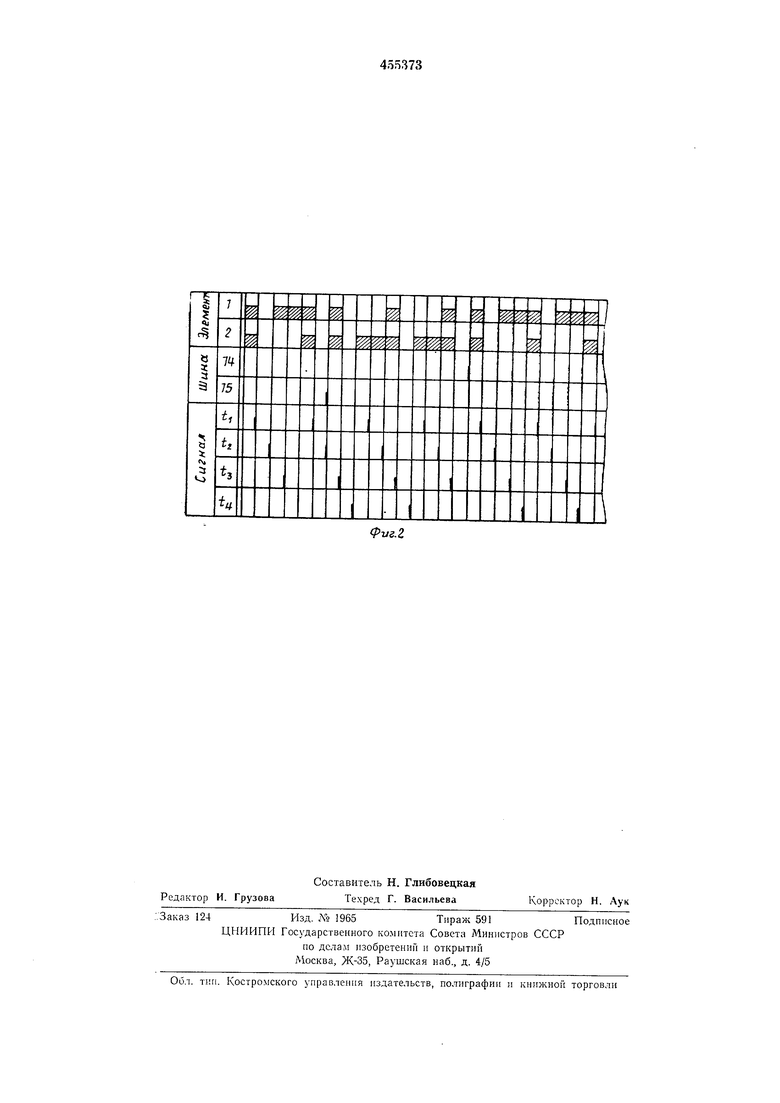

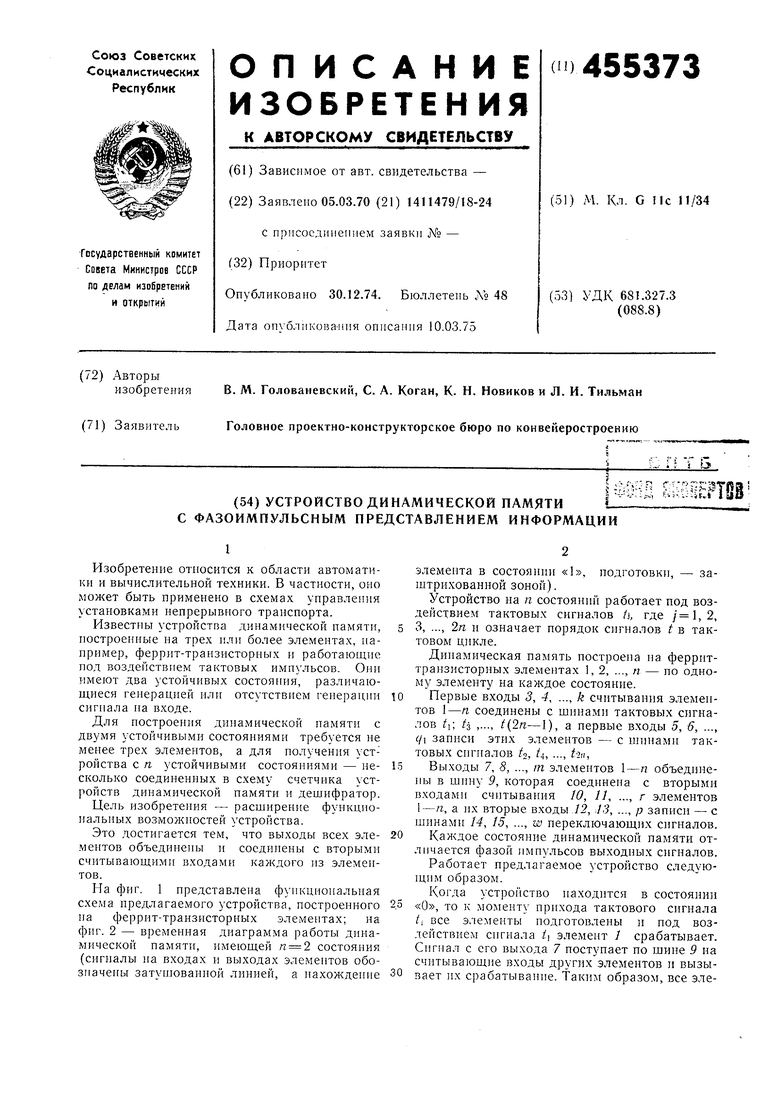

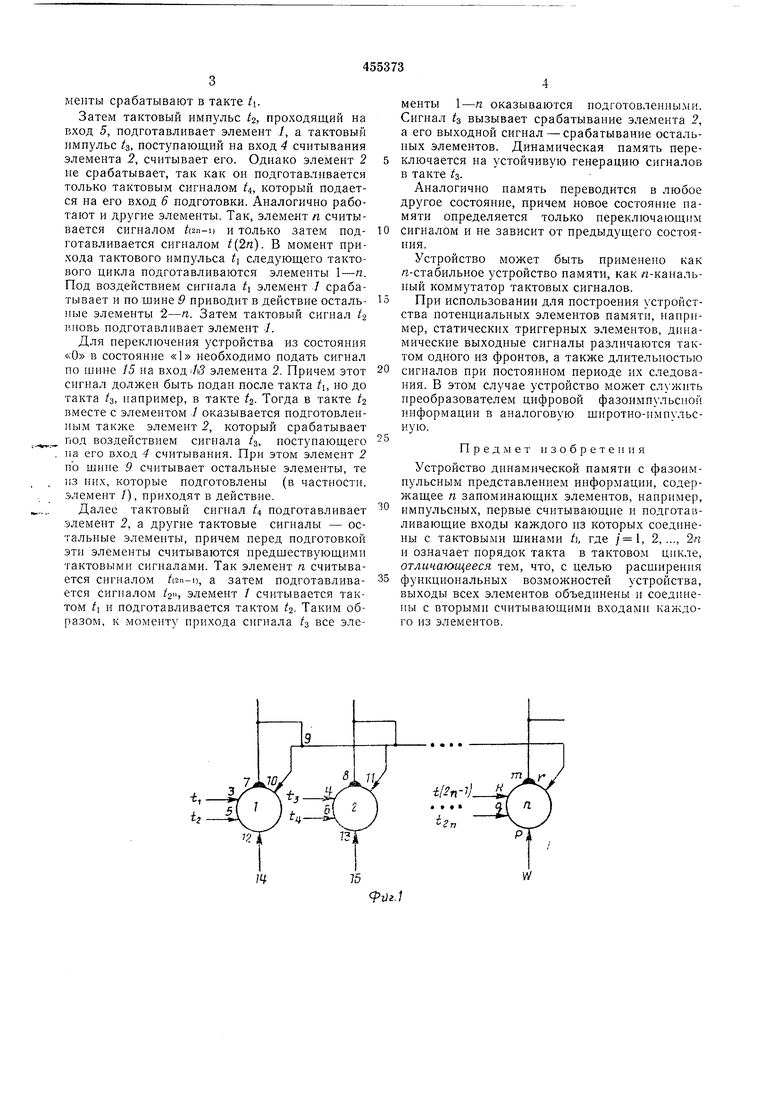

На фиг. 1 нредставлеиа фуикциональиая схема иредлагаемого устройства, построенного на феррит-траизисторных элементах; на фиг. 2 - временная диаграмма работы динамической памяти, имеющей л 2 состояния (сигиалы на входах и выходах элементов обозначены затушоваииой линией, а иахождеиие

элемента в состоянии «1, подготовки, - защтрихованной зоной).

Устройство на п состояний работает под воздействием тактовых сигналов h, где ,2, 3, ..., 2п и означает порядок сигналов t в тактовом цикле.

Дииамическая память построена на ферриттранзисторных элементах 1, 2, ..., п - по одному элементу на каждое состояние.

Первые входы 3, 4, ..., k считывания элементов 1-п соединены с шинами тактовых сигналов ti; /3 ,.-., (2rt-I), а первые входы 5, 6, ..., q записи этих элементов - с шииами тактовых сигналов /о, и, , i24,

Выходы 7, 8, ..., т элемеитов 1-п объединены в щину 9, которая соединена с вторыми входами счнтываиия 10, 11, ..., г элементов 1-п, а их вторые входы .12, 13, ..., р записи - с шинами 14, 15, ..., ш переключающих сигналов.

Каждое состояние динамической памяти отличается фазой имнульсов выходны.ч сигналов.

Работает предлагаемое устройство следующнм образом.

Когда устройство находится в состоянии «О, то к моменту нрихода тактового сигнала /, все элементы нодготовлеиы и нод воздействием снгнала i, элемент / срабатывает. Сигнал с его выхода 7 поступает по шине 9 на считывающие входы других элемеитов и вызы0вает их срабатывание. Таким образом, все элементы срабатывают в такте ti.

Затем тактовый импульс /2, проходящий на вход 5, подготавливает элемент ,/, а тактовый импульс /3, поступающий на вход 4 считывания элемента 2, считывает его. Однако элемент 2 не срабатывает, так как он подготавливается только тактовым сигналом f, который подается на его вход 6 подготовки. Аналогично работают и другие элементы. Так, элемент п считывается сигналом (211-1) и только затем подготавливается сигналом t{2n}. В момент прихода тактового импульса ti следующего тактового цикла подготавливаются элементы 1-я. Под воздействием сигнала ti элемент 1 срабатывает и по шине & приводит в действие остальные элементы 2-п. Затем тактовый сигнал /г вновь нодготавливает элемент J.

Для нереключения устройства из состояния «О в состояние «1 необходимо подать сигнал по шние /5 на вход|/ 5 элемента 2. Причем этот сигнал должен быть подан после такта ь но до такта /3, например, в такте tz. Тогда в такте (2 вместе с элементом / оказывается подготовленным также элемент 2, который срабатывает под воздействием сигнала 4, ноступающего на его вход 4 считывания. При этом элемент 2 по шине 9 считывает остальные элементы, те из них, которые подготовлены (в частностн, элемент /), приходят в действие.

Далее тактовый сигнал (4 подготавливает элемент 2, а другие тактовые сигналы - остальные элементы, причем перед подготовкой эти элементы считываются предшествующими тактовыми сигналами. Так элемент п считывается сигналом 211-1), а затем подготавливается сигналом элемент / считывается тактом /1 и подготавливается тактом t. Таким образом, к моменту прихода сигнала /з все элементы 1-п оказываются нодготовленны.и. Сигнал 3 вызывает срабатывание элемента 2, а его выходной сигнал -срабатывание остальиых элементов. Динамическая память переключается на устойчивую генерацию сигналов в такте 4.

Аналогично память переводится в любое другое состояние, причем новое состояние памяти определяется только переключающим сигналом и не зависит от предыдущего состояния.

Устройство может быть применено как «-стабильное устройство памяти, как «-канальный коммутатор тактовых сигналов.

При использовании для построения устройстства иотенциальных элементов памяти, нанример, статических триггерных элементов, динамические выходные сигналы различаются тактом одного из фронтов, а также длительностью сигналов при постоянном периоде их следования. В этом случае устройство может служить нреобразователем цифровой фазоимпульснон информации в аналоговую широтно-нмпульсНУЮ.

Предмет изобретения

Устройство динамической памяти с фазоимпульсным представлением ииформации, содержащее п запоминающих элементов, например, импульсных, первые считывающие и подготавливающие входы каждого из которых соединены с тактовыми щинами и, где j-l, 2,..., 2п и означает порядок такта в тактовом цикле, отличающееся тем, что, с целью расщирения функциональных возмон ностей устройства, выходы всех элементов объединены и соединены с вторыми считывающими входами каждого из элементов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство динамической памяти | 1972 |

|

SU611299A1 |

| РЕВЕРСИВНЫЙ РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ | 1971 |

|

SU308517A1 |

| Устройство для выделения одиночного сигнала | 1976 |

|

SU648487A2 |

| Реверсивный распределитель импульсов | 1976 |

|

SU656209A1 |

| К-значный фазоимпульсный сумматор | 1971 |

|

SU450163A1 |

| Устройство для адресования грузов установок непрерывного транспорта | 1978 |

|

SU716934A1 |

| Устройство для контроля параметров электрических сигналов | 1983 |

|

SU1250971A1 |

| Логический анализатор | 1989 |

|

SU1730627A1 |

| Динамическая ячейка памяти | 1974 |

|

SU720512A1 |

| Многоканальный коммутатор | 1986 |

|

SU1381565A1 |

if2-n-). I

W

Авторы

Даты

1974-12-30—Публикация

1970-03-05—Подача