1

Изоб;ретен1Ие относится к области импульсной TexiHHiKH.

Известен Делитель с переменным коэффиЦиенто;м делания, содержащей двухтактный двоичный Счетчик, включающий информационный и буферный регистры и схему лереноса на входе информационного репистра, блок синхронизации и Вентили ввода, первые входы которых соединены с выходом блока синхронизации, а -вторые-с входами управления коэффициентом деления.

Цель изобретения - упрощение устройства.

Для этого в предлагаемом делителе выходы ве(нт1илей ввода соединены дополнительные ин1верторы с дополнительными входами размещения записи яуля триггеров информационного регистра.

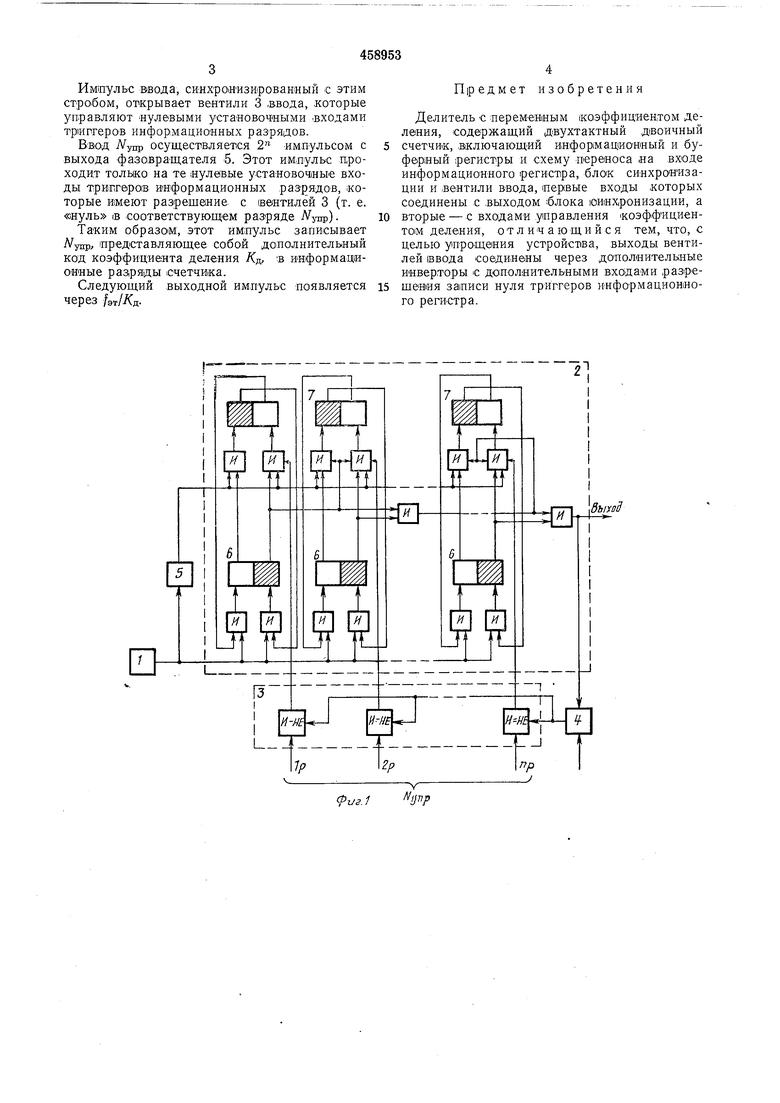

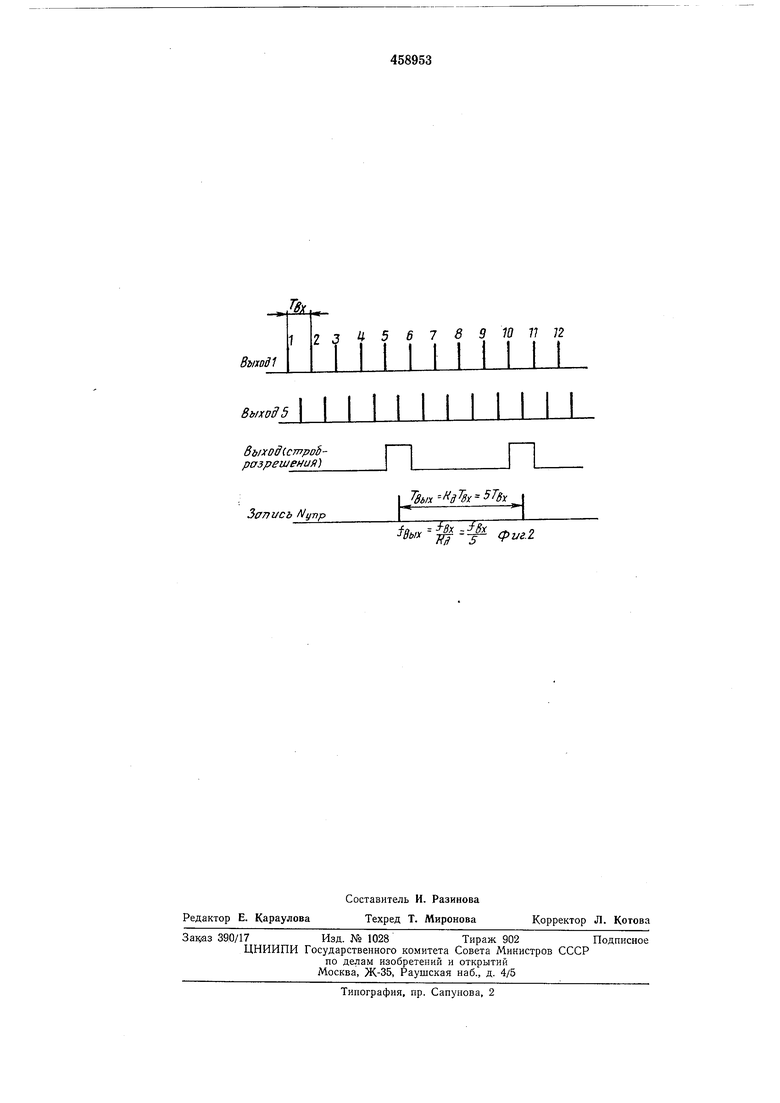

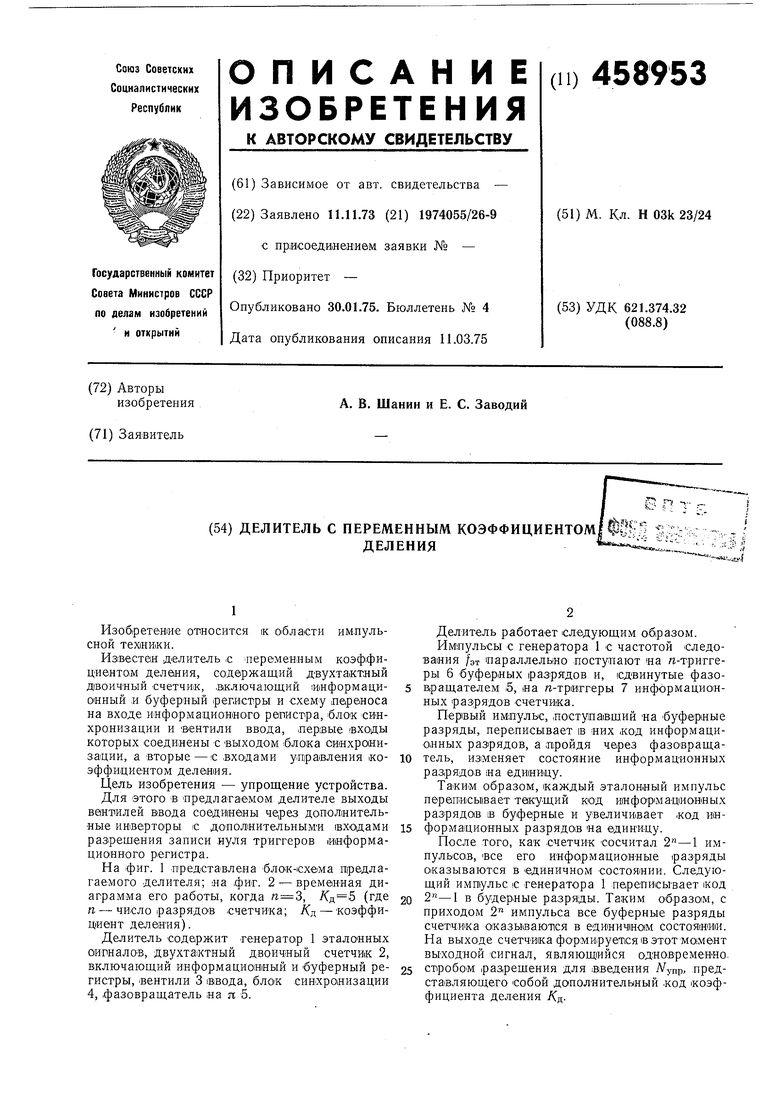

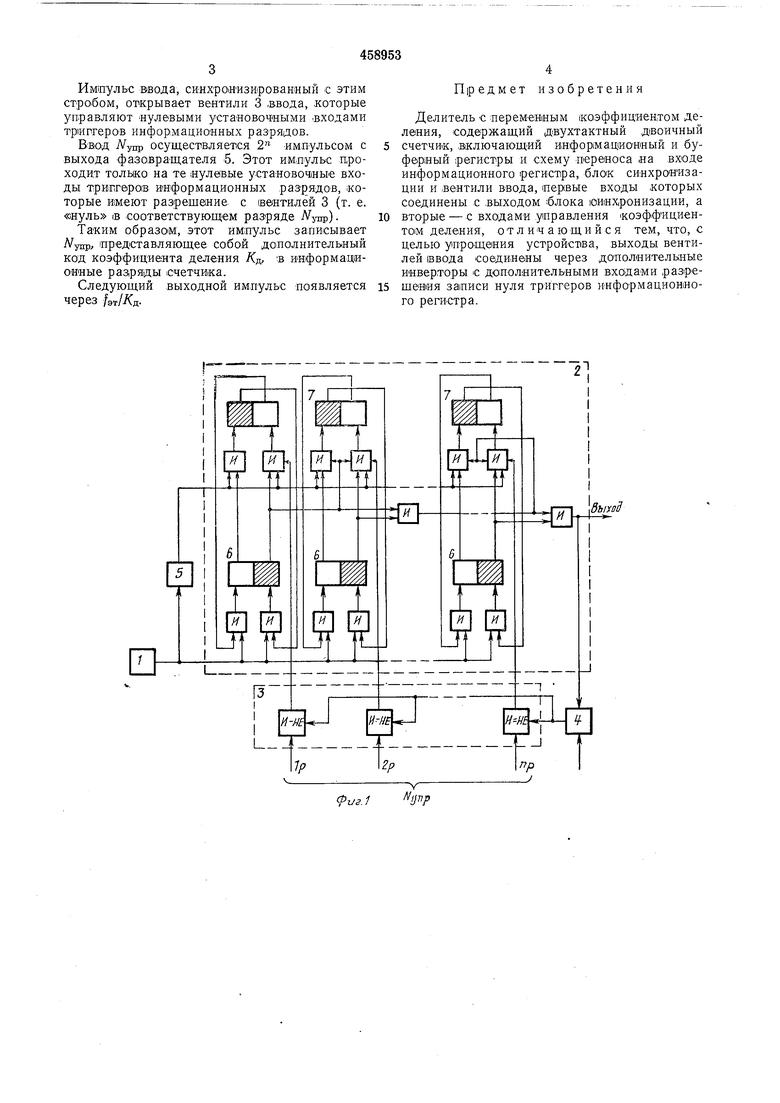

На фиг. 1 представлена блок-схема предлагаемого делителя; на фиг. 2 - временная диаграмма его работы, когда , (где п - число разрядов счетчика; /(д - коэффициент делания).

Делитель содержит генератор 1 эталонных оигналов, двухтактный двоичный счетчик 2, включающий информационный и буферный регистры, вентили 3 ввода, блок синхронизации 4, фазовращатель на л 6.

Делитель работает следующим образом.

Импульсы с генератора 1 с частотой следования /эт параллельно поступают на п-триггеры 6 буферных разрядов и, сдвинутые фазовращателем 5, иа г-тр1иггеры 7 информационных разрядов счетчика.

Первый импульс, лоступавщий на буферные разряды, переписывает IB них ,код информационных разрядов, а лройдя через фазовращатель, изменяет состояние информационных разрядов на единицу.

Таким образом, каждый эталонный импульс переписывает текущий код информационных разрядов в буферные и увеличивает ,код информационных разрядов на единицу.

После того, как счетчик сосчитал импульсов, все его информационные разряды оказываются в единичном состоянии. Следующий имвульс с генератора 1 переписывает код в будерные разряды. Таким образом, с приходом 2 импульса все буферные разряды счетчика оказываются в единич1но1М состоянии. На выходе счетчика формируется в этот момент выходной сигнал, являющийся одновременно, стробом разрещения для введения . представляю щего собой дополнительный код коэффициента деления /Сд.

Имиульс ввода, скнхроиизйрованиый .с этим CTpoi6oM, открывает вентили 3 .ввода, которые управляют Нулевыми устаиовочными входами триггерОВ инфор:мацио1нных разрядов.

Ввод Л/упр осуществляется 2 импульсом с выхода фазовращателя б. Этот имлульс проходит толыко на те «улевые установочные входы триггеров информационных разрядов, которые имеют разрешение с вентилей 3 (т. е. «нуль в соответствующем разряде N-.

Таким образом, этот импульс записывает Лупр, представляющее собой дополнительный код коэффициента деления Кц, в информационные раз,ряды счетчика.

Следующий выходной имлульс появляется через /эт/Хд.

Предмет изобретения

Делитель с переменным коэффициентом деления, содержащий двухтактный двоичный счетчик, .включающий инфор мационный и буферный регистры и схему переноса на входе информационного регистра, блок синхронизации и вентили ввода, первые входы которых соединены с выходом блока 1оинх,ронизации, а вторые - с входами управления коэффициенTOiM деления, отличающийся тем, что, с целью упрощения устройства, выходы вентилей ввода соединены через дополнительные инверторы 1C дополнительными входами разрешения записи нуля триггеров информационного регИСтра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель с переменным коэффициентом деления | 1975 |

|

SU527826A1 |

| Делитель частоты с переменным коэффициентом деления | 1976 |

|

SU657619A1 |

| Делитель с переменным коэффициентом деления | 1975 |

|

SU520689A1 |

| Перестраиваемый делитель частоты следования импульсов | 1978 |

|

SU777824A1 |

| Преобразователь угла поворота вала в код | 1976 |

|

SU635504A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| УСТРОЙСТВО ФУНКЦИОНАЛЬНОЙ ВРЕМЕННОЙ ЗАДЕРЖКИ ЭЛЕКТРИЧЕСКИХ СИГНАЛОВ | 1971 |

|

SU310268A1 |

| Многофазный цифровой фазовращатель | 1978 |

|

SU790210A1 |

| Преобразователь угла поворота вала в код | 1991 |

|

SU1833966A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЯ | 1992 |

|

RU2045781C1 |

3 l 5 6 7 8 9 10 11 12

I I I I 1

Вшод1

Запись Nunp

I 86a-- d 8x 5Ts

Авторы

Даты

1975-01-30—Публикация

1973-11-11—Подача