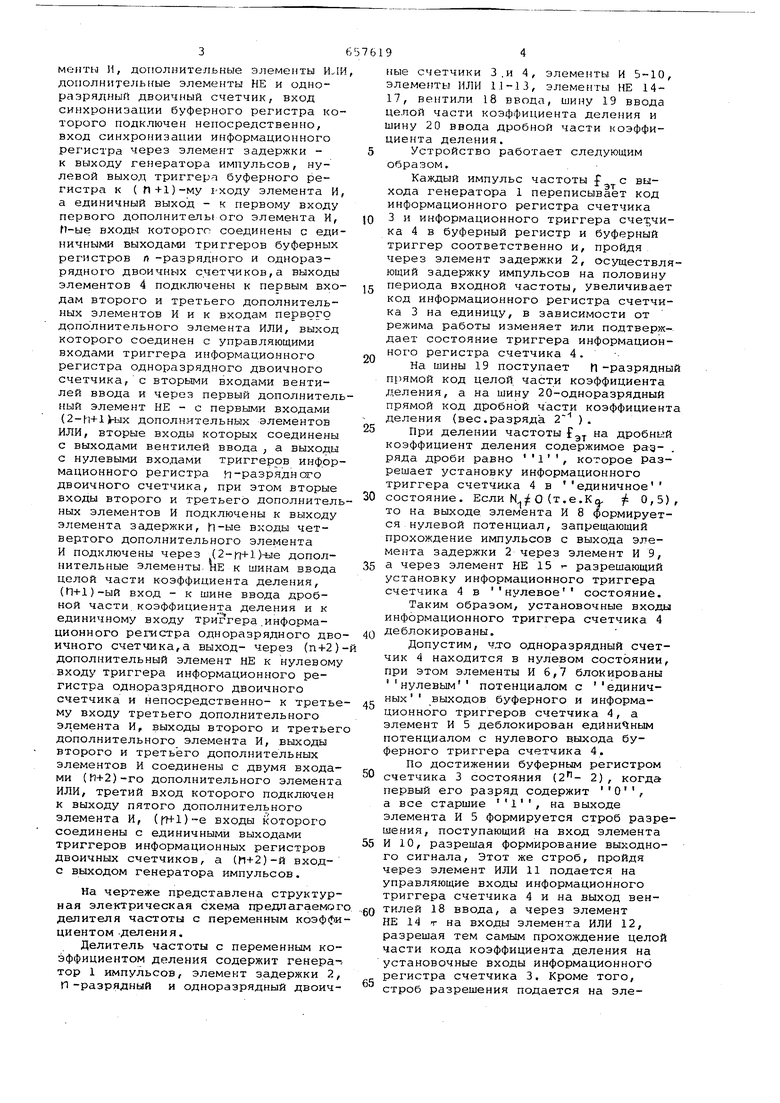

Изобретение относится к цифровым перестраиваемым делителям частоты следования импульсов и может быть использовано в цифровых синтезатора частоты и устройствах синхронизации.. Известен делитель частоты, построенйый на основе двухтактных двоичных счетчиков, в котором изменение коэффициента деления осуществля ется путем ввода поправки, т.е; начального состояния, соответствующег заданному коэффициенту деления. Это изпестное устройство содержи двухтактный двоичный счетчик с информационным и буферным регистрами схемой переноса на входе информационного регистра, блок синхронизации и вентили ввода коэффициента деления 1 . Наиболее близким техническим решением к данному изобретению явля ется устройство, содержащее П-разрядный двоичный счетчик, включающий в себя буферный регистр, подключенн к выходу генератора импульсов, и информационный регистр, подключенны к выходу элемента задержки, вход ко торого соединен с генератором импульсов, вентиля переноса на входе информационного регистра и элемент ИЛИ, соединяющий выход первого триггера буферного регистра с вентилем переноса, вентили ввода, соединенные первыми входами с разрядными целой части коэффициента деления, элемент НЕ, подк.пюченный входом к выходу первого вентиля ввода, а выходом - к единичному входу первого триггера информационного регистра, и многовходовый элемент И, П входы которого ссединены с выходами буферного регистра 2, Известные делители частоты, отличаясь высоким быстродействием и надежностью работы, позволяют изменять коэффициент деления с минимальным шагом, равным единице, что не дает возможности реализовать дробные коэффициенты деления, кратные 0,5. С целью обеспечения возможности деления на дробный коэффициент, кратный 0,5 в делитель частоты с переменным коэффициентом деления, содержащий П- разрядный двоичный счетчик, генератор импульсов, элемент задержки, вентили ввода, подключенные к шинам ввода целой части коэффициента деления, элемент НЕ и элемент И, введены дополнительные элемеиПг Л, дополнительные элементы дополнительные элементы НЕ и одноразрядный двоичный счетчик, вход синхронизации буферного регистра которого подключен непосредственно, вход синхронизации информационного регистра через элемент задержки к выходу генератора импульсов, нулевой выход триггера буферного регистра к (П+1)-му рходу элемента И, а единичный выход - к первому входу первого дополнительЕ ого элемента И, М-ые входы которого соединены с единичными выходами триггеров буферных регистров п -разрядного и одноразрядното двоичных счетчиков, а выходы элементов 4 подключены к первым входам второго и третьего дополнительных элементов И и к входам первого дополнительного элемента ИЛИ, выход которого соединен с управляющими входами триггера информационного регистра одноразрядного двоичного счетчика, с вторыми входами вентилей ввода и через первый дополнитель ный элемент НЕ - с первыми входами (2-м+1 -ых дополнительных элементов ИЛИ, вторые входы которых соединены с выходами вентилей ввода а выходы с нулевыми входами триггеров инфор мационного регистра м-разряди сто двоичного счетчика, при этом вторые входы второго и третьего дополнитель ных элементов И подключены к выходу элемента задержки, входы четвертого дополнительного элемента И подключены через (2-п+1)-ые дополнительные элементы.НЕ к шинам ввода целой части коэффициента деления, (Пн-1)-ый вход - к шине ввода дробной части.коэффициента деления и к единичному входу триггера.информационного регистра одноразрядного дво ичного счетчика,а выход- через (п+2) дополнительный элемент НЕ к нулевому входу триггера информационного регистра одноразрядного двоичного счетчика и непосредственно- к третье му входу третьего дополнительного элемента И, выходы второго и третьег дополнительного элемента И, выходы второго и третьего дополнительных элементов И соединены с двумя входами (11+2)-го дополнительного элемента ИЛИ, третий вход которого подключен к выходу пятого дополнительного элемента И, (fr(-l)-e входы которого соединены с единичными выходами триггеров информационных регистров двоичных счетчиков, а СИ+2)-й входс выходом генератора импульсов, На чертеже представлена структур ная электрическая схема предлагаемо делителя частоты с переменным коэфф циентом -деления. Делитель частоты с переменным ко эффициентом деления содержит генера тор 1 импульсов, элемент задержки 2 Г1 -разрядный и одноразрядный двоич яые счетчики 3 .и 4, элементы И 5-10, элементы ИЛИ 11-13, элементы НЕ 1417, вентили 18 ввода, шину 19 ввода елой части коэффициента деления и ину 20 ввода дробной части коэффииента деления. Устройство работает следующим образом. Каждый импульс частоты f с выхода генератора 1 переписывает код информационного регистра счетчика 3 и информационного триггера сче- чика 4 в буферный регистр и буферный триггер соответственно и, пройдя через элемент задержки 2, осуществляющий задержку импульсов на половину периода входной частоты, увеличивает код информационного регистра счетчика 3 на единицу, в зависимости от режима работы изменяет или подтверж-. дает состояние триггера информационного регистра счетчика 4. На шины 19 поступает П -разрядный прямой код целой, части коэффициента деления, а на щину 20-одноразрядный прямой код дробной части коэффициента деления (вес.разряда ). При делении частоты на дробный коэффициент деления содержимое раз- . , которое разряда дроби равно решает установку информационного триггера счетчкка 4 в единичное состояние. Если N./ О (т.е.Кп, 0,5), то на выходе элемента И 8 формируется нулевой потенциал, запрещающий прохождение импульсов с выхода элемента задержки 2 через элемент И 9, а через элемент НЕ 15 г- разрешающий установку информационного триггера счетчика 4 в нулевое состояние. Таким образом, установочные входы информационного триггера счетчика 4 деблокированы. Допустим, Ч.ТО одноразрядный счетчик 4 находится в нулевом состоянии, при этом элементы И 6,7 блокированы нулевым потенциалом с единичных выходов буферного и информационного триггеров счетчика 4, а элемент И 5 деблокирован единичным потенциалом с нулевого выхода буферного триггера счетчика 4. По достижении буферным регистром счетчика 3 состояния ( 2), когда первый его разряд содержит О, а все старшие , на выходе элемента И 5 формируется строб разрешения, поступающий на вход элемента И 10, разрешая формирование выходного сигнала. Этот же строб, пройдя через элемент ИЛИ 11 подается на управляющие входы информационного триггера счетчика 4 и на выход вентилей 18 ввода, а через элемент НЕ 14 т на входы элемента ИЛИ 12, разрешая тем самым прохождение целой части кода коэффициента деления на установочные входы информационного регистра счетчика 3. Кроме того, строб разрешения подается на элемент ИЛИ двоичного счетчика 3, дебло кируя через вентиль переноса управля ющие входы триггеров информационного регистра счетчика 3. Импульс с выхода элемента задерж ки 2 через элементы И 10 и ИЛИ 13 проходит на выход устройства, а также производит ввод N в информационный регистр счетчика 3, при этом в момент ввода осуществляется преобразование прямого кода целой части коэффициента деления в обратный код доправки, т.е. в первый разряд информационного регистра счетчика 3 при помощи элемента НЕ 16 записывается , если значение первого разряда целой части коэффициента деления равно О, и остается равным О, если первый разряд Нули в старших разрядах записываются при условии, что соответствующие старшие разряды цело части коэффициента деления содержат единицы и наоборот. Этот же импульс поступая на вход информационного триггера счетчика 4, переключает его в единичное состояние, тем самым деблокируется элемент И 7 единичным потенциалом с единичного выхода информационного триггера. Следующий импульс частоты fg-fс выхода генератора 1 переписывает состояние информационного регистра счет чика 3 и информационного триггера счетчика 4 в буферный регистр и буферный триггер соответственно, при этом элемент И 5 блокируемся нулевым потенциалом с нулевого выхода буфер ного триггера, а элемент И б деблокируется единичным потенциалом с единичного выхода буферного триггера счетчика 4. После того, как содержимое инфор мационного регистра счетчика 3 достигнет величины () , импульс с выхода генератора1, пройдя через элементы И 7 и ИЛИ 13 формирует сле дующий выходной импульс и переписывает код ( 1) в буферный регистр счетчика 3. Этот же импульс с выход элемента задержки 2 осуществляет ввод 14 , так как на выходе элемента И б и соответственно на выходе элемента ИЛИ 11 появляется строб разрешения и переключает информационный триггер счетчика 4 в состояние О после чего цикл работы делителя повторится. Если содержимое разряда дроби рав но О (деление на целочисленный коэффициент), то блокируется установ ка в 1 информационного триггера счетчика 4, на выходе элемента И 8 формируется нулевой потенциал, запрещающий прохождение импульсов с выхода элемента задержки 2 через элемент И 9 и через элемент НЕ 14 разрешающий переключение (подтвержде ние) информационного триггера счетчи ка 4 в нулевое состояние. Пои гГ/левом состоянии счетчика 4 блокированы элементы И 6,7 и деблокировын элемент И 5, следовательно, на выходе устройства проходят импульсы fg выхоЛа элемента задержки 2 по достижении буферным регистром счетчика 3 состояния ( 2), этот же импульс осуществляет ввод N в информационный регистр. При делении на коэффициент, равный 0,5-N 0,, на выходе элемента И 18 формируется единичный сигнал, который деблокирует элемент И 9 и при помощи элемента НЕ 15 блокирует установку информационного 4 в нулевое , триггера счетчика состояние, а; единичныи потенциал по шине 20 разрешает установку (подтверждение) информационного триггера счетчика единичное тояние. При единичном состоянии счетчика 4 блокирован элемент И 5 и деблокированы элементы И 6,7, а так как N - , т.е. код поправки равен (), то на выход устройства проходят все импульсы как с выходЬ генератора 1 через элементы И 9 и ИЛИ 13, так и с выхода элемента задержки 2 через элементы И 9 и ИЛИ 13, который также подтверждает состояние () информационного регистра путем ввода Формула изобретения Делитель частоты с переменным коэффициентом деления, содержащий п, разрядный двоичный счетчик, состоящий из информационного регистра, подключенного через элемент задержки к выходу генератора импульсов, буферного регистра, подключенного непосредственно к выходу генератора импульсов, элемента ИЛИ, первый вход которого подключен к единичному выходу первого триггера буферного регистра, а выход - к установочным входам второго триггера информационного регистра и к первому входу вентиля переноса, второй вход которого соединен с единичным выходом второго триггера буферного регистра, а выход - с установочными входами п-го триггера информационного регистра, вентили ввода, первые входы которых подключены к шинам ввода целой части коэффициента деления, элемент НЕ, вход которого соединен с выходом первого вентиля ввода, а выход - с единичным входом первот-о триггера информационного регистра,., и элемент И, И входы которого соединены с выходами буферного регистра, отличающийся тем, что, с целью повышения возможностиделения на дробный коэффициент кратный О ,.5 ,в него введены дополнительные элементы И, дополнительные эле

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1981 |

|

SU1001534A1 |

| Перестраивающий делитель частоты | 1977 |

|

SU661813A1 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

| Делитель с переменным коэффициентом деления | 1975 |

|

SU520689A1 |

| Делитель частоты следования импульсов | 1989 |

|

SU1709514A1 |

| Делитель с переменным коэффициентом деления | 1975 |

|

SU527826A1 |

| Устройство автоматической подстройки частоты | 1987 |

|

SU1539999A2 |

| Дробный делитель частоты следования импульсов | 1981 |

|

SU993480A1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1677869A2 |

| Преобразователь двоичного кода в код с произвольным весом младшего разряда | 1985 |

|

SU1325708A1 |

Авторы

Даты

1979-04-15—Публикация

1976-12-30—Подача