1

Изобретение относится к квазиэлектронной АТС и коммутаторам, а также к устройствам автоматического регулирования.

Известна логическая дифференцируюидая цепочка, содержащая два формирователя, объединенных но унравляющему входу через инвертор. Недостатком подобного устройства является большое количество элементов.

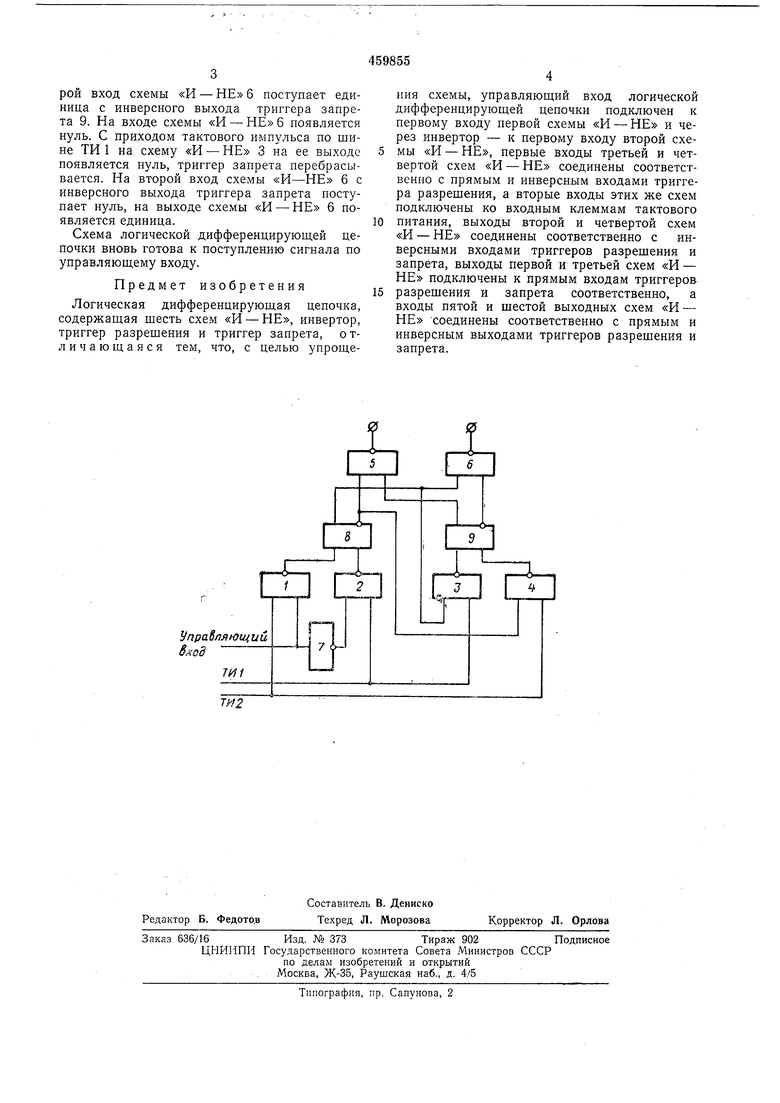

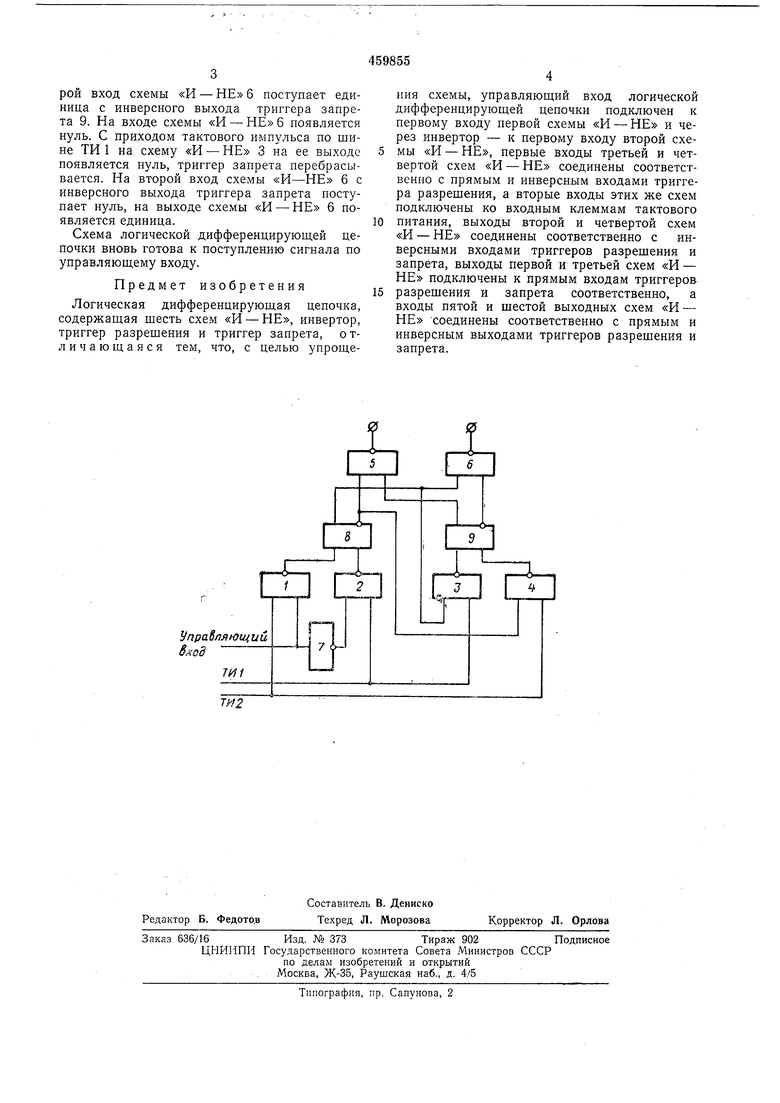

Цель изобретения - упрощение схемы - достигается тем, что управляющий вход предлагаемой логической дифференцирующей цепочки подключен к первому входу первой схемы «И - ИЕ и через инвертор - к первому входу второй схемы «И - НЕ, первые входы третьей и четвертой схем «И - НЕ соедипеиы соответствеппо с прямым и инверсным выходами триггера разрешения, а вторые входы этих же схем подключепы ко входным клемма.м тактовых импульсов, выходы второй и четвертой схем «И - НЕ соединены соответственно с инверсными входами триггеров разрешения и запрета, выходы первой и третьей схем «И - НЕ подключены к прямым входам триггеров разрешения и запрета соответственно, а входы пятой и шестой выходных схем «И - ИЕ соединены соответственно с прямым и инверсным выходами триггеров разрешения и запрета.

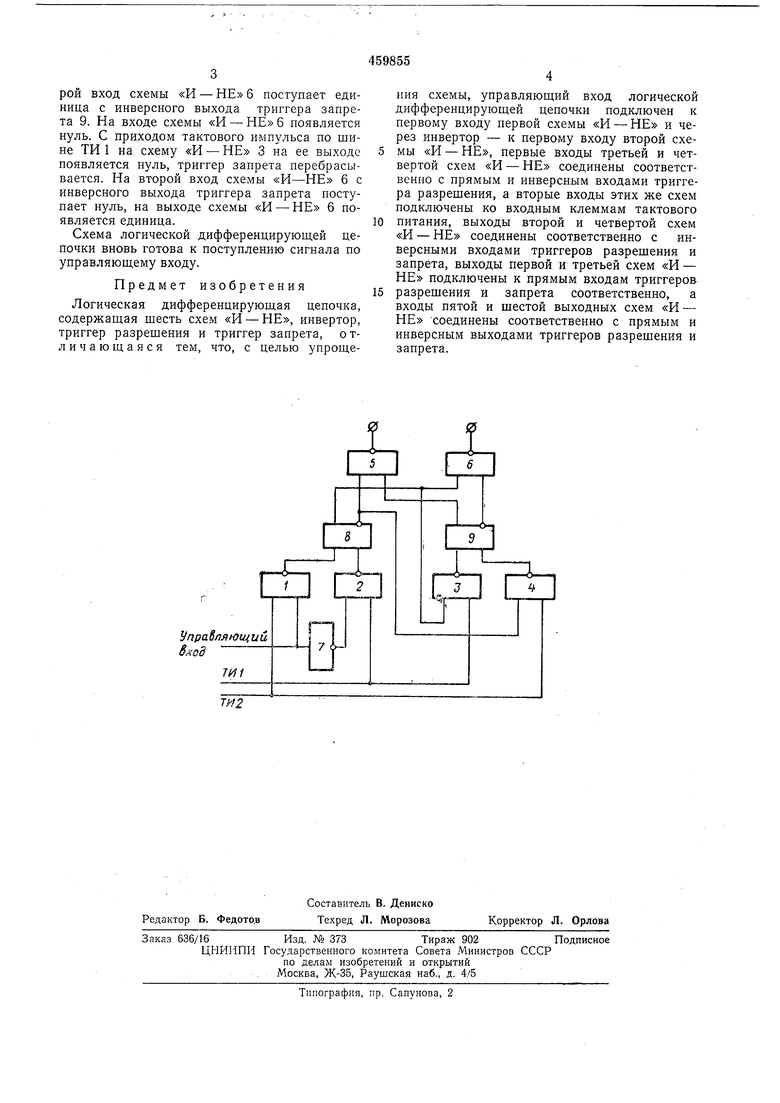

На чертеже представлена схема устройства.

Логическая дифференцирующая ценочка содержит схемы «И - ИЕ 1-6, инвертор 7, триггер разрешения 8, триггер запрета 9.

Схема работает следующим образом.

С приходом управляющего сигнала на управляющий вход логической дифференцирующей цепочки тактового импульса по шипе ТИ1 на выходе схемы «И-ИЕ 2 появляется логический нуль, который перебрасывает триггер разрешепия 8. Логическая единица с инверспого выхода триггера разрешения ноступает на первый вход схемы «И-ИЕ 5, на втором входе которой оказывается единица с прямого выхода триггера заирета 9. Иа выходе схемы «И- НЕ 5 появляется нуль. Единица с ииверсиого выхода триггера разрешения поступает на вход схемы «И - ИЕ 4. С приходом тактового импульса па шине TPI 2 триггер запрета 9 перебрасывается, и с прямого его выхода на второй вход схемы «И - ИЕ 5 поступает нуль. Иа ее выходе появляется единица. По окончании сигнала на управляющем входе и с приходом тактового импульса по щине ТИ 1 на входе схемы «И - ИЕ 1 появляется нуль. Триггер разрешения 8 устанавливается в исходное положение, и с его прямого выхода па первый вход схемы «И - ИЕ б и схемы «И - НЕ 3 поступает единица. Иа второй вход схемы «И - НЕ 6 поступает единица с инверсного выхода триггера запрета 9. На входе схемы «И - НЕ 6 появляется нуль. С приходом тактового импульса по шине ТИ 1 на схему «И - НЕ 3 на ее выходе появляется нуль, триггер запрета перебрасывается. На второй вход схемы «И-НЕ 6 с инверсного выхода триггера запрета поступает нуль, на выходе схемы «И - НЕ 6 появляется единица.

Схема логической дифференцирующей цепочки вновь готова к поступлению сигнала по управляющему входу.

Предмет изобретения

Логическая дифференцирующая цепочка, содержащая щесть схем «И - НЕ, инвертор, триггер разрешения и триггер запрета, отличающаяся тем, что, с целью упрощения схемы, управляющий вход логической дифференцирующей цепочки подключен к первому входу первой схемы «И - НЕ и через инвертор - к первому входу второй схемы «И - НЕ, первые входы третьей и четвертой схем «И - НЕ соединены соответственно с прямым и инверсным входами триггера разрешения, а вторые входы этих же схем подключены ко входным клеммам тактового

питания, выходы второй и четвертой схем «И - НЕ соединены соответственно с инверсными входами триггеров разрешения и запрета, выходы первой и третьей схем «И - НЕ подключены к прямым входам триггеров

разрешения и запрета соответственно, а входы пятой и шестой выходных схем «И - НЕ соединены соответственно с прямым и инверсным выходами триггеров разрещения и запрета.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое дифференцирующее устройство | 1973 |

|

SU577679A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ НАИБОЛЬШЕЙ РАЗНОСТИ | 1967 |

|

SU204021A1 |

| Преобразователь электрического сигнала мостового датчика в частоту | 1982 |

|

SU1026301A1 |

| Перестраиваемый селектор импульсных последовательностей | 1980 |

|

SU940287A1 |

| ФАЗОВЫЙ ДИСКРИМИНАТОР | 2013 |

|

RU2541899C1 |

| Способ прямого микропроцессорного управления тиристорным преобразователем и устройство для его осуществления | 1991 |

|

SU1838868A3 |

| ПРОТИВОУГОННАЯ СИСТЕМА | 1995 |

|

RU2086437C1 |

| Формирователь пачек импульсов | 1981 |

|

SU1005292A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ | 1996 |

|

RU2110144C1 |

| Устройство поэлементной синхронизации | 1987 |

|

SU1517142A1 |

Авторы

Даты

1975-02-05—Публикация

1972-05-05—Подача