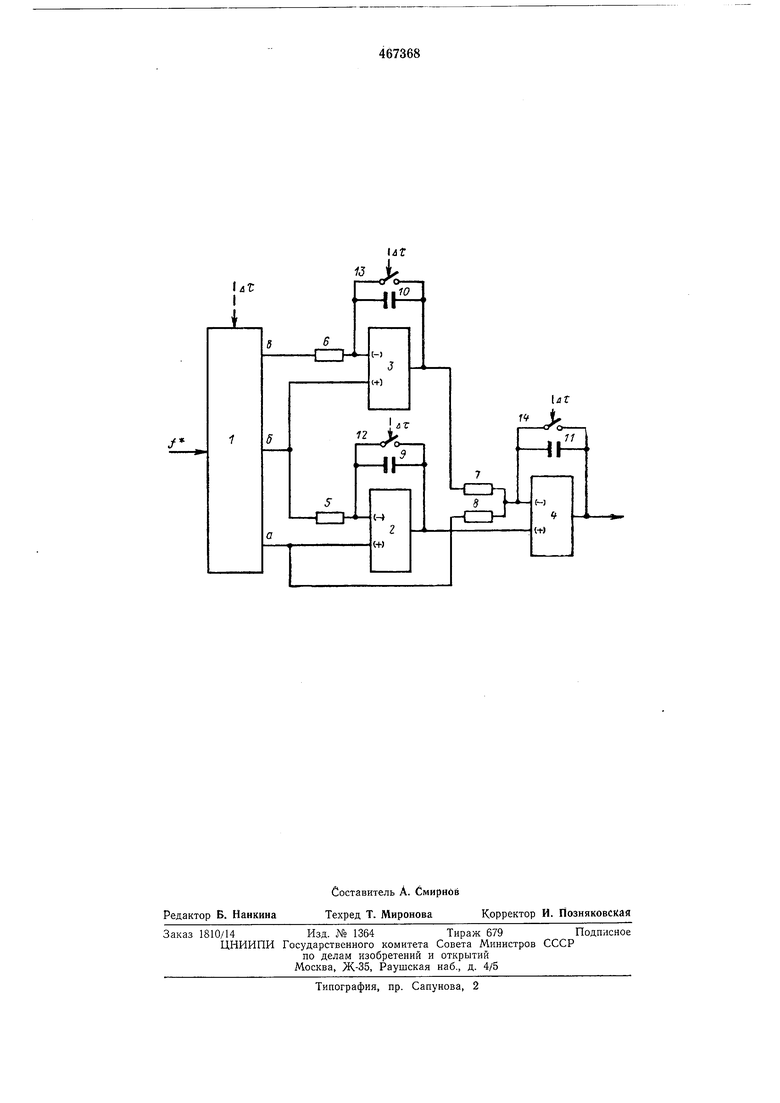

14. Выход «а регистра 1 соединен с неинвертирующим входом операционного усилителя 2, выход «б регистра 1 соединен с неинвертирующим входом операционного усилителя 3 и с резистором 5, второй конец которого подключен к инвертирующему входу операционного усилителя 2; выход «в регистра I подключен к резистору 6, второй конец которого соединен с инвертирующим входом операционного усилителя 3; выход операционного усилителя 2 соединен с неинвертирующим входом операционного усилителя 4, а выход операционного усилителя 3 соединен с резистором 7,второй конец которого подключен к инвертирующему входу операционного усилителя 4, к этому же входу подключен входной резистор 8,второй конец которого соединен с выходом «а регистра 1. За время записи Ат в аналоговый сдвигающий регистр 1 вводится очередной фиксируемый сигнал таким образом, что его величина фиксируется на выходе «а, а величины предшествующих импульсных сигналов )Т и F(n-2)Г фиксируются на выходах «б и «в соответственно. После окончания режима записи ключи 12, 13, 14 размыкаются и выходные напряжения С/2, Uz, U операционных усилителей 2, 3, 4 изменяются в соответствии с зависимостями U, U,-(U,-U,)dti с) I U,-U,--((U,-U,}dt; . и,l-(U,U,)dtt-(U.-U,}dt, т I - Rf91 TZ - «Сю, /3 - R-f-iii 4- Rfii, t - время, отсчитываемое от момента окончания записи. Так как U,.F{nT, U6 F{( и f/3 («-2)r постоянны в пределах одного периода квантования, то, принимая Т,Т,Т, 1Т 2Г, где Т - период квантования, и подставляя выражения (2), (3), в (4), после несложных преобразований получаем U, U,+ i + -l + i. (5) После сравнения (1) и (5) становится очевидным, что и4 моделирует . По окончании такта вычисления на время записи в регистр 1 очередного значения ключи 12, 13, 14 замыкаются и разряжают конденсаторы 9, 10, 11 соответственно, в результате схема принимает исходное состояние. Предмет изоб етения Аналоговый экстраполятор, содержащий интегрирующий усилитель, аналоговый регистр сдвига, первый и второй выходы которого подключены к неинвертирующему и инвертирующему входам интегрирующего усилителя, отличающийся тем, что, с целью увеличения точности, он дополнительно содержит второй и третий интегрирующие усилители, второй и третий выходы регистра сдвига соединены с неинвертирующим и инвертирующим входами второго интегрирующего усилителя, выход которого соединен с первым инвертирующим входом третьего интегрирующего усилителя, неинвертирующий вход третьего интегрирующего усилителя соединен с выходом первого интегрирующего усилителя, причем первый выход аналогового регистра сдвига соединен со вторым инвертирующим входом третьего интегрирующего усилителя.

1лТ

Ur

| название | год | авторы | номер документа |

|---|---|---|---|

| Экстраполятор | 1980 |

|

SU934504A1 |

| Экстраполятор | 1980 |

|

SU926681A1 |

| Интегратор | 1988 |

|

SU1728871A1 |

| Цифро-аналоговый преобразователь с автоматической коррекцией нелинейности | 1980 |

|

SU951692A1 |

| Устройство для определения моментов времени квантования сигналов | 1984 |

|

SU1167731A1 |

| Линейный аналоговый экстраполятор | 1974 |

|

SU503256A1 |

| Аналоговый интегратор | 1979 |

|

SU834714A1 |

| Аналого-цифровой интегратор | 1981 |

|

SU1013978A1 |

| Цифроаналоговый преобразовательС АВТОМАТичЕСКОй КОРРЕКциЕй НЕли-НЕйНОСТи | 1979 |

|

SU809549A1 |

| Аналоговый интегратор | 1980 |

|

SU886010A1 |

Авторы

Даты

1975-04-15—Публикация

1974-03-19—Подача