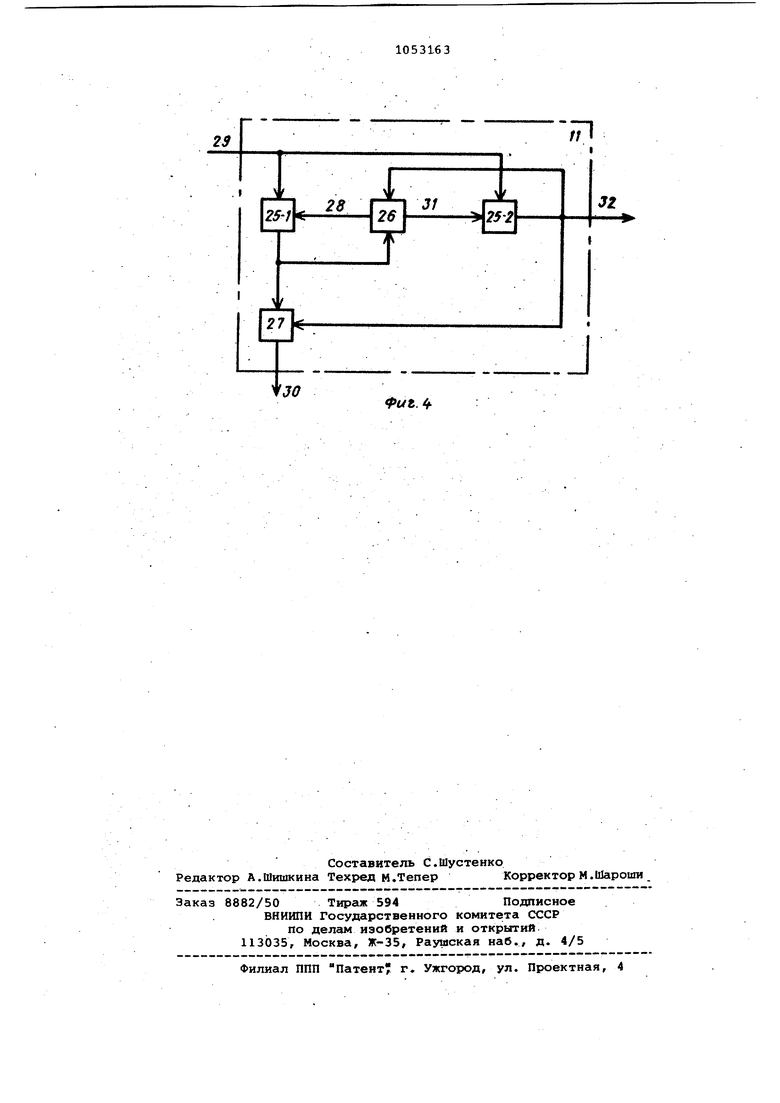

Изобретение относится к запоми нающим устройствам и может быть использовано в устройствах сопряжения вычислительных машин, в ада тивных системах измерений и вычис лительных системах для соп1Гяжения их с каналами передачи информации Известно запоминающее устройство, содержащее ячейки памяти, с единенные поразрядно последовател но, и регистр-распределитель, выходы которого соединены с входами считывания соответствующих ячеек памяти 1. Известно также запоминающее устройство, содержащее поразрядно соединенные регистры, два коммутатора, соединенные непосредствен но и через последовательно включенные регистры, элементы ИЛИ, запрета и счетчик 2. Недостатки этих устройств в то что при возникновении неисправноЬ ти в цепи передачи одного из бито информации на выход.поступают искаженные сообо1ения, т.е. в их низкой достоверности передачи дан ных. Наиболее близким по техническо сущности, к изобретению является запоминакяцее устройство, содержащее поразрядно соединенные регистры с информационньми разрядами и разрядами признака сообщени (маркерными), узлы управления перезаписью (ячейки совпадения и уп равления перезаписью) по числу ре гистров и источник тактовых сигналов з . Недостаток известного устройст заключается в невысокой надежност передачи данных, которая определя ся тем, что при возникновении неисправности в одной из цепей (канале) последовательно соединенных разрядов, на выход устройства поступает, искаженная инфО1 1ация, и такая, информация подается в течение всего сеанса передачи данных после возникновения неисправности . ; Целью изобретения является повышение надежности устройства за счет резервирования. Поставленная цель достигается тем, что в буферное запоминающее устройство/ содержащее последовательно соединенные регистры, ин-г формациойные выходы каждого из ко торых, кроме последнего., подключены к информационным входам последующего регистра, элемент ИЛИ, выход которого подключен к одному из информационных входов первого регистра, другие информационные входы первого регистра подключены к входам элемента ИЛИ, первый управляющий выход первого регистра является управляющим выходом устройства, элементы И, выходы которых подключены к управляющим входам соответствующих регистров, перв1ые входы элементов И подключены к вторьЯм управлякииим выходам соот- ветствующих регистров, а вторые входы элементов И подключены к первым управляюшим выходам последующих регистров, второй вход последнего элемента И является перBtiM управляющим входом устройства:, третьи входы элементов И объединены и являются вторым управляющим входом устройства, введены блоки контроля, коммутаторы, блок сравнения и блОк управления, один вход которого подключен к одному выходу первого блока колтроля, другие входы блока управления подключены к выходам блока сравнения, входы которого подключены к выходам второго блока контроля, вход В орого блока контроля подключен к-третьим входам элементов И, входы первой группы второго блока контроля подключены к другим выходам первого блока контроля, входы которого подключены к информационным входам первого коммутатора и являются информационными входами устройства, управляющий вход первого коммутатора является вторым управляющим вьгходом устройства и подключен к выходу блока управления и к управлякадему входу второго коммутатора, выходы которого подключены к входам второй группы второго блока контроля и являются инфо{ 1ационными выходами устройства, выходы первого коммутатора подключены к соответствующим информационным входам первого регистра, информационные входы второго коммутатора подключены к информационным выходам последнего регистра. На фиг. 1 приведена схема буферного запоминающего устройства; на фиг. 2 - примеры выполнения первого и второго коммутаторов и блока управления; на фиг. 3 пример выполнения коммутируквдего элемента; на фиг. 4 - пример выполнения селектора окончан1;я кадБуферное запоминаквдее устройство содержит коммутаторы 1, накопитель 2, блок 3 управления, блоки 4 контроля, блок 5 сравнения. Накопитель 2 содержит элемент ИЛИ б, м поразрядно соединенных регистро, каждый из которых содержит п основных и к резервных информационных разрядов 7, а такж.е разряд 8 признака сообщения, элементы И 9 о Блоки 4 содержат блоки 10 строчного контроля, селекторы 11 окончания кадра и накопитель 12. Коммутаторы 1 содержат коммутирующ элементы 13, группы элементов ИЛИ 14 и 15. Блок 3 управления содержит коммутатор 16 и К узлов. 17 управления, каждый из которых содержит П триггеров 18, группу элементов И 19, элемент ИЛИ 20, эле-. мент И 21 и триггер 22. Коммутирующий элемент 13 содержит элемент НЕ-И 23 и элемент И 24. Селектор 1 окончания кадра содержит элемент И 25, триггер 26, элемент ИЛИ 27, выход 23 триггера 26, вход 29 элемента li 25 f выход 30 элемента ИЛИ 27, выход 31 триггера 26- и выход .32 селектора 11.. Кроме того, буфер ное запоминающее устройство .содержит информационные входы 33, входы 34 и выходы 35 накопителя 2, выходы 36 , управляющие входы 37-1 и выходы 37-2., выходы 38-40 блоков 4 контроля, выходы 41 блока 5 сравнения, вход 42 и выход 43 блока 3 управления, управлянвдий вход 44. устройства, выходы 45 и 46 коммутатора 16, выходы 47 узла 17. . управления, входы 48 и 49 коммутатора 16, вькоды 50 и 51 коммутирующих элементов 13 и выходы 52 эле « ентов ИЛИ 15. Накопитель 12 выполнен аналогич но накопителю 2. Число регистров в накопителе 12 соответствует числ кадров текущей информации, которое одновременно может находится в накопителе 2. Блок 5 сравнения предназначен для поразрядного сравнени сообщений о результатах строчного контроля на входе и выходе устройства, которые синфазйо поступают на его входы 39 и 40. Он содержит П сумматоров по модулю 2, Се.пектО1р 11 оконч;анкякадра работает следующим образом. В исходном состоянии на выходе 28 триггера 26 имеется сигнал. Поэтому признак начала кадра {бит.1) поступающий на входы 29 элементов И 25, формирует на выходе элемента И 25-1 сигнал. Этот сигнал.через элемент ИЛИ 27 поступает на выход 30 селектора, а также на вход триггера 26, который перебрасывается, при этом снимается сигнал с выхода 28 и формируется на выходе 31. Поэтому признак окончания кадра (бит. 2), поступающий на вход 29, формирует сигнал на выходе элемента И 25-2, с которого поступает на второй в.ход триггера 26, который возврарщется в исходное положение, а также на выход 32 селектора 11 и через элемент ИЛИ 27 на его выход 30. Во втором блоке 4-2 контроля, в селекторе 11-2 первый выход 30 не используется, поэтому на схеме он не показан. Допустим, что строчный контроль информации на входе и выходе в результате сравнения в узле 5 (фиг,1) обнаружил ошибку по второму разряду каналу сообщений текущего кадра. Это означает, что в цепи: коммутируюр ий элемент 13-2, выход 50-2, элемент ИЛИ 14-2, его вьвсод 34-2, второй разряд 7-2 накопителя 2 (фиг. 2), выход 35-2, коммутирующий элемент 13-1, выход 50-1, элемент ИЛИ 14-2 появилась неисправность. Тогда на вход 41 поступает сигнал с битом 1 в цепи второго разряда. Этот сигнал через коммутатор 16 поступает на вход триггера 18-2, который перебрасывается и на его выходе формируется сигнал, который поступает на вход элемента И 1.9-2, а также через элемент ИЛИ 20 на вход элемента Ч 21. После окончания текущего кадра, поступающего на вход 42 блока 3 подается сигнал, который поступает на второй вход элемента И 21, на выходе которого формируется сигнал, поступающий на вхрл триггера 22. Триггер 22 перебрасывается и на его выходе.48 формируется сигнал, поступающий на вход коммутатора 16, который прн этом закрывает выход 45 (при к-1 одновременно Открывается выход 46). Кроме тогог сигнал с выхода 48 триггера 22 поступает на вторые входы элементов И 19. При этом на выходе 43-2 элемента И 19-2 формируется сигнал, поступающий в коммутаторах 1-1 и 1-2 через элементы ИЛИ 15-2, 15-п на входы элементов 13-2, 13-Г1. При этом комму- . тирующие элементы 13-2, 13-ti соединяют свои входы 33 и 35 с выходами 51-2, 51-Ц. Поэтому в сообщениях очередного кадра 1 разряд проходит с входа 33-1 через элемент 13-1, его выход ЗО- и элемент ИЛИ 14-1 коммутатора 1-1 на вход 34-1 накопителя 2 и с его вы.хода 35-1 через элемент ИЛИ 14-1 коммутатора 1-2 на выход 36-1. Остальные разряды, начиная со второго, поступают на входы 33-2, 33-П через эдементы 13-2, 13-п, их выходы 51-2, 51-я и элементы ИЛИ 14-П, 14 (ti+K) коммутатора 1-1 на входы 34-п, 34 (п+К) накопителя 2 и с его выходов 35-П, 35 (П+К) через элементы 13-2, 13-П, их выходы 51-2, 51-И и элементы ИЛИ 14-2, 14-м коммутатора 1-2 на выходы 36-2, 36-п. При этом исключается неисправный второй канал. Одновре- .1

менно сигнал с выхода 43-2 блока 3 поступает на выход устройства для регистрации неисправного канала. После окончания работы на вход 44 поступает сигнал сброса, который поступает на вторые входы триггеров 18 и 22 и возвращает их в исходное состояние, при котором снимаются сигналы с их выходов. Затем (уточняется и устраняется неисправность во втором канале передачи данных.

Буферное запоминающее устройст работает следующим образом.

Если на выходе 3J-2 накопителя 2 имеется сигнал, то на вход 33 поступают сообщения текущего кадра. В начале поступает признак начала кадра, а затем информационны сообщения и, после передачи информационных сообщений, признак окончания кадра. В качестве признаков начала и окончания .кадров может быть выбран, .например, код О О ... 1. Сообщения с входа 33, подаются на вход коммутатора 1-1 и блока 4-1, в котором поступают на.вход узла 10-1, где суммируются поразрядно, а признак кадра, кроме того, поступает и на вход 29 селектора 11-1, на выходе 30 которого формируется сигнал, поступающий на вход 42 блока 3.

С выхода 34 первого коммутатора 1-1 сообщения подаются -в. накопитель 2 и поступают на выходы первого регистра и запоминаются в разрядах 7, а также через элемент ИЛИ 6 на вход разряда 8-1 прнака сообщения, который перебрасывается. При этом снимается сигнал с выхода 52 разряда 8-1 (а значит и с выхода 37-2 устройства) и формируется на выходе 53, с которого поступает на вход узла 9-1. Если второй (следукидий) регистр свободен, то .о выхода 52 ра.ряда 8-2 на второй вход элемента 9-1 также поступает сигнал. В этом случае при поступлении тактового сигнала ТИ на третий вход элемента 9-1, на его выходе формируется сигнал перезаписи, поступаквдий на считывающие входы разрядов 7 и 8Поэтому сообщение из первого регистра переписывается во второй. При записи в разряд 8-2 признака сообщения этот разряд перебрасывается. При этом снимается сигнал с его выхода 52 и формируется на выходе 53, с которого поступает на вход элемента 9-2, который подготавливается для перезаписи сообщения из второго в третий регистры.

Одновременно, при перезаписи сообщения из первого в второй регистр в разряде 8-1 снимается сигнал с выхода 53 и формируется на i выходе 52, с которого поступает на выход 3t-2 устройства. В ответ на этот сигнал на вход 33 поступает следующее сообщение.

При записи сообщения в последний регистр в разряде 8-iW снима- , ется сигнал свыхода 52 и формируется на выходе 53, с которого по0 ступает на вход элемента 9-rti. Если при зтом сопрягаемое устройство готово к приему сообщения, то на вход 37-1 устройства поступает сигнал, который подается на вход 52

5 элемента 9-т. Поэтому очередной . тактовый сигнал ТИ формирует на выходе элемента 9-ryi сигнал перезаписи, которым сообщение из последнего регистра переписывается на

Q вход 35 второго коммутатора 1-2, с выхода котррого поступает на выход 36 устройства и на вход второго блока 4-2 контроля. При этом сообщения поступают на вход узла

5 10-2, в котором суммируются поразрядно, а признаки кадра поступают также и на вход 29 селектора 11-2. При поступлении на вход 33 устройства признака окончания кадра, признак кадра поступает на вход 29. селектора 11-1 первого блока 4-1 контроля. При этом на выходах 30 и 32 селектора 11-1 формируются . сигналы. Сигнал с выхода 32 селектора 11-1 поступает на считывающий

5 вход узла 10-1, на выход 38 которого поступает результат построчного суммирования битов сообщений данного кадра информации, который поступает на вход накопителя 12 и,

0 аналогично накопителю 2, продвигается к выходу 40.

Сигнал с выхода 32 селектора 11-1 кроме того, поступает и .на вход 38 накопителя 12. Этот сигнал н.еобхо5 ДИМ для формирования признака сообщения в том случае, когда результат построчного суммирования -в узле 10-1 в узле равен нулю. Это необходимо для обеспечения Синфазного

Q сравнения результатов контроля в блоках 4-1 и 4-2.

Признак окончания кадра с выхода 36 второго коммутатора 1-2 поступает в блок 4-2, и признак кадра подается на вход 29 селектора 11-2, на выходе 32 которого формируется сигнал. Этот сигнал поступает на входы накопителя 12 и узла 10-2, на выходы 40 и 39 которых синфазно поступают результаты строчного

0 контроля- текугчегсэ кадра на входе и выходе устройства. Эти результаты поступают на входы узла 5, в котором осуществляется их поразрядное сравнение. Результаты такого

5 сравнения поступают на выход 41

узла 5, с которого подаются на вход блока 3, в котором запоминаются.

Если биты сравниваемых разрядов равны, то на соответствующие выходы 41 поступает нулевой бит, при j неравенстве сравниваемых битов, на соответствующий выход 41 поступает единичный бит. Если к-акой-либо из основных 1, 2,. .., ti каналов вышел из строя в процессе передачи информации, то очередной сигнал, поступивший на вход 42 блока 3, формирует на его выходе 43 управляющий сигнал, поступающий на выход устройства для регистрации,а также на входы коммутаторов 1-1 и 1-2. При этом первый коммутатор 1-1

исключает неисправный основной канал путем смещения соответствующих разрядов в область резервных К каналов, .а второй коммутатор 1-2 возвращает смещенные разряды на основные 1, 2,..., П выходы.

Предложенное устройство позволяет повысить надежность (достовер:ность) передачи данных., так как возникающие неисправности при передаче данных устраняются автоматически по результатам контроля информации на входе и выходе устройства. Это особенно важно в тех случаях, когда отсутствует возможность получения повторной информации, например при телеметрических измерениях летательных аппаратов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивная телеметрическая система | 1979 |

|

SU783825A1 |

| Устройство для передачи телеметрической информации | 1978 |

|

SU765858A1 |

| ЦИФРОВОЙ ТЕЛЕВИЗОР | 2006 |

|

RU2310287C1 |

| Запоминающее устройство с коррекцией ошибок | 1980 |

|

SU942160A2 |

| ЦИФРОВОЙ ТЕЛЕВИЗОР | 2006 |

|

RU2313919C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Запоминающее устройство с коррекцией ошибок | 1978 |

|

SU744740A1 |

| Многоканальное устройство передачиТЕлЕМЕТРичЕСКиХ дАННыХ C СОКРАщЕНиЕМизбыТОчНОСТи | 1979 |

|

SU851442A1 |

| Система программного управления станками | 1985 |

|

SU1328792A1 |

| Запоминающее устройство с обнаружением ошибок | 1986 |

|

SU1348913A1 |

БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее последовательно : соединенные регистры, информационные выходы каждого из которых, кроме последнего, подключены к информационным входам последуицего регистра, элемент ИЛИ, выход которого подключен к одному из информационных входов первого регистра, другие информационные входы первого регистра подключены к вхо.дам элемента ИЛИ, первый управляющий выход первого регистра является управляющим выходом устройства, элементы И, выходы которых подключены к управляющим входгм соответствующих регистров, первые входы элементов И подключены к вторым управлякицим выходам соответствующих регистров, а вторые входы элементов и подключены к первым управляющим выходам последующих регистров, второй вход последнего эле,мента И является первым управляют щим входом устройства, третьи входы элементов И объединены и являются вторым управляющим входом устройства, о т л и ч а ю щ е е с я тем , что, с целью повышения его надежности за счет резерви- . рования , оно содержит блоки контроля , коммутаторы, блок сравнения и блок управления, бдим вход которого подключен к одному выходу первого блока контроля, другие входы блока управления подключены к выходам блока сравнения, входы которого подключены к выходам второго блока контроля, вход второго блока контроля подключен к третьим входам элементов И, входы первой группы второго блока S контроля подключены к другим выходам первого блока контроля, входы которого подключены к информационным входам первого коммутатора и являются информационными входами устройства, управляющий вход первого коммутатора является вторьм управляющим выходом устройства и подключен..к выходу блока управления и к управляющему входу второго коммутатора, выходы которого подключены к входам второй группы сл второго блока контроля и являются оо информационными выходами устройства, выходы первого коммутатора подключены к соответствующий о информационные входам первого регистра, информационные входы второсо го коммутатора подключены к информационные выходам последнего регистра.

50-1 11/5-; «

33

-иг.З 1

tJ(7

.J

Фиг.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| МИНАЮЩЕЕ УСТРОЙСТВО | 0 |

|

SU282427A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 0 |

|

SU397972A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Запоминающее устройство | 1974 |

|

SU474844A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1983-11-07—Публикация

1982-06-07—Подача