4 ОО 4ib СЛ

Z4

. .1

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах, имеющих дефектные элементы памяти.

Цель изобретения - повьппение быстродействия и расширение функциональных возможностей устройства за счет выявления дефектных элементов памя- |ти в режиме самоконтроля.

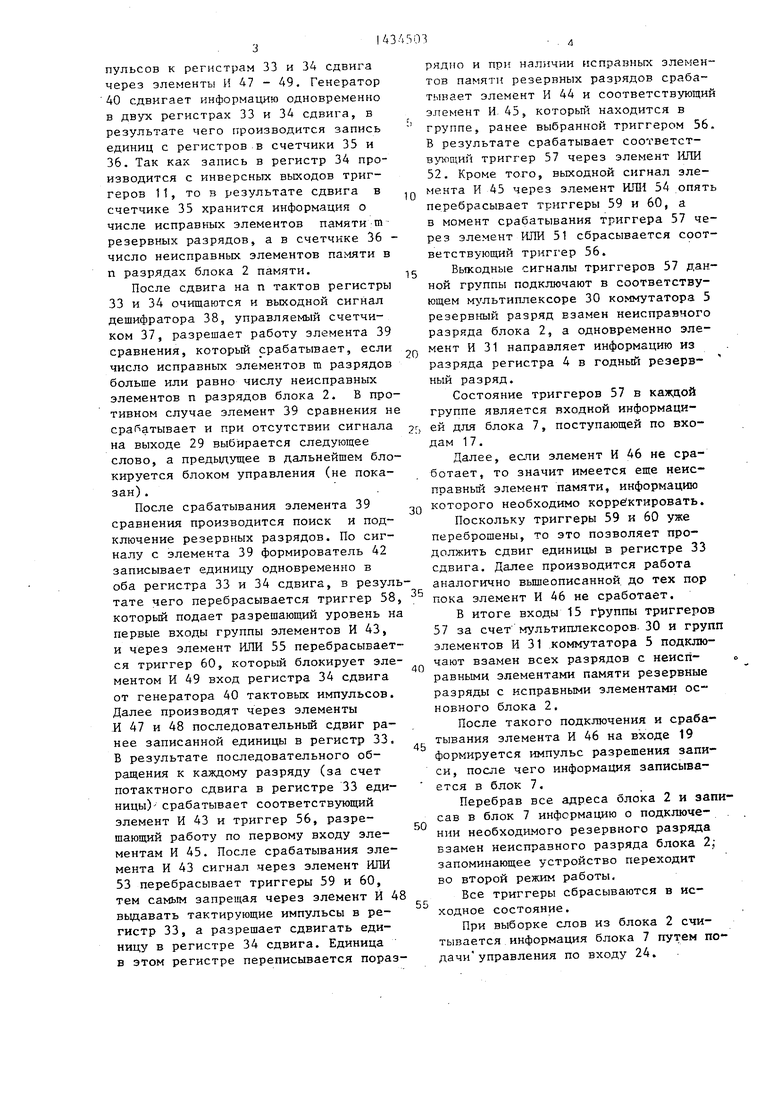

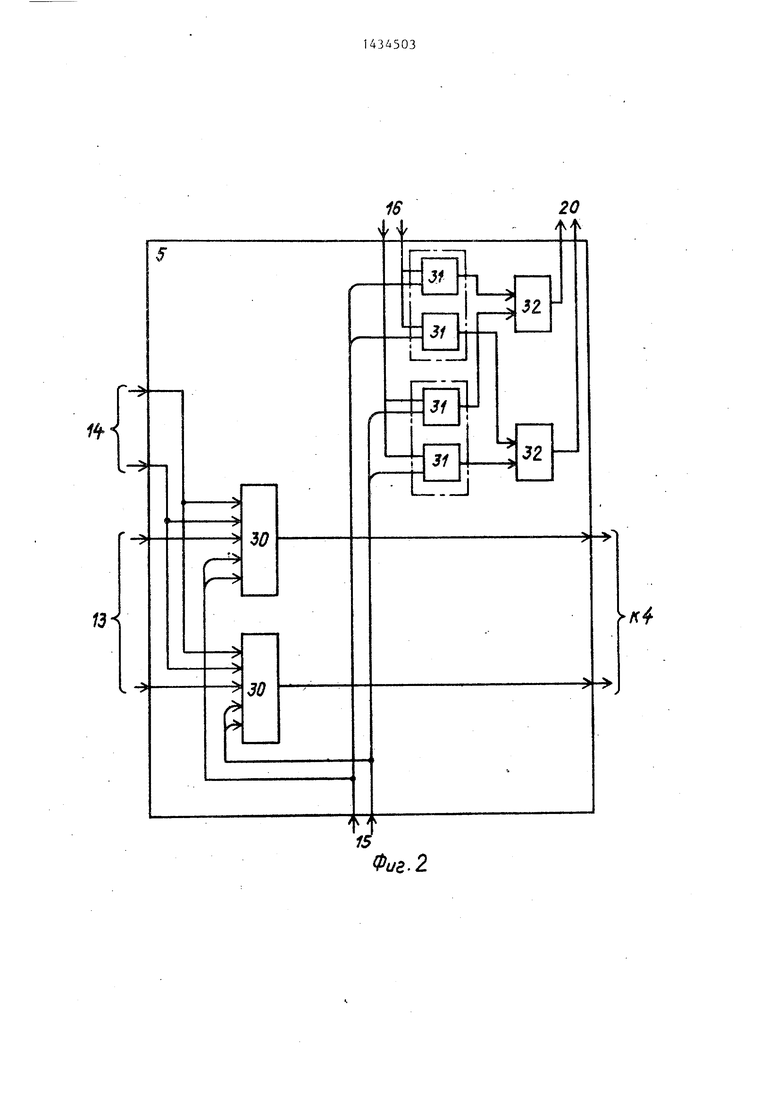

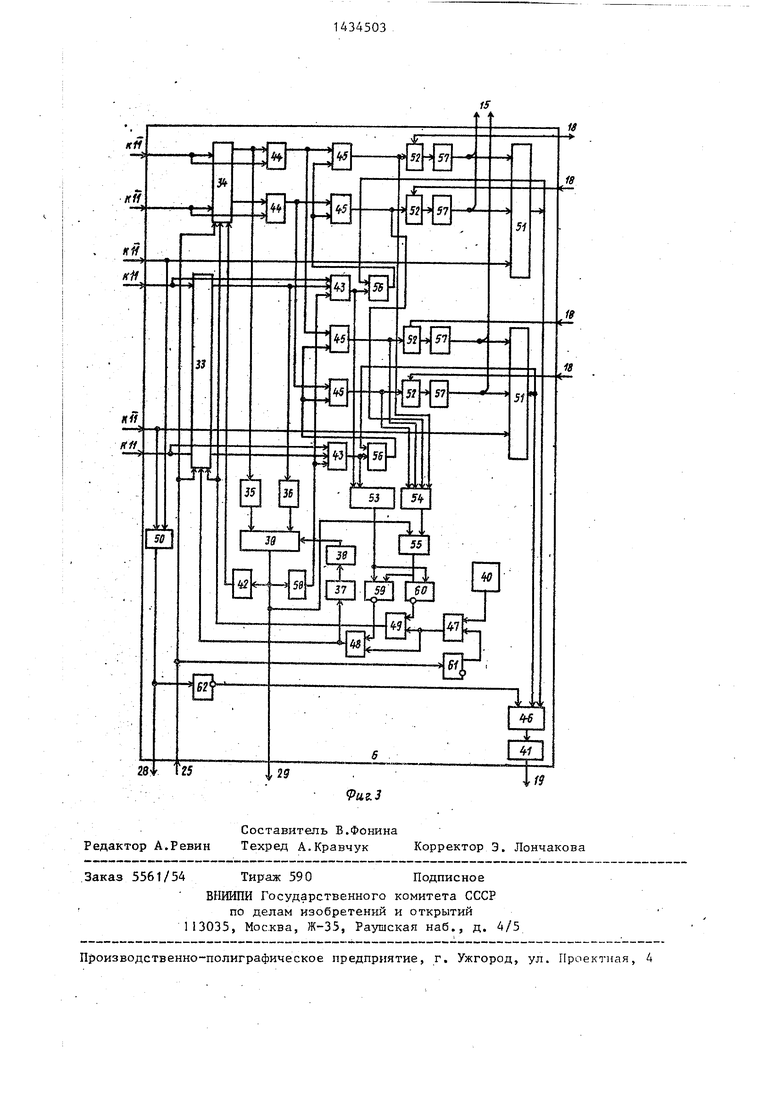

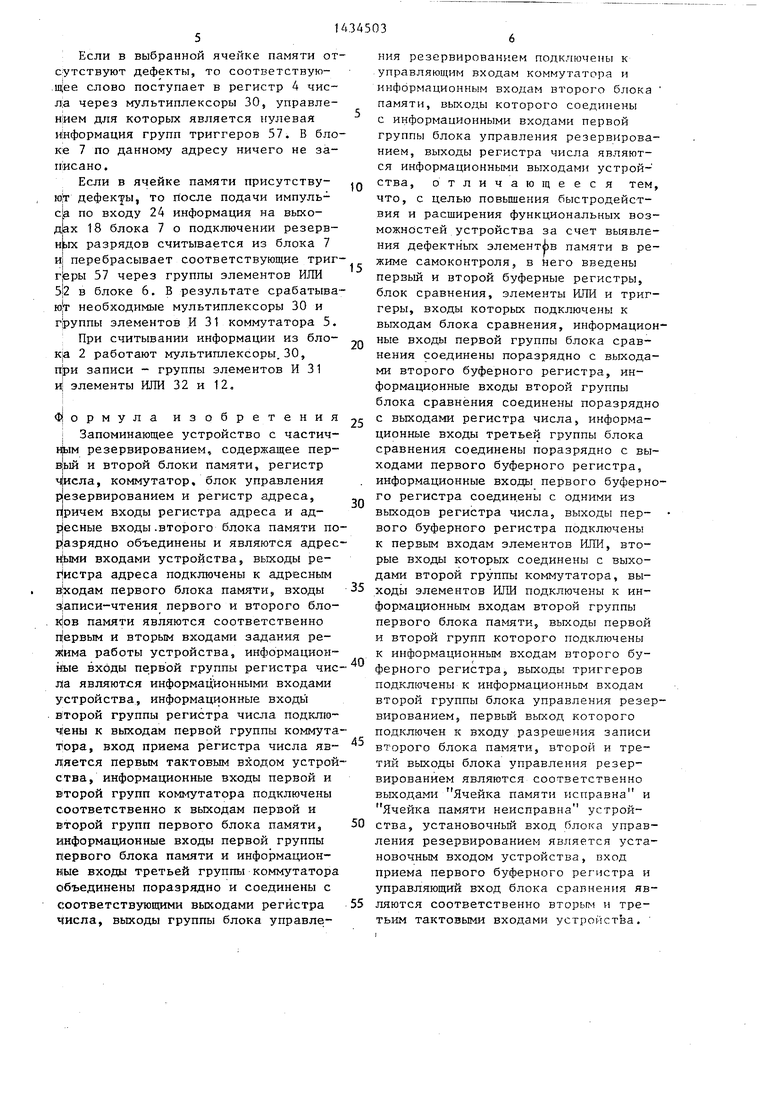

На Фиг. 1 изображена структурная схема предлагаемого устройства; на фиг. 2 - структурная схема коммутатора; на фиг. 3 - структурная схема 5лока управления резервированием. I Устройство содержит регистр 1 ад- эеса, первьй блок 2 памяти с резервами элементами 3 памяти, регистр 4

числа, коммутатор 5, блок 6 управления резервированием, второй блок 7 ламяти,, первый 8 и второй 9 буферные регистры, блок 10 сравнения, тригге- )Ы 11 и элементы ИЛИ 12.

Коммутатор 5 содержит входы 13 - 16,

Блок 7 содержит входы 17 выхо18 и входы 19.

Коммутатор 5 содержит выходы 20.

Устройство также содержит информа онные 21 и адресные 22 входы, пер- ый 23 и второй 24 входы задания режи работы устройства, установочный 4ход 25, тактовые входы 26 и 27, вы- з|од Ячейка памяти исправна 28 и вы НОД Ячейка памяти неисправна 29.

Регистр 4 - п-разрядный, регистр 8 - т-разрядный, регистр 9 - (n+m)- р азрядный, причем .

Коммутатор 5 содержит мультиплек- с1оры 30 и группы элементов И 31, причем число мультиплексоров и групп элементов-И 31 равно разрядности п блока 2 памяти, и элементы ИЛИ 32 в.количестве, равном числу m резервных разрядов.

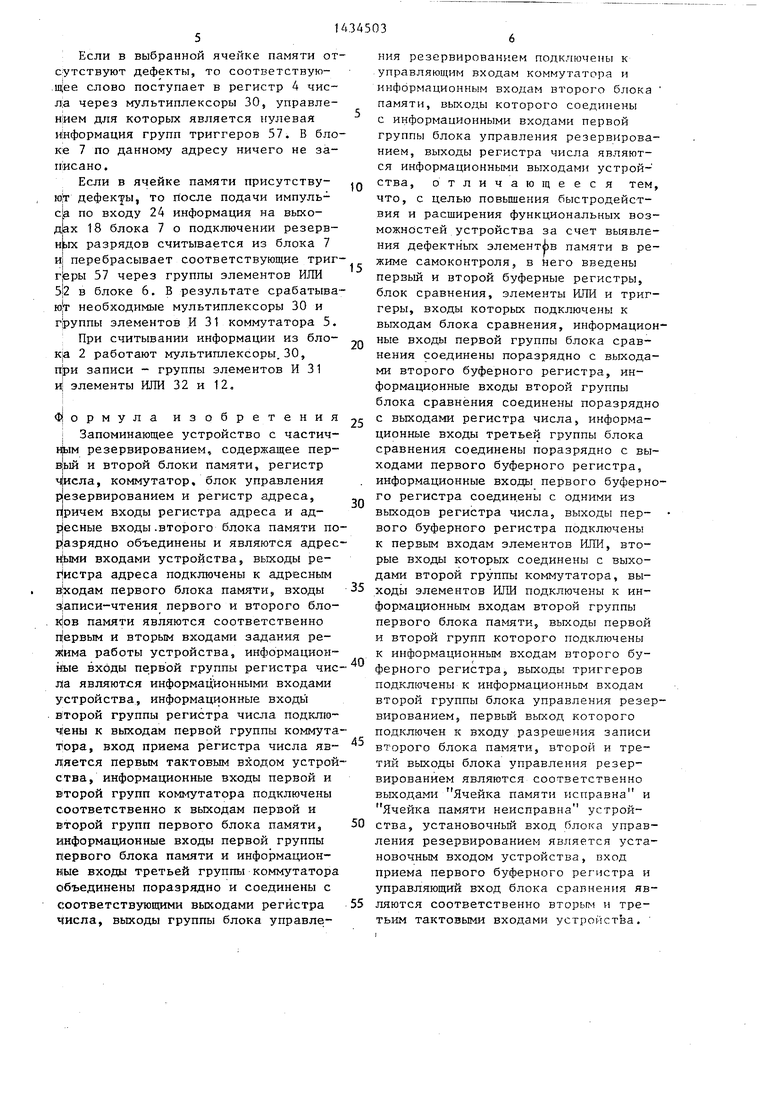

Блок 6 управления резервированием содержит два регистра 33 и 34 сдвига, три счетчика 35 - 37, дешифратор 38, элемент 39 сравнения генератор

40тактовых импульсов, формирователи

41и 42 одиночных импульсов, группы элементов И 43 - 45, элементы И 46-50, группы элементов ИЛИ 51 и 52, элементы ИЛИ 53 - 55, группы триггеров 56

и 57 и триггеры 58-62.

В качестве блока 7 памяти может быть использовано либо оперативное ЗУ, либо программируемое постоянное ЗУ.

5

о

Устройство работает в двух режимах.

Первый режим работы - режим самоконтроля - выявляет в каждой ячейке памяти неисправные элементы памяти блока 2 и находит необходимые резервные разряды, координаты которьпс затем записываются в соответствующие

Q разряды блока 7 памяти.

Второй режим работы обеспечивает эксплуатацию устройства. Перед выборкой каждого слова опрашивается блок 7, где хранится информация пер5 вого режима работы, и взамен неисправных элементов памяти оперативно подключаются резервные элементы 3 блока 2.

Перед началом работы все регистры,

0 счетчики и триггеры устройства сброшены в исходное состояние(цепи управления сбросом не показаны).

При первом режиме работы (после установления на входах 22 необходи5 мого адреса) в регистр 4 записывается число, подаваемое по входам 21. Далее подается управление на вход 27, в результате чего информация из регистра 4 переписывается в регистр 8, при этом в регистре 4 информация остается. Затем подается команда по входу 23 и производится запись числа из регистра 4 и из регистра 8 через элементы ИЛИ 12 в блок 2. Далее опять по команде на вход 23 считывается информация из блока 2 и записывается только в регистр 9. Инфор0

5

0

мация, считанная в регистре 9, и информация хранящаяся в регистрах 4 и 8, поразрядно сравниваются в блоке 10. Сигналы несравнения, показывающие неисправные элементы памяти в выбранной ячейке памяти, перебрасывают соответствующие триггеры 11,

Если все элементы памяти в п разрядах блока 2 годные, тогда нулевая информация с триггеров 11 вызывает срабатывание элемента И 50, который перебрасывает триггер 62 и выдает сигнал по выходу 28, показывающий год- годность всех п разрядов. Тогда выбирается очередное слово.

Если имеются неисправные разряды тогда по отсутствию сигнала на выходе 28 на вход 25 подается одиночный сигнал, переписывающий состояния триггеров 11 в регистры 33 и 34 и перебрасывающий триггер 61, подключая тем самым генератор 40 тактовых импульсов к регистрам 33 и 34 сдвига через элементы И 47 - 49. Генератор 40 сдвигает информацию одновременно в двух регистрах 33 и 34 сдвига, в результате чего производится запись единиц с регистров в счетчики 35 и 36. Так как запись в регистр 34 производится с инверсных выходов триггеров 11, то в результате сдвига в счетчике 35 хранится информация о числе исправных элементов памяти:т резервных разрядов, а в счетчике 36 - число неисправных элементов памяти в п разрядах блока 2 памяти.

После сдвига на п тактов регистры 33 и 34 очищаются и выходной сигнал дешифратора 38, управляемый счетчиком 37, разрешает работу элемента 39 сравнения, который срабатывает, если число исправных элементов m разрядов больше или равно числу неисправных элементов п разрядов блока 2. В противном случае элемент 39 сравнения не срабатывает и при отсутствии сигнала на выходе 29 выбирается следующее слово, а предыдущее в дальнейшем блокируется блоком управления (не показан) .

После срабатывания элемента 39 сравнения производится поиск и подключение резервных разрядов. По сигналу с элемента 39 формирователь 42 записывает единицу одновременно в оба регистра 33 и 34 сдвига, в результате чего перебрасывается триггер 58 который подает разрешающий уровень на первые входы группы элементов И 43, и через элемент ИЛИ 55 перебрасывается триггер 60, который блокирует элементом И 49 вход регистра 34 сдвига от генератора 40 тактовых импульсов. Далее производят через элементы И 47 и 48 последовательньй сдвиг ранее записанной единицы в регистр 33. В результате последовательного обращения к каждому разряду (за счет потактного сдвига в регистре 33 единицы)- срабатывает соответствующий элемент И 43 и триггер 56, разрешающий работу по первому входу элементам И 45. После срабатывания элемента И 43 сигнал через элемент ИЛИ 53 перебрасывает триггеры 59 и 60, тем самым запрещая через элемент И 48 выдавать тактирующие импульсы в регистр 33, а разрешает сдвигать единицу в регистре 34 сдвига. Единица в этом регистре переписывается пораз0

5

0

Г)

0

5

0

5

0

5

рядно и при наличии исправных элементов памяти резервных разрядов срабатывает элемент И 44 и соответствующий элемент И- 45, которьш находится в группе, ранее выбранной триггером 56. В результате срабатывает соответст- в тощий триггер 57 через элемент ИЛИ 52. Кроме того, выходной сигнал элемента И 45 через элемент KTDi 54 опять перебрасывает триггеры 59 и 60, а в момент срабатывания триггера 57 через элемент ИЛИ 51 сбрасывается соот- ветствуюпщй триггер 56.

Выходные сигналы триггеров 57 данной группы подключают в соответствующем мультиплексоре 30 коммутатора 5 резервный разряд взамен неисправного разряда блока 2, а одновременно элемент И 31 направляет информацию из разряда регистра 4 в годный резерв ный разряд.

Состояние триггеров 57 в группе является входной информацией для блока 7, поступающей по входам 17.

Далее, если элемент И 46 не сработает, то значит имеется еще неис- правньй элемент памяти, информацию которого необходимо корректировать.

Поскольку триггеры 59 и 60 уже переброшены, то это позволяет продолжить сдвиг единицы в регистре 33 сдвига. Далее производится работа аналогично вьш еописанной до тех пор пока элемент И 46 не сработает.

В итоге входы 15 триггеров 57 за счет мультиплексоров. 30 и групп элементов И 31 коммутатора 5 подключают взамен всех разрядов с неисп- равными элементами памяти резервные разряды с исправными элементами основного блока 2.

После такого подключения и срабатывания элемента И 46 на входе 19 формируется импульс разрешения записи, после чего информация записывается в блок 7.

Перебрав все адреса блока 2 и записав в блок 7 информацию о подключении необходимого резервного разряда взамен неисправного разряда блока 2; запоминающее устройство переходит во второй режим работы.

Все триггеры сбрасываются в исходное состояние.

При выборке слов из блока 2 считывается информация блока 7 путем подачи управления по входу 24.

Если в выбранной ячейке памяти отсутствуют дефекты, то соответствующее слово поступает в регистр 4 числа через мультиплексоры 30, управлением для которых является нулевая Информация групп триггеров 57. В блоке 7 по данному адресу ничего не записано .

Если в ячейке памяти присутству- ю дефекты, то после подачи импуль- с по входу 24 информация на выхо- дЬх 18 блока 7 о подключении резерв- разрядов считывается из блока 7 и| перебрасывает соответствующие триг- гЬры 57 через группы элементов ИЛИ в блоке 6. В результате срабатыва- ю т необходимые мультиплексоры 30 и г|руппы элементов И 31 коммутатора 5.

При считывании информации из бло- к 2 работают мультиплексоры. 30, записи - группы элементов И 31 и| элементы ИЛИ 32 и 12,

Йормула изобретения Запоминающее устройство с частич- ribiM резервированием, содержащее пер- ый и второй блоки памяти, регистр ч|исла, коммутатор, блок управления р|езервированием и регистр адреса, п|ричем входы регистра адреса и ад- FJecHHe входы .второго блока памяти по- р азрядно объединены и являются адрес- ф1ми входами устройства, выходы ре- rJHCTpa адреса подключены к адресным выходам первого блока памяти, входы з аписи-чтения первого и второго бло- к1ов памяти являются соответственно первым и вторым входами задания ре- Жима работы устройства, информационные входы первой группы регистра чис па являются информационными входами устройства, информационные входы в торой группы регистра числа подклю- четл к выходам первой группы коммута Tiopa, вход приема регистра числа является первым тактовым входом устрой ства, информационные входы первой и второй групп коммутатора подключены соответственно к выходам первой и Б1ТОРОЙ групп первого блока памяти, информационные входы первой группы первого блока памяти и информационные входы третьей группы коммутатора объединены поразрядно и соединены с соответствующими выходами регистра числа, выходы группы блока управления резервированием подключены к управляющим входам коммутатора и информационным входам второго блока памяти, выходы которого соединены с информационными входами первой группы блока управления резервированием, выходы регистра числа являются информационными выходами устрой д ства, отличающееся тем, что, с целью повьщ1ения быстродействия и расширения функциональных возможностей устройства за счет выявления дефектных элементов памяти в жиме самоконтроля, в него введены первый и второй буферные регистры, блок сравнения, элементы ИЛИ и триггеры, входы которых подключены к выходам блока сравнения, информацион2Q ные входы первой группы блока сравнения соединены поразрядно с выходами второго буферного регистра, информационные входы второй группы блока сравнения соединены поразрядно

25 с выходами регистра числа, информационные входы третьей группы блока сравнения соединены поразрядно с выходами первого буферного регистра, . информационные входы первого буферно, го регистра соединены с одними из выходов регистра числа, выходы первого буферного регистра подключены к первым входам элементов ИЛИ, вторые входы которых соединены с выходами второй группы коммутатора, вы35 ходы элементов ИЛИ подключены к ин- формационньм входам второй группы первого блока памяти, выходы первой и второй групп которого подключены к информационным входам второго буферного регистра, выходы триггеров подключень к информационным входам второй группы блока управления резервированием, первый выход которого подключен к входу разрешения записи второго блока памяти, второй и третий выходы блока управления резервированием являются соответственно выходами Ячейка памяти исправна и Ячейка памяти неисправна устрой50 ства, установочньш вход блока управления резервированием является установочным входом устройства, вход приема первого буферного регистра и управляющий вход блока сравнения яв55 ляются соответственно вторым н третьим тактозыми входами устройства.

. 40

45

1

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1982 |

|

SU1084903A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1309024A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| МОДУЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2474868C1 |

| Резервированная вычислительная система | 1990 |

|

SU1755400A1 |

| РАСПРЕДЕЛИТЕЛЬНАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1997 |

|

RU2122229C1 |

| Резервированное запоминающее устройство | 1987 |

|

SU1501172A1 |

| РАСПРЕДЕЛЕННАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 2000 |

|

RU2185656C2 |

| Микропроцессорная система | 1989 |

|

SU1686454A1 |

| Резервное запоминающее устройство | 1976 |

|

SU604036A1 |

Изобретение относится к вычислительной технике и может быть ис- пользовано в запоминающих устройствах, имеющих дефектные элементы памяти. Цель изобретения - повышение быстродействия и расширение функцио- нальньрс возможностей устройства за счет выявления дефектных элементов памяти в режиме самоконтроля. Устрой- ство содержит регистр 1 адреса, первый 2 и второй 7 блоки памяти, ре- : гистр 4 числа, коммутатор 5, блок 6 управления резервированием, первый 8 и второй 9 буферные регистры, блок 10 сравнения, триггеры 11 и элементы ИЖ 12. Устройство работает в двух режимах. Первый режим - режим самоконтроля - позволяет выявить неисправные элементы памяти в блоке 2, заменить их резервными элементами 3 памяти блока 2 и запомнить информацию о такой замене в блоке 7 памяти Второй режим обеспечивает эксплуатацию устройства при записи и считывании информации. 3 ил. . € сл

W

L f

30

Фиг-2

Kii

| Заявка Японии №,59-31159, кл | |||

| Бесколесный шариковый ход для железнодорожных вагонов | 1917 |

|

SU97A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

| Запоминающее устройство | 1982 |

|

SU1084903A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-10-30—Публикация

1986-11-10—Подача