1

Изобретение относится к запоминающим устройствам.

Известны запоминающие устройства, содержащие накопитель, разрядньш и адресные блоки, элементы И и ИЛИ l. Такие устройства имеют ограниченные функциональные возможности,

Из известных запоминающих устройств наиболее близким по техническому решению к предлагаемому является устройство, содержащее числовые линейки, подключенные соответственно через разрядный и адресный блоки управления к регистру слова и регистру признаков обращения и через усилители чтения - к входам выходного элемента ИЛИ и блока регенерации, выходы которого соединены с входами разрядного блока управления, подключенными к выходам регистра признаков обращения, и шины признаков обращения 2. Это устройство способно определять для последовательности двоичных слов, каждый из которых имеет свой приоритет, содержится ли в последующем слове значащий разряд с более высоким приоритетом, чем в предыдущем слове,

и вырабатывать в случае наличия такого разряда соответствующий сигнал и признак старшего значащего разряда последуюп1его слова. Оно может использоваться в качестве устрюйства прерывания, предназначенного для определения порядка обслуживания системы абонентов, каждый из которых имеет свой, отличный от других абонентов, приоритет на обслуживание.

Однако на практике довольно часто среди обслуживаемых абонентов встречаются абонент с одинаковыми приоритетами на обслуживание. В этом случае это логическое запоминающее устройство не способно отличить запросы на обслуживание от абонентов с одинаковыми приоритетами и вьфабатьгоать признаки обслуживания различных абонентов, имеющих одинаковые приоритеты.

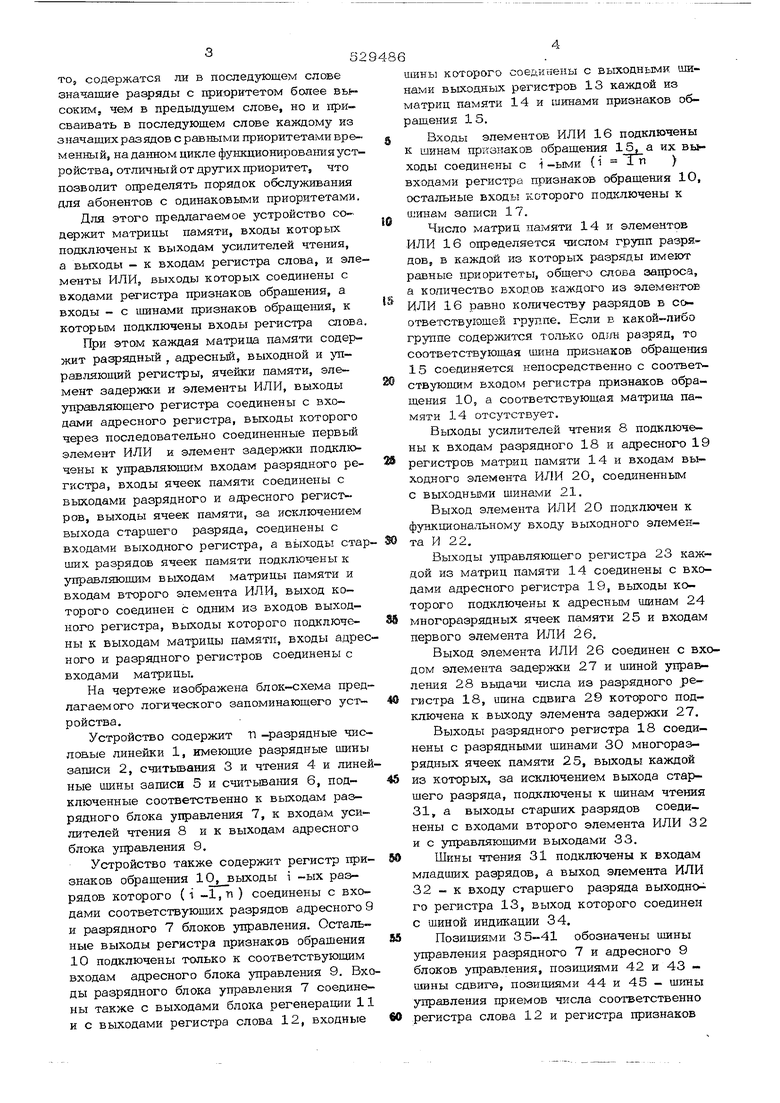

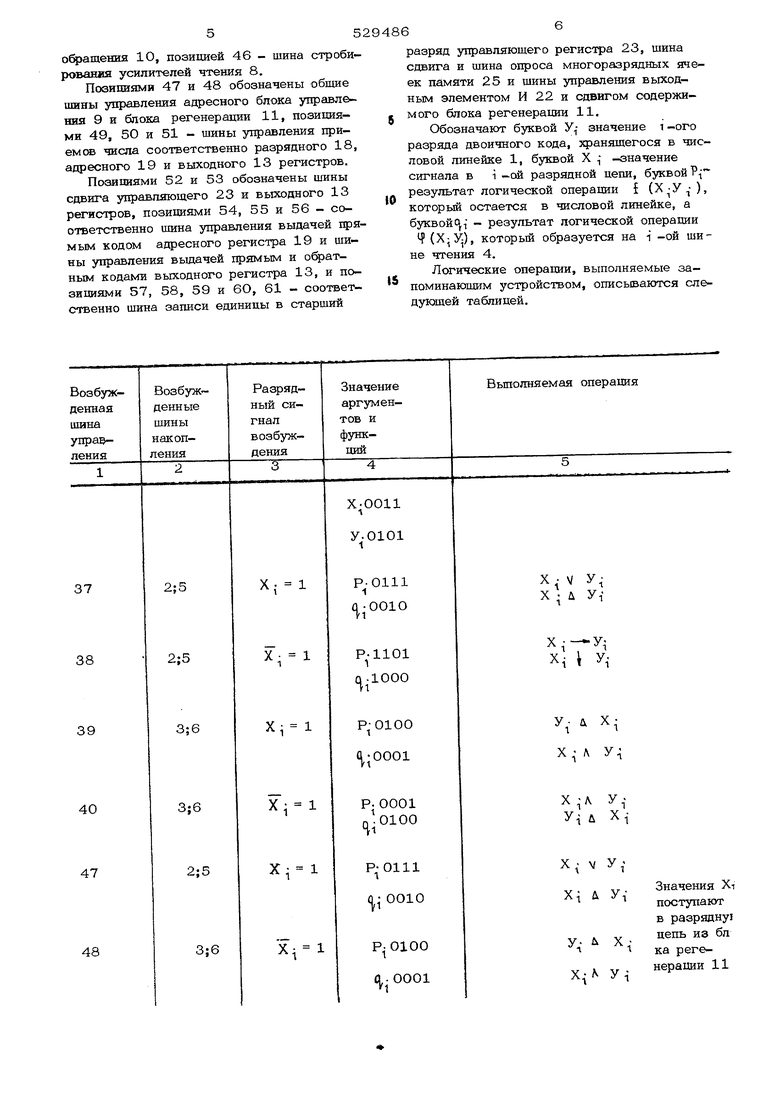

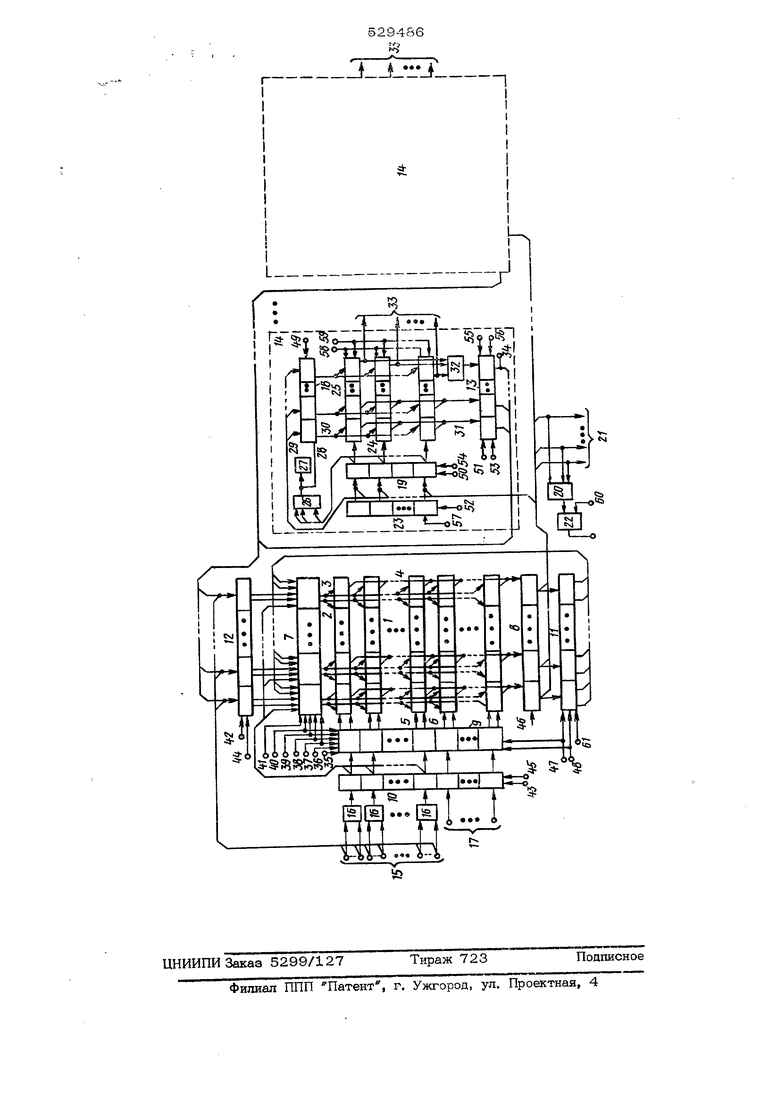

Цель изобретения - расширение функциональных возможностей логического запоминающего устройства, что позволит определять для последовательности двоичных слов, каждый из разрядов которых имеет свой приоритет (и при этом приоритеты некоторых разрядов равны по величине), не только то, содержатся ли в последз ощем слове значащие разряды с приоритетом более вь{ соким, чем в предыдущем слове, но и при сваивать в последующем слове канедому из значащих раз ядов с равными приоритетами вре менный, на данном цикле фушшионирования уст ройства, отличны и от других приоритет, что позволит определять порядок обслуживания для абонентов с одинаковыми приоритетами Для этого предлагаемое устройство содержит матрицы памяти, входы которых подключены к выходам усилителей чтения, а выходы - к входам регистра слова, и эле менты ИЛИ, выходы которых соединены с входами регистра признаков обращения, а входы - с шинами признаков обращения, к которым подключены входы регистра слова При этом каждая матрица памяти содержит разрядный , адресньй, выходной и управляюЕШЙ регистры, ячейки памяти, элемент задержки и элементы ИЛИ, выходы управляющего регистра соединены с входами адресного регистра, выходы которого через последовательно соединенные первый элемент ИЛИ и элемент задержки по ислючены к управляющим входам разрядного регкстра, входы ячеек памяти соединены с выходами разрядного и адресного регистров, выходы ячеек памяти, за исключением выхода старшего разряда, соединены с входами выходного регистра, а выходы ста ших разрядов ячеек памяти подключены к управляющим выходам матрицы памяти и входам второго элемента ИЛИ, выход которого соединен с одним из входов выходного регистра, выходы которого подключены к выходам матрицы памяти, входы адре ного и разрядного регистров соединены с входами матрицы. На чертеже изображена блок-схема пред лагаемого логического запоминающего устройства. Устройство содержит п -разрядные числовые линейки 1, имеющие разрядные шины записи 2, считьтания 3 и чтения 4 и лине ные шины записи 5 и считьюания 6, подключенные соответственно к выходам разрядного блока управления 7, к входам усилителей чтения 8 и к выходам адресного блока управления 9, Устройство также содержит регистр признаков обращения 10, выходы i -ых разрядов которого ( i -1,11 ) соединены с входами соответствующих разрядов адресного 9 и разрядного 7 блоков управления. Осталь ные выходы регистра призншсов обращения 10 подключены только к соответствующим входам адресного блока управления 9. Вхо ды разрядного блока управления 7 соединены также с выходами блока регенерации 11 и с выходами регистра слова 12, входнь е 6. шины которого соединены с ВЫХОДНЬЕЛИ шинами выходных регистров 13 каждой из матриц памяти 14 и шинами признаков обращения 13. Входы элементов ИЛИ 16 подключены к шинам признаков обращения 15, а их вь ходы соединены с i -ыми {i 1 п ) входами регистра признаков обращения 10, остальные входы которого подключены к шинам записи 17. Число матриц памяти 14 и элементов ИЛИ 16 определяется числом групп разрядов, в каждой из которых разряды имеют равные приоритеты, общего слова запроса, а количество входов каждого из элементов ИЛИ 16 равно количеству разрядов в соответствующей группе. Если в какой-либо группе содержится только один разряд, то соответствующая шина признаков обращения 15 соединяется непосредственно с соответ ствующим входом регистра признаков обращения 10, а соответствующая матрица памяти 14 отсутствует. Выходы усилителей чтения 8 подключены к входам разрядного 18 и адресного 19 регистров матриц памяти 14 и входам выходного элемента ИЛИ 20, соединенным с выходными шинами 21. Выход элемента ИЛИ 20 подключен к функциональному входу выходного элемента И 22, Выходы управляющего регистра 23 каждой из матриц памяти 14 соединены с входами адресного регистра 19, выходы которого подключены к адресным шинам 24 многоразрядных ячеек памяти 25 и входам первого элемента ИЛИ 26. Выход элемента ИЛИ 26 соединен с входом элемента задержки 27 и шиной управления 28 выдачи числа иа разрядного регистра 18, ишна сдвига 29 которого подключена к выходу элемента задержки 27. Выходы разрядного регистра 18 соединены с разрядными шинами 30 многоразрядных ячеек памяти 25, выходы каждой из которых, за исключением выхода старшего разряда, подключены к шинам чтения 31, а выходы старших разрядов соединены с входами второго элемента ИЛИ 32 и с управляющими выходами 33. Шины чтения 31 подключены к входам младших разрядов, а выход элемента ИЛИ 32 - к входу старшего разряда выходнсьго регистра 13, выход которого соединен с шиной индикации 34. Позициями 3 5-41 обозначены шины управления разрядного 7 и адресного 9 блоков управления, позициями 42 и 43 ины сдвига, позициями 44 и 45 - шины правления приемов числа соответственно егистра слова 12 и регистра признаков 55 обращения 10, позицией 46 - шина стробирования усилителей чтения 8. Позициями 47 и 48 обозначены общие ишны управления адресного блока управле -. ния 9 и блока регенерации 11, позициями 49, 50 и 51 - шины управления приемов числа соответственно разрядного 18, адресного 19 и выходного 13 регистров. Позициями 52 и 53 обозначены шины сдвига управляющего 23 и выходного 13 регистров, позициями 54, 55 и 56 - соответственно ишна управления выдачей пря мым кодом адресного регистра 19 и шины управления вьщачей прямым и офатным кодами выходного регистра 13, и позициями 57, 58, 59 и 6О, 61 - соответственно шина записи единицы в старший разряд управляющего регистра 23, шина сдвига и шина опроса многоразрядных ячеек памяти 25 и шины управления выходным элементом И 22 и сдвигом содержи- мого блока регенерации 11. Обозначают буквой У,- значение т -ого разряда двоичного кода, хрангащегося в числовой линейке 1, буквой X -значение сигнала в i -ой разрядной цепи, буквой Р{ результат логической операции f (), который остается в числовой линейке, а буквой - результат логической операции (т,). который образуется на i -ой шине чтения 4. Логические операции, выполняемые запоминающим устройством, описьшаются следукшей таблицей.

Продолжение табл. .

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое запоминающее устройство | 1980 |

|

SU886052A2 |

| Логическое запоминающее устройство | 1979 |

|

SU801101A2 |

| Логическое запоминающее устройство | 1977 |

|

SU674101A2 |

| Логическое запоминающее устройство | 1972 |

|

SU474847A2 |

| Логическое запоминающее устройство | 1979 |

|

SU864336A1 |

| ЛОГИЧЕСКОЕ ПОЛНОТОЧНОВ ЗАПОМИНАЮЩЕЕ L'rifc :ИГ УСТРОЙСТВОI.™™———- | 1973 |

|

SU374658A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU428450A1 |

| Логическое запоминающее устройство | 1974 |

|

SU608199A2 |

| Логическое запоминающее устройство | 1981 |

|

SU963099A1 |

| Ассоциативное логическое запоминающее устройство | 1972 |

|

SU485501A1 |

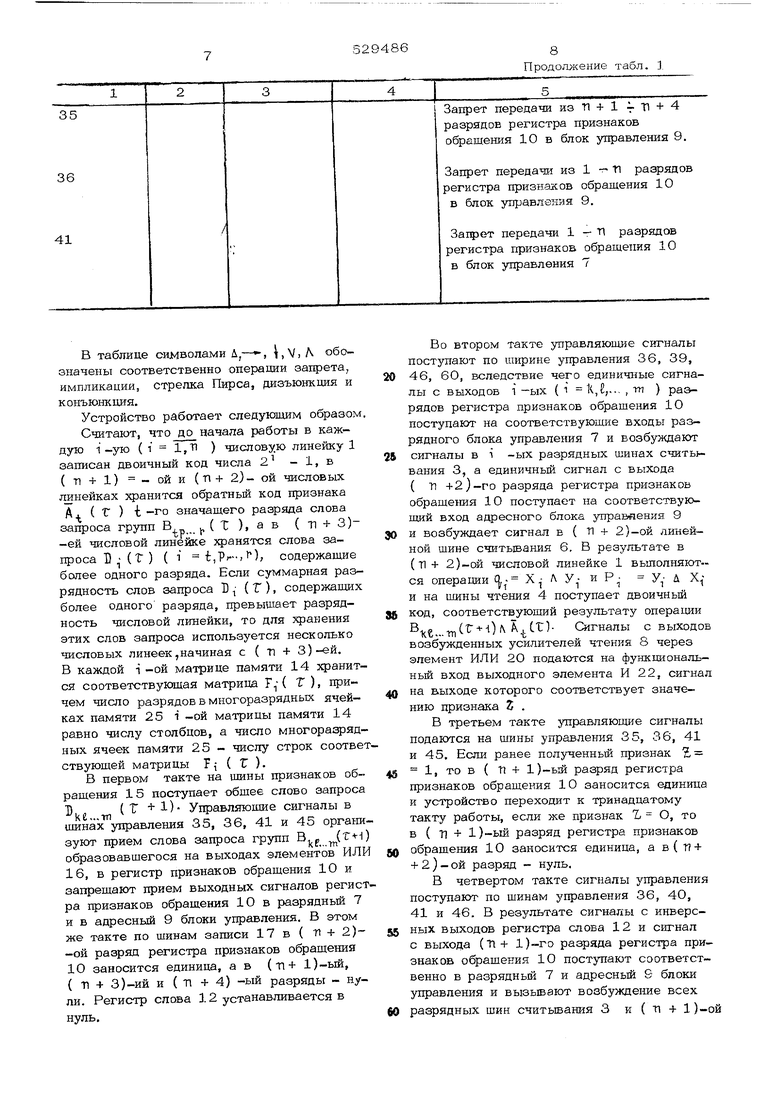

В таблице символами Д,, ,V, Л обозначены соответственно операции запрета, импликации, стрелка Пирса, дизъюнкция и конъюнкция. Устройство работает следующим образом Считают, что до начала работы в каждую 1-ую ( 1 1,Т1 ) числовую линейку 1 записан двоичный код числа 2 - 1, в (n + l) -ойи (11+ 2)-ей числовых л инейках хранится обратный код признака АА ( t ) {. -ГО значащего разряда слова запроса групп ... ,(Т;),ав (Т1 + 3) -ей числовой линейке хранятся слова запроса Б - (t ) ( 1 t,Pj-,f), содержащие более одного разряда. Если суммарная разрядность слов запроса Б - { Г ), содержащих более одного разряда, превышает разрядность числовой линейки, то для хранения этих слов запроса используется несколько числовых линеек,начиная с ( п + 3)-ей. В каждой 1 -ой матрице памяти 14 ранится соответствующая матрица ( Г ), причем число разрядов в многоразрядных ячейках памяти 25 i -ой матрицы памяти 14 равно числу столбцов, а число многоразрядных ячеек памяти 25 - числу строк соотве ствующей матрицы f{ ( Г ). В первом такте на щины признаков обращения 15 поступает общее слово запроса ( Т + ) УпраБЛ5Пощие сигналы в шинах управления 35, 36, 41 и 45 органи зуют прием слова запроса групп ( образовавщегося на выходах элементов ИЛИ 16, в регистр признаков обращения 10 и запрещают прием выходных сигналов регист ра признаков обращения 10 в разрядный 7 и в адресный 9 блоки управления. В этом же такте по шинам записи 17 в ( 11+2)-ой разряд регистра признаков обращения 10 заносится единица, а в (п + 1)-ый, ( п + 3)-ий и ( п + 4) -ый разряды - нули. Регистр слова 12 устанавливается в нуль. Во втором такте управляющие сигналы поступают по ширине управления 36, 39, 46, 6О, вследствие чего единичные сигналы с выходов 1 -ых ( 1 , } раэрядов регистра признаков обращения 10 поступают на соответствующие входы разрядного блока управления 7 и возбуждают сигналы в i -ых разрядных шинах считывания 3, а единичный сигнал с выхода ( И +2)-го разряда регистра признаков обращегшя 10 поступает на соответствующий вход адресного блока упрааяения 9 и возбуждает сигнал в ( п + 2)-ой линейной шине считывания 6. В результате в (Т1 + 2)-ой числовой линейке 1 выполняются операции - Л и у. д х,и на шины чтения 4 поступает двоичный код, соответствующий результату операции kt...) О гналы с выходов возбужденных усилителей чтения 8 через элемент ИЛИ 2О подаются на функциональный вход выходного элемента И 22, сигнал на выходе которого соответствует значению признака 2 . В третьем такте управляющие сигналы подаются на шины управления 35, 36, 41 и 45. Если ранее полученный признак Ъ 1, то в (11+ 1)-ый разряд регистра признаков обращения 10 заносится единица и устройство переходит к тринадцатому такту работы, если же признак Ъ О, то в ( и + 1)-ый разряд регистра признаков обращения 10 заносится единица, а в(т + + 2 ) - ой разряд - нуль. В четвертом такте сигналы управления поступают по шинам управления 36, 4О, 41 и 46. В результате сигналы с инверсных выходов регистра слова 12 и сигнал с выхода (71+ 1)-го разряда регистра признаков обращения 1О поступают соответстенно в разрядный 7 и адресньш 9 блоки правления и вызьюают возбуждение всех азрядных щин считьтания 3 и ( п + 1 )-ой 95 линейной шины счйтьшания 6, что обееяпечивает считывание из ( ц + 1)-ой числовой линейки 1 слова Дх (Т ), которое с выходе усипитепей чтения 8 заносится в блок регенерации 11. В пятом такте управляющие сигналы поступают по щинам управления 36, 41 и 4-7, что вызывает передачу сигналов с выходов блока регенерации 11 и с выхода ( f7-f l)-ro разряда регистра признаков обращения 10 соответственно в разрядный 7 и G ресньй 9 блоки и возбуждение разрядных 2 и ( п -г 1)-ой пинейной 5 шин записи, вслед ствие чего в ( п + 1)ой числовой линейке 1 вьшолняются операции X : V У{ к ( . X - U У. В результате в ( п + 1 )-ой числовой линейке 1 производится регенерайия слова А, ( t) . В шестом такте управляющие сигналы поступают по шина1и управления 35, 36, 41, 45 и 61. Вьшолняется сдвиг слова А, ( и ) в блоке регенерации 11 на один разряд в сторону младших разрядов. Ощиг выполняется как сдвиг обратного кода (т.е. в освободившийся заносится единица) Одновременно в регистре признаков обращения 10 выполняется запись нуля и единицы соответственно в ( п + 1)-ый и в {п + 4)-ый разряды по шинам записи 17. Угфавление работой устройства в седьмо такте производитсй сигналами, поступающими по тинам управления 36, 41 и 47. Вь1ходные сигналы блока регенерапии 11 и ( П + 4)-го регистра признаков обращения 10 подаются соответственно в разрядный 7 и адресный 9 блоки управления и выэьшают возбуждение разрядных 2 и ( п + 4)-ой линейной 5 шин записи. В результате осуществляется запись слова t А i (Т)( Т1+ 4)-ую числовую линейку 1. В восьмом такте управляющие сигналы поступают по шинам управления 36, 39, 46 и 60. В устройстве вьшолняется передача слова запроса групп В. „ ( 1), хранящегося в 1 -ых разряда ( i l,Ti) регистра признаков обращения 10, и выходного сигна ла ( п + 4)-го разряда этого же регистра соответственно в разрядный 7 и ад15есный 9 блоки управления, что вызьшает возбуждение К, -m -ых разрядных 3 и (п.+4)-ойо1Инейной бщин считывания. Врезультате в ( и + 4)-ой числовой линейке выполняются операции Р У Л Х и . Х|А у-в... (Г + )/2 Выходные сигналы усилителей чтения 8 про ходят через элемент ИЛИ 20 на функциональный вход выходного элемента И 22 на выходе которого формируется сигнал, со ответствующий значению признака f. В девятом такте по сигналам в шинах управления 36, 40 и 41 в устройстЕе выполняется передача сигналов с инверсных выходор регистра слова 12 и с выхода (71 + + 4)-го разряда регистра признакон обращения 10 соответственно в разрядный 7 и адресньй 9 блоки управпония, что вызывает возбуждение разрядных 3 и ( ti + 4)ой линейной 6 шин счйтьшания. В результате во все ( я + 4)-ой числовой линейки 1 заносятся нули. В десятом такте, управляющие етггналы поступают в шины управления 35, 36, 41 и 45. Производите запись единиц в (-П + f 1)-ы8 и ( Т + 2)-ой и запись нуля в ( Т1 + 4)-ый разряды регистра признаков обращения 10 по шинам записи 1 7. Если признак , сформкрованньга в восьмом такте, равен нулю, то устройство переходит к тринадцатому такту работы. Если же ф 1, то в одиннадцатом такте управляющие сигналы в шиках зшравленкя 36, 40, 41 и 46 производят настройку устройства на прием сигналов с инверсных выходов регистра слова 12 и сигналов с выходов ( Л + 1)-го и ( п + + 2)- го разрядов регистра 11риэна1« в обращения 10 соответственно в разрвдпьй 7 и адресньй 9 блоки управления, что вызывает возбуждение разрядных 3 и { п 1)-ой к и ( П+ 2)-ой линейных 6 шкк считьтания. В результате выполняется очистка ( п + 2)-ой числовой пинейкн 1 и считьюание из ( Т + 1)ой числовой ли нейки слова А ( f ), которое поступает с выходов усилителей чгения 8 в блок регенерации 11. В двенадцатом такте настройка устрой ства производится по шпкам управления 36. 41 и 47. Выходные сигналы блока регенерации 11 и { п + 1)-го к ( п +2) -го разрядов регистра признаков обращения 10 поступают соответственно в разрядный 7 и адресный 9 блоки управления и вьгзывают Боабунщение разрядных 2 и {и + 1} -ой и ( п + 2)-ой линейных 5 шин записи, вследствие чего вьшолняется запись слова А ( г ) в ( п + 1)-ую ив ( п + +2).ую числовые пинейки 1. После завершения операций двенадцатого такта устройство переходит к шecтнaйцaтo y такту работы. В тринадцатом такте 5Т равляющие сигналы поступают по шинам угфавления 35, 40, 41 и 46. Выходные сигналы с инверсных выходов регистра слова 12 и с выходов 1 -ых разрядов ( и,& ,.., ,т.) регистра признаков обращения 10, в которых записаны значащие разряды слова за(Т + 1), подаются проса групп В соответственно в разрядный 7 и адресный вызьюают Бозбуж9 блоки управления и -ых а к ,..., дение разрядных 3 и .,., т. ) линейных 6 шин считывания. В результате производится считывание содержимого i -ых числовых линеек 1 и на выходах возбужденных усилителей чтения 8 формируется признак А ( Т + 1) старшей группы общего слова запроса Dxe--... гп (fC + 1), содержащей хотя бы один значащий разряд, который поступает на вьь ходные шины 21 логического запоминак щего устройства, а также заносится в блок регенерации 11. В четырнадцатом такте управляющие си налы в шинах управления 36, 38 и 41 вы зьтают передачу сигналов с инверсных выходов регистра слова 12 и с выходов { Т| ч- 1)-го и ( Т1 + 2)-го разрядов регистра признаков обращения 10 в разрядный 7 и адресный 9 блоки управления и возбуждение разрядных 2 и ( И + 1)-ой и ( л + 2)-ой линейных шин 5 записи, что приводит к записи в ( Т1 + 1)ую ив (Ti + + 2)-ую числовые линейки 1 кода 2 -1. В пятнадцатом такте по сигналам в шинах управления 36, 41 и 48 в устройстве производится передача сигналов с выходов блока регенерации 11, т.е. слова А ( и сигналов с выходов (77 + 1 ) -го и { П + 2)-го разрядов регистра признаков обращения 10 соответственно в разрядный 7и адресный 9 блоки управления, что вь1зывает возбуждение разрядных шин считывания 6, соответствующих значащим разрядам слова А(Т +1) и (п + 1)-ой и { Ti + 2)-ой лшieйныx шин считьюания 6 8результате в ( Т1 + 1)-ой и ( л + 2)-ой числовых линейках 1 вьшолняются операции ДХ- и О Х- Л ,что приводит к формированию в этих числовых линейках слов А,.( Т + 1), представляюащх собой обратный код приоритета старшего значащего разряда слова запроса групп В к.е ...777 (Т + 1). В шестнадцатом такте управляющие сигналы поступают по ошнам управления 35, 36, 41, 44 и 45. В устройстве производится загшсь нулей в ( TI + 1)-ьш и в ( П + 2)-ой и единицы в ( Т1 + 3)-ий разряды регистра признаков обращения 10, по ступающих по шинам записи 17, и прием в регистр слова 12 слов запроса Т + 1) l -ых (1 V .-.. ) групп общего слова запроса ВК ...тС + 1), в которых содержится более одного разряда и имеется хотя бы один значащий разряд. В семнадцатом такте управляющие сигна посаупают по шинам управления, 36, 39, 41, 46 и 50. Выходные сигналы регистра слова 12 и ( п + 3)-го разряда регистра признаков обраидения 10 подаются в разрядный 7 и адресный 9 блоки управления и вызьшают возбуждение разрядных шин считывания 3, соответствующих единичным выходным сигналам регистра слова 12, и ( Т) -f 3)-ей линейной шины считьтания 6. В { я + 3)-ей числовой линейке 1 вьшол- няются операции У Д Х и Х,-Л Л над разрядами предыдущих И -( Г ) и последуюцщх D ( Т + 1) слов запроса i -ых групп. На выходах усилителей чтения 8 формируются слова (Т + 1) Xi( Т+1)( Т), которые заносятся в блок регенерации 11 и каждое i -ое из которых поступает в адресный регистр 19 i -ой матрицы памяти 14. Если для хранения слов запроса ( Т ) i -ых групп требуется несколько числовых линеек 1, то операции по тактам 16-32 повторяются столько раз, сколько числовых линеек необходимо для фанения слов запроса ( Т ). Причем в вьшолнении операций по каждому такому циклу участвуют только те матрицы памяти 14, которые соответствуют обрабатываемым в данном цикле словам запроса И, ( Т ) и ( Г + + 1), а в шестнадцатом такте единица заносится только в тот разряд регистра признаков обращения 10, который соответствует числовой линейке 1, хранящей требуемые в данном цикле слова запроса Б; (Г ). В восемнадцатом такте управляющие сигналы поступают по шинам управления 35, 36, 41, 45, 51, 54 и 59. Производится запись единицы в ( я + 4)-ьш разряд регистра обращения 1О и сброс в нуль регистра слова 12. В матрицах памяти 14 вьшолняется опрос адресных регистров 19, что вызьюает возбуждение адресных шин 24, соответствующих значащим разрядам.( Т + 1), хранящихся в адресных регисррах 19, и считьюание содержимого соответствующих многоразрядных ячеек памяти 25, Считьюание выполняется без разрушения информации. В результате в каждой из матриц памяти 14 в выходном регистре 13 формируется слово, номера X/ значащих разрядов которого равны временным приоритетам, присвоенным в предьщущем цикле функционирования устройства значащим разрядам, общим для слов запроса ( Т ) и Di ( Г + 1). В девятнадцатом такте управление работой устройства производится сигналами, поступающими по шинам управления 36, 40, 41 и 55 .Сигналы с инверсных выходов егистра слова 12 и с выходов ( Т) + 3)-го { Т1 + 4)-го разрядов регистра признаков обращения 10 подаются соответственно в азрядньй 7 и адресный 9 блоки управлеия и возбуждают разрядные 3 и ( П + 3)ую и ( и + 4)-.ую линейные 6 тины считывания, что вызывает занесение нулей во все разряды ( п + 3)-ей и ( Т) + 4)-ой числовых линеек 1. В этом же такте в матрицах памяти 14 производится опрос выходных регистров 13, Сигнал на шине индикашш 34 каждой i -ой матрицы памяти 14 соответствует значению признакар Если все признаки р. 1, то устройство переходит к двадцать первому такту работы. Если некоторые из признаков О, то в двадцатом-такте в соответствзтощих матрипах памяти 14 под воздействием сигналов в шинах управления 35, 36, 41, 54 и 58 производится опрос адресных регистр 19 и сдвиг содержимого многоразрядных ячеек памяти 25, подключенных к возбужденным адресным шинам 24, на один разряд в сторону старших разрядов, что эквивалентно уве личению временных приоритетов значащих разрядов, общих для слов запроса Б ( Т ) и D,-( Г + 1). В двадцать первом такте управляющие сигналы поступают по шинам управления 36, 41 и 47. В результате выходные сш налы блока регенерации 11 и сигналы с вы ходов ( Л + 3)-го и ( п + 4)-го разрядов регистра признаков обращения 10 подаются в разрядный 7 и адресньй 9 блоки управления и возбуждают разрядные шины записи 2, соответствующие единичным разрядам слов ( Г + 1), хранящихся в блоке регенерации 11, и ( п + 3)-ью и ( Л + + 4)-ую линейные шины загшси 5, вследствие чего в ( Т1 + 3)-ей и в ( п + 4)-ой числовых линейках 1 производится запись слов ( Т + 1). В двадцать втором такте управляющие сигналы поступают по шинам управления 35 36, 41, 44, 45, 51, 54 и 59. Вьшолняется запись нуля в ( п + 4)-ый разряд регистра признаков обращения 10 по шина записи 17 и запись слов запроса ( + 1) в регистр слова 12 по шинам признаков обращения 15. В этом же такте в матрицах памяти 14 троизводится опрос адресных регистров 19 считывание содержимого многоразрядных ячеек памяти 25, соответствующих возбуж денным адресным шинам 24, и формирован в выходных регистрах 13 слов, значащие разряды которых соответствуют столбцам матриц ( Т), имеюшлм единичные элементы. . В двадцать третьем такте возбуждены шины управления 36,39 и 41. Выходные сигналы регистра слова 12 и ( 71+ 3)-го разряда регистра признаков обращения 10 поступают соответственно в разрядньй 7 и адресный 9 блоки управпения и вызьюа 6ют возбуждение разрядных шин считывания 3, соответствующих единичным вькодным сигналам регистра слова 12, и ( П + 3)-ей линейной шины считьшания 6, В результате в разрядах ( Ti + 3)-ей числовой линейки 1 выполняются операции Х и,. X,- л ив этой числовой линейке 1 формируется результат операции i( X + 1)л лБ ( Г + 1). В двадцать четвертом такте управляющие сигналы поступают по шинам управления 35, 36, 41 и 45. Производится запись нуля и единицы соответственно в ( Т) + 3)-ий и в { Т + 4)-ый разряды регистра признаков обращения Ю по шинам записи 17, а также сброс в нуль блока регенерации 11 и адресных регистров 19. В двадцать пятом такте под действием управляющих сигналов в шинах управления 36, 37, 41 и 46 выходные сигналы регистра слова 12 и ( П + 4)-го разряда регистра признаков обращения 10 поступают в разрядный 7 и адресный 9 блоки управления и вызьтают возбуждение разрядных шин за писи 2, соответствующих единичным разрядам содержимого регистра слова 12, и ( Т1 + 4)-ой линейной шины записи 5. В { п + 4)-ой числовой линейке 1 выполняются операции ,- и - Х,-ЛУ,, на выходах усилителей чтения Э формируется результат операции i:( + 1)( Т + 1), который заносится в блок регенерации 11. В двадцать шестом такте управляющие сигналы поступают по шинам управления 35, 36, 41 и 45. Производится запись единицы и нуля соответственно в ( п +3) -ий и в ( П + 4)-brtj разряды регистра признаков обращения 10. Регистр слова 12 сфасьтается в нупь. В двадцать седьмом такте организация работы устройства щзоисходит по сигналам в шинах управлеш1Я 36, 41 и 47. Содер жимое блока регенерации 11 и ( П + 3)-го разряда регистра признаков обращения 1О поступает в разрядньш 7 и адресный 9 блоки управления, что вызывает возбуждение соответствующих разрядных 2 и линейной 5 щин записи. В разрядах (Т1.+3)-ей числовой линейки 1 выполняются операции Р; X иО, X & и в линейку записьшается результат операции ( A Ct- -OlvC&.(T -tUl} Ct- -1)l-iD В двадцать восьмом такте управляющие сигналы поступают по шинам управления 36, 40, 41, 46 и 50. Сигналы с инверсных выходов регистра слова 12 и выхода ( П + 3)-го разряда регистра признаков обращения 10 подаются соответственно в разрядный 7 и адресный 9 блоки управлеНИИ и возбуждают разрядные 3 и ( и + 3)-ью линейную 6 шины считывания, В реауп тате в ( Т1 + 3)-ей числовой линейке 1 производится считывание слов &D, которые с выходов усилителей чтегшя 8 заносятся в адресные регистры 19 соответствующих матриц памяти 14. В двадцать девятом такте по сигналам в шинах управления 35, 36, 41, 44 и 56 в устройстве производится передача инверс ных кодов содержимого выходных регистров 13 матриц памяти 14 в регистр слова 12, причем порядок расположения кодов в регистре слова соответствует порядку расположения соответствующих слов запроса Б - ( Г ) i -ык групп. В тридцатом такте настройка устройства производится сигналами в шинах управления 36, 37, 41 и 53. Содержимое регистра слова 12 и ( П + 3)-го разряда регистра признаков обращения 10 поступает соответ ственно в блоки 7 и 9 угфавления, вызывая возбуждение разрядных шин записи 2, соответствующих нулевым сигналам с вь ходов регистра слова 12, и (л + 3)-ей линейной шины записи 5. В результате со держимое регистра Слова 12 записьшается в ( Т1 + 3) ью числовую шшейку 1. В этом же тазсте в выходных pei-истрах 13 матриц памяти 14 выполняется сдвиг на один разряд в сторону младших разрядов с занес& нием единицы в освободившийся разряд, В тридцать первом такте управляющее сигналы nocTynasoT по шинам управле1-п-1Я 35,36, 41, 44 и 55. Вьшолняется пере дача прямых кодов содер: кимого выходных регистров 13 матриц памяти 14 в регистр слова 12. В тридцать втором такте .тфавляющие сигналы поступают по шинам управления 36,39, 41, 46, 49 и вызьтают передачу выходных сигналов регистра слова 12 и ( Т1 ч- 3)-го разряда регистра признаков обращения 10 соответственно в блоки 7 и 9 управле шя. Происходит возбуждение разрядных шин считывания 3, соответствую ших единичным выходным сигналам регист ра слова 12, и ( П + 3)-ей линейной шины считывания 6. В ( Ti + 3)-ей числовой линейке 1 вьшопняются операхщи Л 4 Ху YI над содержимым этой числовой линейки и содерлохмым регистра сло ва 12. Результат операции с выходов усилителей чтения 8 поступает в разрядные регистры 18 соответствующих матриц памяти 14. В каждом из регистров 18 будет записано не более одного значащего разряда номер которого равен номеру старшего из незанятых ра ядных сечений матрицы памя-.и 14. Сечение считается незанятым, если оно не содержит значащих разрядов. В тридцать такте тхравляющие сигналы подаются по шинам управления 35, 30, 41, 45 и 57. Производится запись единиц в 1 -ые ( i 1, п ) разряды регистра признаков обращения 10, в старшие разряды управляющих регистров 23 матриц памяти 14. В тридцать четвертом такте ттравляющие сигнэлы поступают по шинам управления 35, 36, 41 и 44. В младший разряд регистра слова 12 записывается единица в остальные разряды - нули. В тридцать пятом такте управление уст ройством произБодится по шинам управления 35,37 и 41. В матрицах памяти 14 выходным сигналом значащего разряда каждого из пpaвляющиx регистров 23 производится опрос соответствующехо разряда адресного рогистра 19. Если в опрошенном разряде адресного регистра 19 была записана единица, то выходной сигнал этого разряда возбуждает пош.люченную к нему адресную ия-гау 24 и проходит через элемент ИЛИ 26 на шину атравления 28 выдачей числа разрядного регистра 18 и на вход элемента задержки 27, создающей задержку на один такт, Как упоминалось ранее, в каждом разрядном регистре 18 находится не более одного значащего разряда и только з том случае, если Б соответствующей матрице памяти 14 имеется хотя бы одно иегаь я тое разрядное сечение. Поэтому при опросе каждого из разрядных регистров 18 сигналом, поступающг м по шине управления 28, единичный выходной с.игнап может появиться не более, чем в одной разрядной ши:н:е 30. Наличие в i .ой матрице памяти 14 возбуадепных -ой адресной 24 и -ой разрядной 30 шин вызывает запись единицы в Д. -ый разряд V ой многоразрядной ячейки памяти 25, что отражает присвоение временного приоритета, численно равного/jj - ;) -ому значащему разряду слова запроса J (Т + 1). В этом же такте в числовых линейках, соответствующих тем из -i -ых ( i Гд ) разрядов регистра признаков обращения 10. в которых содержатся единицы, производится запись единиц в разряды, соответствук -. щие значащему разряду регистра слова 12. В тридцать шестом такте управляющие сигналы поступают по шинам управления 35, 36,41, 42, 43 и 52, В устройстве выподняется сдвиг содержимого регистра слова 12 и регистра 1тризнаков обращения 10 на один разряд в сторону старших разрядов, а содержимого управляющих регистров 23 в С1хэрону младших разрядов, В этом же такте под воздействием выходных сигналов тех элементов задержки 27, на входы которых в предыдущем такте поступили единичные сигналы, производится сдвиг содержимого соответствуюац х разрядных регистров 18 на один разряд в сторону младших разрядов. Операции по тридцать пятому и тридцать шестому тактам повторяются Ti раз, В результате в каждой т -ой числовой лзгаейкеД будет сформирован двоичный код числа 2 -1, т.е. будет осуществлена регенерация содержимого этих числовых ли- неек, а содержимое многоразрядных ячеек памяти 25 каждой из матриц памяти 14 отражает распределение временных приоритетов между значащими разрядами соответствующего слова запроса Б ( Т -f 1). В тридцать седьмом такте управляющие сигналы подаются по шинам управления 35, 36, 41 и 45. Производится запись единиц в П-ый, { П + 3)-ий и в { И + 4)- -ый разряды регистра признаков обращения 10. В тридцать восьмом такте настройка устройства вьшопняется сигналами, поступающими по щинам управления 36, 40, 41 46 и 50, Сигналы с инверсных выходов регистра слова 12 и с выходов П-го, ( П + + 3)-го и ( п + 4)-Г:0 разрядов регистра признаков обращения 10 подаются соответственно в разрядный 7 и ащзесный 9 блоки управления а возбуждают все разрядные 3 и У1-ую, ( + 3)-ью и ( n-i- 4)-ута линейные 6 шины считьюания. Вьшопняется считьюание двоичногю кода числа 2-1 из И ой к считывание содержимого из ( Ш + 3)-ей и ( Т1 + 4)-ой числовых линеек 1. В результате возбуждаются все усилители чтения 8, и сигналы с их выходов производят запись единиц во все раэряды блока регенерации 11 и адресных регистров 19. В тридцать девятом такте управляющие сигналы поступают по шинам управления 35, 36, 41 и 45. Вьшолняется запись нулей в ( ri + 3)-ий и ( П + 4)-ый разряды регистра признаков обращения 10. В сороковом такте по сигналам в шинах управления 36, 41,47, 54 и 59 в устройстве осуществляется передача выходных сигналов блока регенерации 11 и и -го pas ряда регистра признаков обращения 10 в разрядный 7 и адресньи 9 блоки управлени что вызьюает возбуждение всех разрядных 2 и П -ой линейной 5 шин записи. В результате в п-ой числовой линейке 1 вьтол няется регенерация двоичного кода числа 2 -1. В этом же такте выходные сигаалы адр ных регистров 19 вызывают возбуждение всех адресных шин 24, и в матрицах намят-и 14 производится опрос содержимого мног разрядных ячеек памяти 25, выходные сиг налы старших разрядов которых поступают на управляющие выходы 33. Номер V возбужденного управляющего выхода 33 каждой из матриц памяти 14 равен номеру того значащего разряда соответствующего слойа запроса Б ( f ч- 1), которому в данном цикле функционирования устройства присвоен наивысший в данном сповс запроса D (Г + ь 1) временны приоритет. В сорок первом такте управляюш1 е сигналы поступают по шинам управления 35, 36, 41, 44 и 45. В устройстве производится прием по шинам признаков обращения 15 в регистр слова 12 слов запроса ( Г + 1), содержащих более одного разряда, в ( П + 3)-ий регистра признаков обращения 10 по шинам записи 17 заносится единица, а ( Т1 + 4)-ый и в п -ый разряды - нули. В сорок втором такте по сигналам в шинах управления 36, 41 и 37 в устройстве 1ФОИСХОДИТ передача выходных сигналов регистра слова 12 и ( п + 3)-ге) ргзр5ща регистра признаков обращения 10 соответственно в разрядный 7 и адресный 9 блоки управления, что вызьшает возбуждение разрядных шин записи 2, соответствующих значащим разрядам двоичного кода, хранимого в регистре слова 12, и (п + 4- 3)-ей линейной шины заплси 5, Б результате в ( Т1 + 3)-ью числовую линейку 1 будут записаны слова запроса D ( Т + 1). На этом цикл функционирования логического запоминающего устройства заканчздваетсй. Формула изобретения 1. Логическое запоминающее устройство, содержащее числовые линейки, подключенные соответственно через разрядный и адресный блоки управления к регистру слова и регистру признаков обращения и через усилители чтения - к входам выходного элемента ИЛИ и блока регенерации, выходы которого соединены с входами разрядного блока управления, подключенными к выходам регист- ра признаков обращения, и шины признаков обращения , отличающееся тем, что, с целью расширения функциональных возможностей устройства, оно содержит матрицы памяти, входы которых подключены к выходам усилителей чтения, а выход к входам регистра слова, и элементы ИЛИ, выходы которых соединены с входами регистра признаков обращения а входы - с шинами признаков обращения, к которым подключены входы регистра слова, 2. Устройство ПОП.1, отличающееся тем, что каждая матрица па

мяти содержит разрядный, адресный, выходкой и управляющий регистры, ячейки памяти, элемент задержки и элементы ИЛИ, выходы управляющего регистра соединены с входами адресного регистра, выходы которого через последовательно соединенные первый элемент ИЛИ и элемент задержки подключены к управляющим входам разрядного регистра, входы ячеек памяти соединены с выходами разрядного и адресного регистров, выходы ячеек памяти, за исключением выхода старшего разряда, соединены с входами выходного регистра, а выходы старших разрядов ячеек памяти подключены к управляющим выходам матрипы памяти и входам второго элемента ИЛИ, выход которого соединен с одним из входов выходного регистра, выходы которого подключены к выходам матрицы памяти, входы адресного и разрядного регистров соединены с входами матрицы.

Источники информации, принятые во внимание при экспертизе:

2,Авт. свид. NP 490183, М.Кл Gil С 15/ОО, 1974 г.

Авторы

Даты

1976-09-25—Публикация

1975-01-14—Подача