1

Предлагаемое изобретение относится к области вычислительной техники и может быть использовано при построении цифровых интегрирующих машин (ЦИМ) и других устройств, оперирующих с величинами и их приращениями.

Р1звестны цифровые интегрирующие машины, включающие в себя устройство для выделения приращения, которое состоит из блока выделения группы старщих разрядов, блока памяти, блока выделения приближенного значения приращения, счетчика тактов.

Приращение результата любой операции (умножения, деления, извлечения квадратного корня и др.) есть частное от деления одного последовательпого кода Р на другой последовательный код S, т. е.

AZ S

Выделение

приращения из отношения --

осуществляется с помощью устройства для выделения приращений. Для представления приращений в этих устройствах используется комбинированная щкала вида ± (О, 1, 2, ... 2 2, 1, 2, , ..., ).

Основными недостатками устройства являются невысокая скорость отработки начальных условий и сравнительно низкая точность вычислений величин на участках их быстрого изменения.

Цель изобретения - повышение точности

и быстродействия устройства.

Для этого в устройство введен блок формирования сигналов изменения масштаба приращения, один из входов которого соединены с одннм из входов блока выделения приближенного значения приращения, счетчика тактов, блока выделения группы старших разрядов и с одним из выходов блока формирования и хранения масштабов приращения, а другие входы подключены к входным клеммам устройства, блок формирования и хранения масштабов приращения, один из входов которого соединен с одним из выходов блока формирования сигналов изменения масштаба приращения, другой выход которого соединен

с одним из входов блока выделения приближенного значения приращения, блок задержки, один вход которого соединен с выходом блока формирования и хранения масштаба приращения, а выход - с одним из входов

счетчика тактов, другие входы которого подключены к входным клеммам устройства, а выход - к одним из входов блока выделения приближенного значения, выход которого соединен с одним из входов блока памяти, к друтому входу которого подключен выход блока

выделения группы старших разрядов, причем другие входы блока задержки и блока формировапия и храпения масштаба прирап1,ения подсоедипепы ко входу устройства, а выход б.шка памяти - к выходу ycTpoiicTBa.

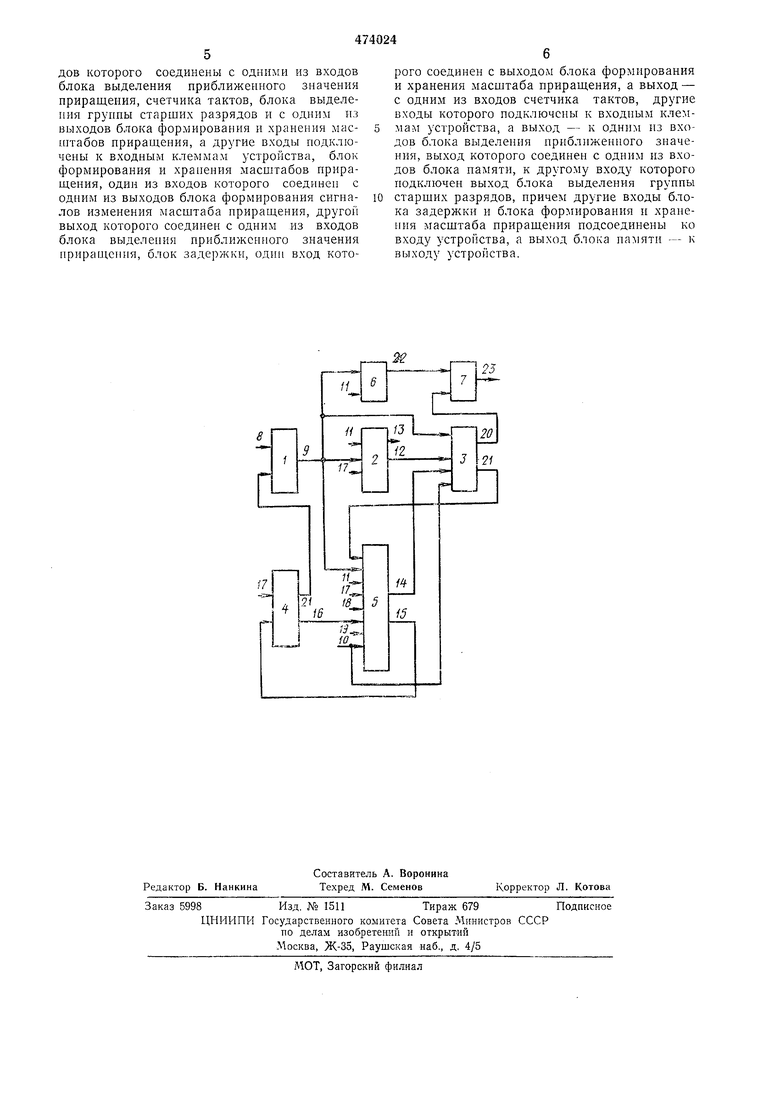

Структурная схема устройства для выделепия прираш,е11ия изображена иа чертеже, где 1 - блок задержки последовательного кода 5 на О, 1,2,..., V тактов; 2 - счетчик тактов; 3 - блок выделения приближенпого значепия приращения (AZ); 4 - блок формирования и хранения масштаба нрпращения; 5 -блок формирования сигналов изменения маснггаба; 6 - блок выделения группы старших разрядов из кода S; 7 - блок памяти; 8 - вход, на которы| 1 ноступает последовательный код S; 9 - выход, с которого снимается носледовательны код S; 10 - вход, на который поступает последовательный код Р; 11 - входы, на которые ностуиают тактовые пмнульсы; 12 -- выход, с которого снимаются сигналы, уиравляюпхне переписью разрядов кода Р в блок выделения приближеииого зпачеиия ирираш,ения; 13 - выход, с которого снимается сигнал максимальпого показания счетчика; 14 - выход, с которого снимается сигнал записи единиц в блок выделепия приближенного значения приращения; 15 - выход, с которого снимаются сигналы изменения масштаба; 16 - выход, с которого снимается сигнал наличия текущего масштаба больше минимального; 17 - входы, на которые подаются сигналы начальной установки в нулевое состояние соответствующих блоков; 18- вход, на который подается тактовый импульс знака; 19 - вход, иа который подается сигпал окончания текущего щага вычнслений; 20 - - выход, с которого сннмается нриближепное значение приращения Дл; 21 выход, с которого снимается масштаб приращения; 22 - выход, с которого снимается группа старших разрядов кода S; 23 - выход, с которого сннл ается результата онерации AZ.

В основу ностроения нредлагаемого устройства положен способ выделения приращеin-iii, отличающийся от существующих тем, что все Боз.можные приращеиия величии, участвующих в вычислениях, представляются набором целых двоичных чисел из некоторого дианазона. Этому набору на каждом шаге вычислений в зависимости от скорости нзмеиения величии, автоматически ирисваивается онределеппый вес ± (О, 1,2,..., 2 - 2, 2 - 1) М, где yVl 2, 2, 22, . . . , -- маспггаб (вес) мпогоразрядных приращений.

Веса приращений определяются но следующему правилу: в даином /-м щаге вычислений формируется сигнал увеличения масщтаба приращений, выделяе.мых в следующем (i + 1)-м шаге, если хотя бы одно приращение i-ro шага выходит за верхнюю границу принятого диапазона, и сигнал уменьшения масштаба, если выход за верхнюю границу отсутствует.

Особенностью способа, облегчающей его

техническую реализацию, является то, что масштаб в запоминаюшее устройство приращений не записывается, так как для всех приращений одного тага оп является одним и

тем же.

Устройство функционирует следующим образом. При минимальном масщтабе М- 2° нриран;еиие результата операции представляет собой целую часть от деления кода Р на

код 5, т. е.

Г Р

7 -

z

L 5-9

15 где - символ выделеиия целой части.

Предположим, что па /-м щаге приращения нредставляются в масштабе М- 1 , т. с.

( 1

AZ;r

- ч 5,-2 J

Если приращение результата хотя бы одпой операции t-ro щага выходит за верхнюю границу диаиазона ± (О, 1, 2, ... , 2, 2 1), то формируется сигнал увеличения масштаба, по которому к содержимому счетчика блока 4 добавляется «1. Добавление «1 ироисходит при появлении первого переполнения

(-ГО Шага. Последующие переполнения /-ГО шага состояния счетчика блока 4 не меняют. В очередном (i + 1)-м щаге все приращения иеремепных будут представлены в масщтабе Mi+i 2+ , т. е.

7 -Г + 1

- S,,,2/+i JOoc.ie того как масштаб М достигнет максимал1 ного значения , дальнейшее увеличение его прекращается.

Аналогичным путем осуществляется уменьHicHHe масштаба. Если на г-м ишге ни одно из нриращений не вышло за верхиюю границу диапазона, то формируется сигнал уменьшения масштаба, по которому содержимое реверсивного счетчика блока 4 умеиьщается на единицу. В очередном (( + 1)-м щаге приращения переменнь1х будут представлены в масштабе Л1г-м 2- , т. е.

Г i+i 1 AZ/-J-1 „ , ,

L J

Предмет- и з о б р е т е н и я

Устройство для выделеиия приращения, содержандее блок выделения группы старщих

разрядов, блок памяти, блок выделения приближенного значения приращения, очетчиктактов, отличающееся тем, что, с целью повышения точности и быстродействия устройства, в него введен блок формирования сигналов изменения масштаба приращения, одни из входов которого соединены с одними из входов блока выделения приближеиного значения приращения, счетчика тактов, блока выделения груииы старших разрядов и с одним из выходов блока формирования и хранения масштабов ирираш,ения, а другие входы нодключены к входным клеммам устройства, блок формирования и хранения масштабов нрираш,ения, один из входов которого соединен с одним из выходов блока формирования сигналов изменения масштаба ирирашения, другой выход которого соединен с одним из входов блока выделения приближенного значения ириран ения, блок задержки, один вход которого соединен с выходом блока формирования и хранения масштаба приращения, а выход - с одним из входов счетчика тактов, другие входы которого подключены к входным клеммам устройства, а выход - к одним из входов блока выделения приближенного значения, выход которого соединен с одним из входов блока памяти, к другому входу которого подключен выход блока выделения группы старших разрядов, причем другие входы блока задержки и блока формирования и хранения масштаба приращения подсоединены ко входу устройства, а выход блока памяти - к выходу устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой линейный интерполятор | 1989 |

|

SU1631518A1 |

| Устройство для вычисления квадратного корня числа в модулярной системе счисления | 1985 |

|

SU1317434A1 |

| УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ ЭЛЕКТРОКАРДИОСИГНАЛОВ | 2003 |

|

RU2256400C1 |

| Устройство для измерения расстояния до места повреждения в линиях электропередачи и связи | 1988 |

|

SU1597799A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1675849A1 |

| УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ ЭЛЕКТРОКАРДИОСИГНАЛОВ | 2010 |

|

RU2452364C1 |

| Следящий аналого-цифровой преобразователь | 1985 |

|

SU1338073A1 |

| Устройство для решения систем линейных дифференциальных уравнений | 1985 |

|

SU1252792A1 |

| Цифровое устройство для автоматического управления движением шахтной подъемной машины | 1969 |

|

SU475336A1 |

| Цифровой линейный интерполятор | 1987 |

|

SU1434406A1 |

Авторы

Даты

1975-06-15—Публикация

1973-07-16—Подача