ИзоРретение г тносится к автоматике и яычук ли тех шке н может быть использовано ;у1я преобразования быстроиаменяюкшхся аналоговых сигналов в цифровой код.

Целью изобрепения является повышение точности путем предотвращения возникновения режима автоколебаний,

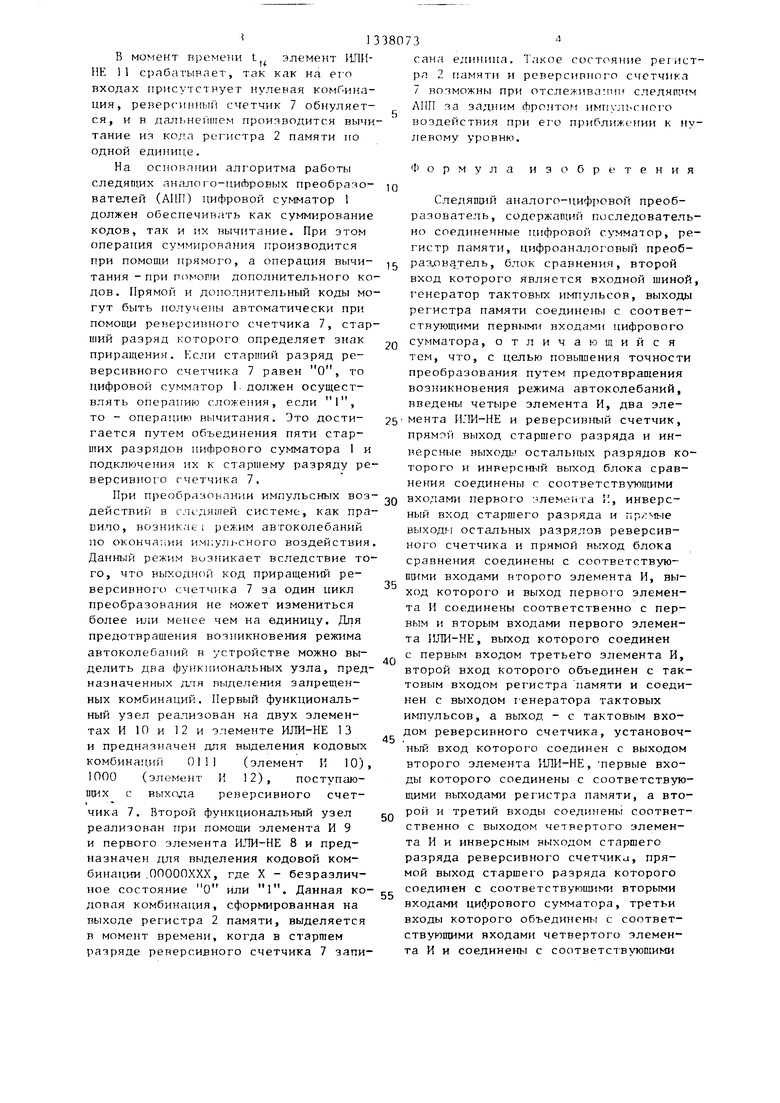

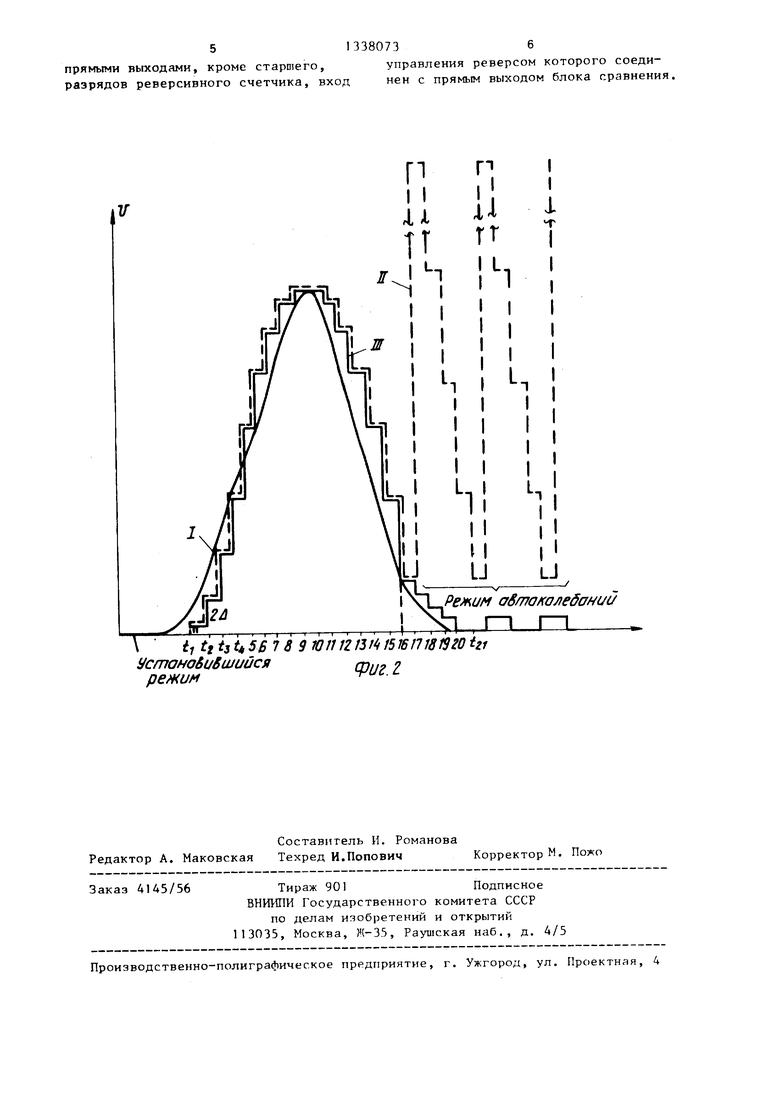

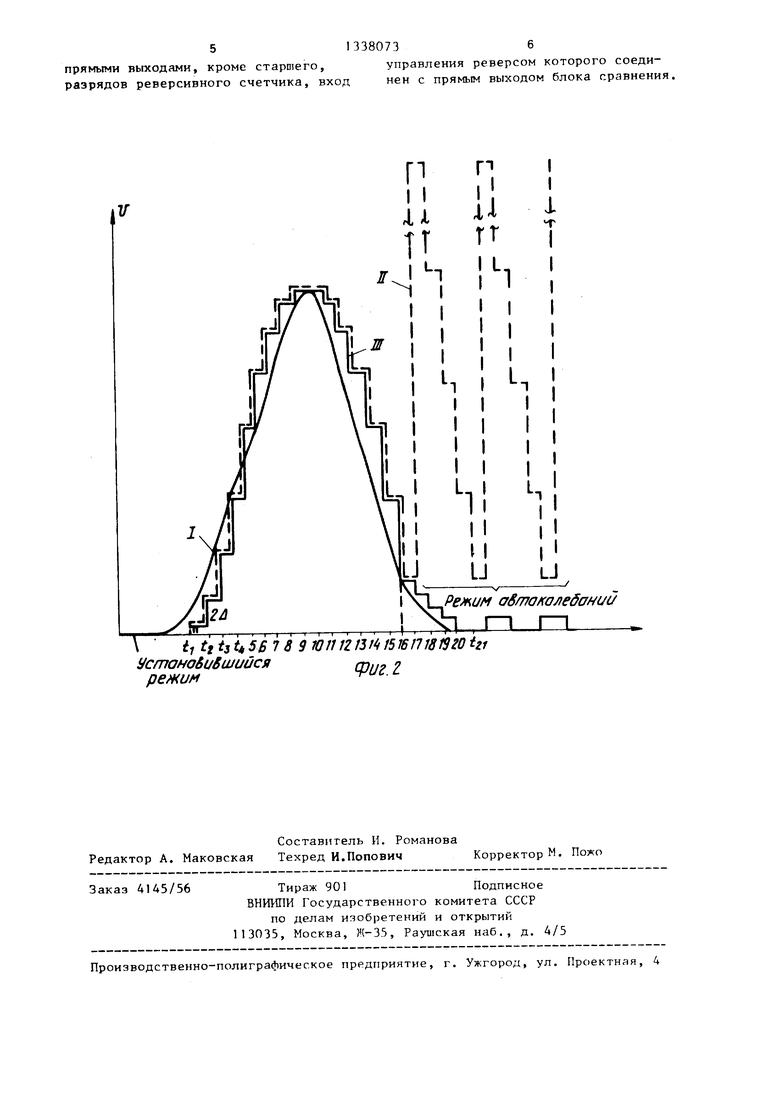

Яа фиг.1 приведена блок-схема следящего аналсго-пифровог С) преобразователя ; на фиг..

временные диаграммы,

поясняюгше работу устройства.

Следяишй ана юго-пифрсвой преобразователь содержит цифровой сумматор 1, регистр 2 памяти, цифроаналоговый преобразователь 3, блок 4 сравнения, генератор т тактовых импульсов, второй -элемент И 6, реверс:ивный счетчик 7, первый элемент ИЛИ-НК 8, четвертый элемент И 9, второй элемент И 10, вторс й элемент ИЛИ-НЕ 1 , первый элемент И 12.

Преобразователь работает следующим образом.

В исходном состоянии регистр 2 памяти и реверсивный счетчик 7 находятся в нулевом состоянии (схема установки в О на фиг.1 не показана).

На вход устройства поступает импульс- зо писанным в регистре 2 памяти, и за-

ный сигнал I j,. (t) (фи1 .2, линия I). При помоп и генератора 5 задается щаг дискретизации аналого-цифрового преобразования по времени. Как только уровень Р ходного сигнала достигает уровня срабатывания блока 4 сравнения, на его выходе формируется сигнал уровнялогической 1, который постуцает на вход управ.ления работой реверсив 1ого счетчика 7 . Значение сигнала на выходе блока 4 сравнения опреде.ляет ь:аправление счета в реверсивном счетчике 7. С приходом тактового 1гмпульса, вырабатываемого генеpaTOptiM 5, на тактовый вход реверсив- ний до тех пор, пока соотношение

ного счетчика 7 через обычно открытый элемент И 6 в реверсивном счетчике 7 производится суммирование или вычита :ие импульсов. Причем если вы- сигнал блока 4 сравнения равен 1, то производится операция , сумьшрования, еспи О, то - операция вы-читания. Так, если в момент времени t на выходе блока 4 сравнения сформировался сиг нал уровня логической 1, то в реверсивный счетчик 7 импульсов по переднему фронту так- товог(5 имп льса записывается единица , на выходе которог о формируется

и, (t) и

Вых и.ДП

не изменится. П

50

55

изменении данного соотношения на ходе блока 4 сравнения формируетс сигнал уровня логического О, и версивный счетчик 7 переключается режим вычитания, элемент И 6 откр ется, и с приходом тактового импу са код приращений уменьшается на ницу (фиг.2, линия III, момент вр ни 14).

Временные диаграммы, цриведенн на фиг.2 (I и III), полностью опи вают данный процесс. Интерес вызы ют момент времени t и последующ

код приращений и егч) знак. В данном случае код приращений имеет вид 0001, старший разряд которого определяет знак кода прираще1П1Й, предназначенный для осуществления операций суммирования и вычитания цифровым сумматором 1 . Если в разряде кода ирираишний записан О, то в цифровом сумматоре 1 производится операция суммирования, если 1, то - операция вычитания. В момент времени t производится операция суммирования кода приращений 0001 с кодом

00000000, записанным в этот момент в регистре 2 памяти, и запись полученного в результате суммирования кода 00000001 в регистр 2 памяти по заднему фронту тактового импульса. В момент времени t на выходе блока сравнения также формируется сигнал уровня логической 1, так как Ug (t) Mi U.AP реверсивный счетчик 7 добавляется еще один импульс, и код приращений имеет вид 0010. Так как в старшем разряде записан О, то при помощи пифрового сумматора 1 производится суммирование кода приращений 0010 с кодом 000000001, за5

пись полученного в результате суммирования кода 00000011 в регистр 2 памяти. В дальнейшем при неизменном соотношении условия ) цлп происходит увеличение кода црираще- на одну единицу. Как только код приращений будет иметь вид 0111, элемент И 6 запирается, тем самым пре- кpaD aeтcя поступление тактовых им- 0 пульсов на вход реверсивного счетчика 7. Код приращений остается неизменным, и в дальнейщем код, записанный в регистр 2 памяти, будет суммироваться с постоянным кодом приращений до тех пор, пока соотношение

и, (t) и

Вых и.ДП

не изменится. При

0

5

изменении данного соотношения на выходе блока 4 сравнения формируется сигнал уровня логического О, и реверсивный счетчик 7 переключается в режим вычитания, элемент И 6 открывается, и с приходом тактового импульса код приращений уменьшается на единицу (фиг.2, линия III, момент времени 14).

Временные диаграммы, цриведенные на фиг.2 (I и III), полностью описывают данный процесс. Интерес вызывают момент времени t и последующие.

в момент Bpt MeiiH t элемент ИПИНЕ 11 српбать вает, так КсЭК на его входах присутствует нулевая комбинация, реверс ивный счетчик 7 обнуляется, ив дал1)Не1И11ем производится вычитание из кода регистра 2 памяти по одной единице.

На основании алгоритма работы следяпщх аналого-цисЪровых преобразо- вателей (АИП) цифровой сумматор 1 должен обеспечивать как суммирование кодов, так и их вычитание. При этом операция суммирования производится при помощи прямого, а операция вычи- тания - при помопги дополнительного кодов . Прямой и дополнительный коды могут быть получены автоматически при помопда реверсивного счетчика 7, старший разряд которого определяет знак приращения. Если старший разряд реверсивного счетчика 7 равен О, то цифровой сумматор 1. должен осуществлять операцию сложения, если 1, то - операцию вычитания. Это дости- гается путем объединения пяти старших разрядов цифрового сумматора 1 и подключе}1ия их к старшему разряду реверсивного гчетчика 7.

При цреобразонлнии импульсных воз действий в с . К дяигей системе, как правило, возникае I режим автоколебаний по окончании импульсного воздействия Данный режим возникает вследствие того, что выходной код приращений ре-,

версивного счетчика 7 за один цикл преобразования не может измениться более или менее чем на единицу. Для предотвращения возникновения режима автоколебаний в устройстве можно выделить два функциональных узла, предназначенных для выделения запрещенных комбинаций. Первый функциональный узел реализован на двух элементах И 10 и 12 и элементе ИЛИ-ПЕ 13 и предназначен для выделения кодовых комбинаций 0111 (элемент И 10), 1000 (элемент И 12), поступаю- с выхода реверсивного счетчика 7. Второй функциональный узел реализован при помощи элемента И 9 и первого элемента ИЛИ-НЕ 8 и предназначен для выделения кодовой комбинации .ОООООХХХ , где X - безразличное состояние О Или 1. Данная ко- довая комбинация, сформированная на выходе регистра 2 памяти, выделяется в момент времени, когда в стартам разряде реверсивного счетчика 7 запи

338073

сана едишша, Такое состояние регистра 2 памяти и реверсивного счетчика 7 возможны при отслежива:п11 следяпгим АПП за задним фронтог( импульсного воздействия при его приближении к нулевому уровню.

IQ ,„ 25

-Q

тс

Q

0

5

о р м у л а изобретения

Следящий аналого-цифровой преобразователь, содержаг1ий последовательно соединенные цифровой сумматор, регистр памяти, цифроаналоговый преоб- раз.ователь, блок сравнения, второй вход которого является входной щиной, генератор тактовых импульсов, выходы регистра памяти соединены с соответствующими первым входами цифрового сумматора, отличающийся тем, что, с целью повьш ения точности преобразования путем предотвращения возникновения режима автоколебаний, введены четыре элемента И, два элемента ИЛИ-НЕ и реверсивный счетчик, прямой выход старщего разряда и инверсные выходы остальных разрядов которого и инверсный выход блока сравнения соединены с соответств тощими входами первого элемента I, инверсный вход старшего разряда и пр/:мые выходи остальных разрядов реверсивного счетчика и прямой блока сравнения соединены с соответствую- пгими входами второго элемента И, выход которого и выход первого элемента И соединены соответственно с первым и вторым входами первого элемента ИЛИ-НЕ, выход которого соединен с первым входом третьего элемента И, второй вход которого объединен с тактовым входом регистра памяти и соединен с выходом 1 енератора тактовых импульсов, а выход - с тактовым входом реверсивного счетчика, установочный вход которого соединен с выходом второго элемента ИЛИ-НЕ, первые входы которого соединены с соответствующими выходами регистра памяти, а второй и третий входы соединены соответственно с выходом четвертого элемента И и инверсным выходом старшего разряда реверсивного счетчика, прямой выход старшего разряда которого соединен с соответствующими вторыми входами цифрового сумматора, третьи входы которого объединены с соответствующими входами четвертого элемента И и соединены с соответствующими

513380736

прямыми выходами, кроме старшего, управления реверсом которого соеди- разрядов реверсивного счетчика, вход иен с прямым выходом блока сравнения,

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД | 2013 |

|

RU2534971C1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1988 |

|

SU1589383A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

| Устройство для отображенияиНфОРМАции | 1976 |

|

SU798961A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА | 1996 |

|

RU2115229C1 |

| Устройство для воспроизведения переменных во времени коэффициентов | 1981 |

|

SU1005087A1 |

| МНОГОМЕРНЫЙ СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР УСРЕДНЕННОЙ МОЩНОСТИ НЕСТАЦИОНАРНОЙ НАГРУЗКИ | 1992 |

|

RU2060542C1 |

| Вычислительное устройство | 1982 |

|

SU1040493A1 |

| Устройство программного управления | 1984 |

|

SU1246055A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для преобразования быстроизменяющихся аналоговых сигналов в цифровой код. Целью изобретения является повышение точности путем предотвращения возникновения режима автоколебаний. Цель достигается за счет того, что в известное устройство, содержащее цифровой сумматор I, регистр 2 памяти, цифро- аналоговый преобразователь 3, блок 4 сравнения, генератор 5 тактовых импульсов, реверсивный счетчик 7, введены четьфе элемента И и два элемента ИЛИ-НЕ. 2 ил. а & (Л иЛж. 00 оо 00 о со фиг

V

ii tt tj и 5БТ S 9 ЮН 12 /J/415761718 IS 10 izi

УстонобиКшийсяm,iy 7

режим -

I

11

гг

Т

I

1 I

I LJ

и

автоколебаний

Составитель И. Романова Редактор А. Маковская Техред И.Попович Корректор М. Пожо

Заказ 4145/56

Тираж 901Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Следящий аналого-цифровой преобразователь | 1975 |

|

SU546099A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразование информации в аналого-цифровых вычислительных устройствах и системах | |||

| М.: Машиностроение, с | |||

| Гудок | 1921 |

|

SU255A1 |

| Облицовка комнатных печей | 1918 |

|

SU100A1 |

Авторы

Даты

1987-09-15—Публикация

1985-10-02—Подача