QS

ч ел

00

N о

информационные входы которых с выходов регистров 2 и 3 поступают значения N младших разрядов координатных приращений X и Y соответственно. На информационные входы блоков 20 и 21 выравнивания поступают значения сформированных 2M N-pas- рядных приращений, а с их выходов,

соответствующих ведущей и ведомой координатам, эти значения считываются внешним устройством. Интерполяция заданного отрезка прямой осуществляется за 2N+1 интерполяционных тактов. Блок 1 управления осуществляет синхронизацию работы интерполятора. 2 з.п. ф-лы, 4 ил. 1 табл.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой линейный интерполятор | 1987 |

|

SU1434406A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1631518A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1693592A1 |

| Цифровой линейный интерполятор | 1986 |

|

SU1310779A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Круговой интерполятор | 1985 |

|

SU1359772A1 |

| Линейно-круговой интерполятор | 1984 |

|

SU1215090A2 |

| Цифровой линейный интерполятор | 1988 |

|

SU1624406A1 |

| Линейный интерполятор | 1986 |

|

SU1423984A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1674061A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в выводных графических устройствах с линейными и матричными органами регистрации, в станках с программным управлением, в которых использованы линейные и матричные исполнительные органы. Цель изобретения - уменьшение погрешности аппроксимации интерполятора, Цифровой линейный интерполятор обеспечивает нахождение многоразрядных приращений, которыми аппроксимирован заданный отрезок прямой, за один интерполяционный такт, а затем пропускание сформированных многоразрядных приращений через блок выравнивания, вследствие чего уменьшается неравномерность распределения единичных импульсов в указанных группах. За счет этого погрешность аппроксимации уменьшается в два раза. Значение N младших разрядов М-разрядных координатных приращений запоминаются в регистрах 2 и 3. M-N старших разрядов координатных приращений поступают на адресные входы блока 4 постоянной памяти, с выходов которого 2 N-1 разрядов приращений записываются в регистры 9 и 10. Младший разряд 2м м-разрядных приращений формируется N-разрядны- ми двоичными умножителями 5 и 6, на сл С

Изобретение относится к автоматике и вычислительной технике и может быть использовано в выводных графических устройствах с линейными и матричными органами регистрации, в станках с программным управлением, в которых использованы линейные и матричные исполнительные органы.

Цель изобретения - уменьшение погрешности аппроксимации интерполятора.

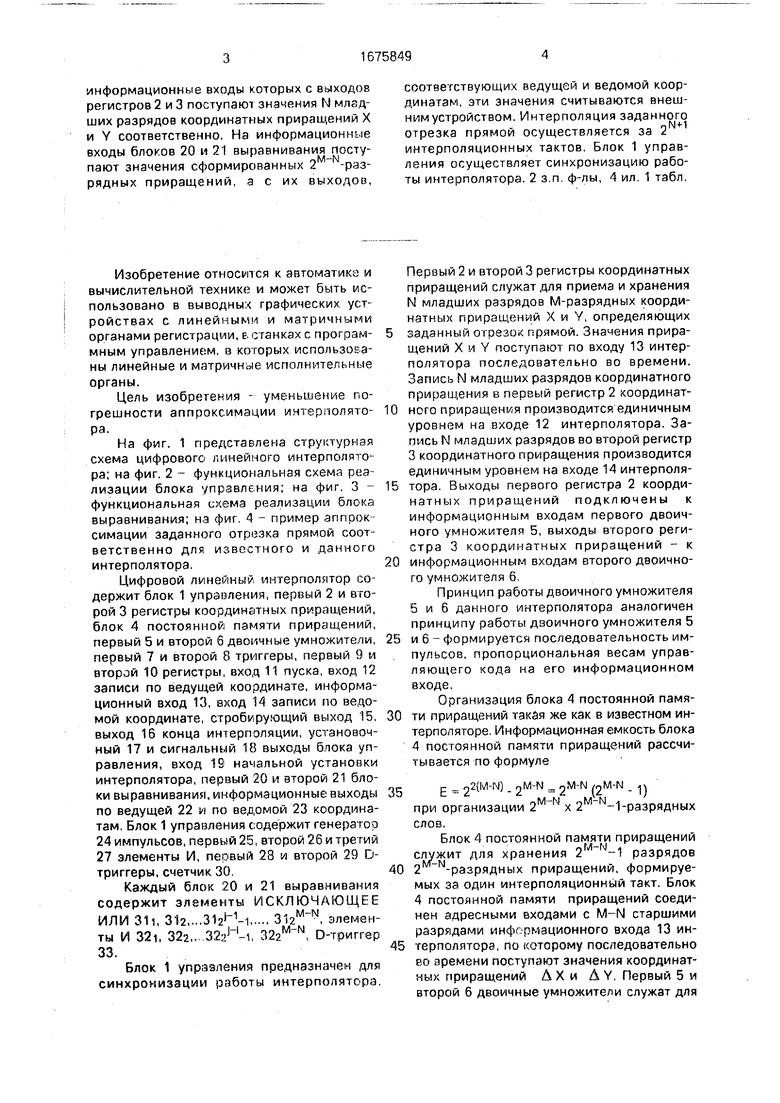

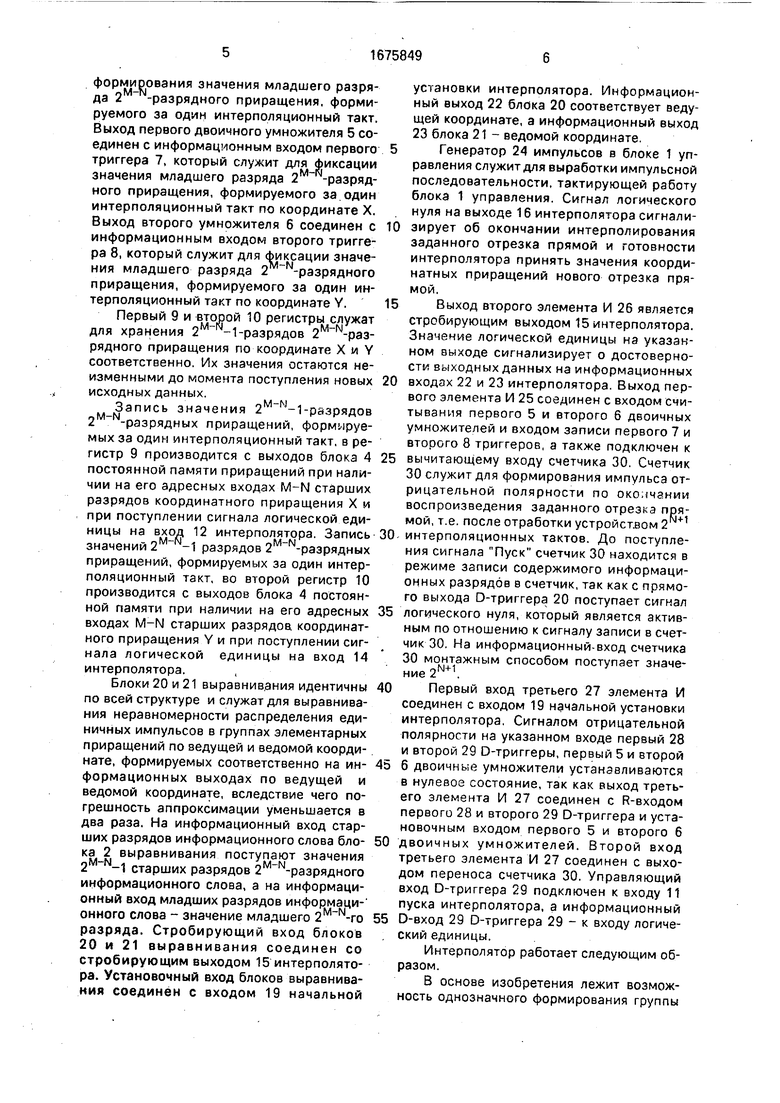

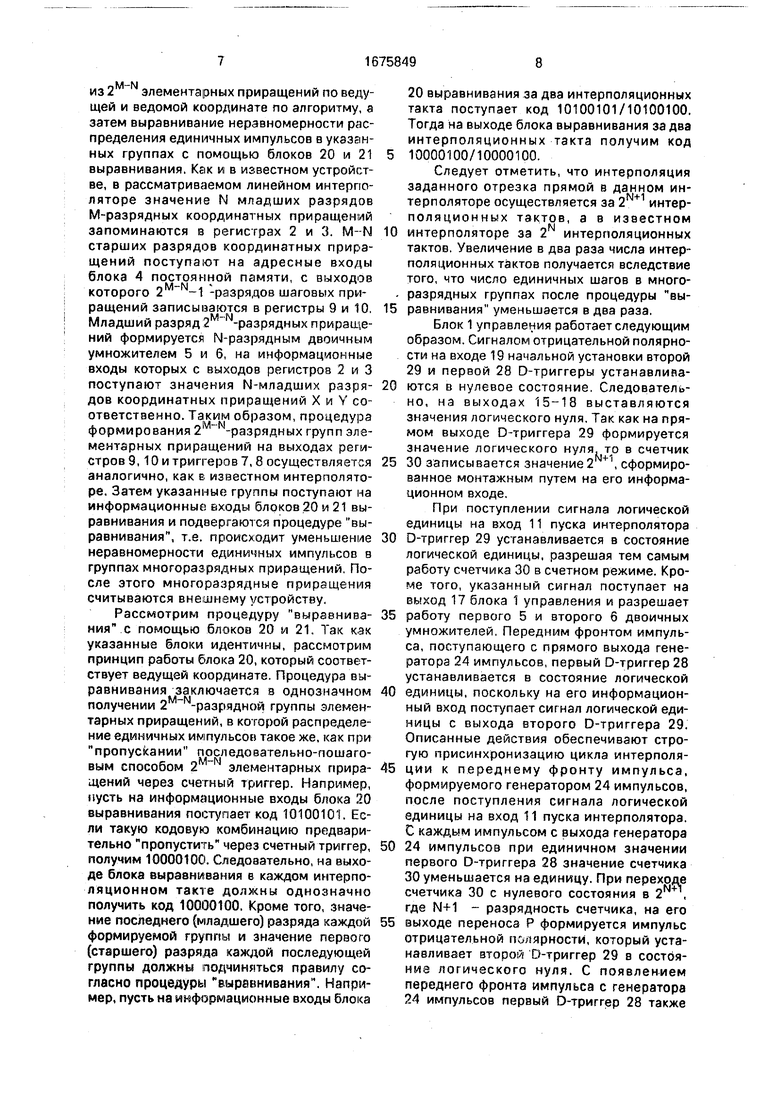

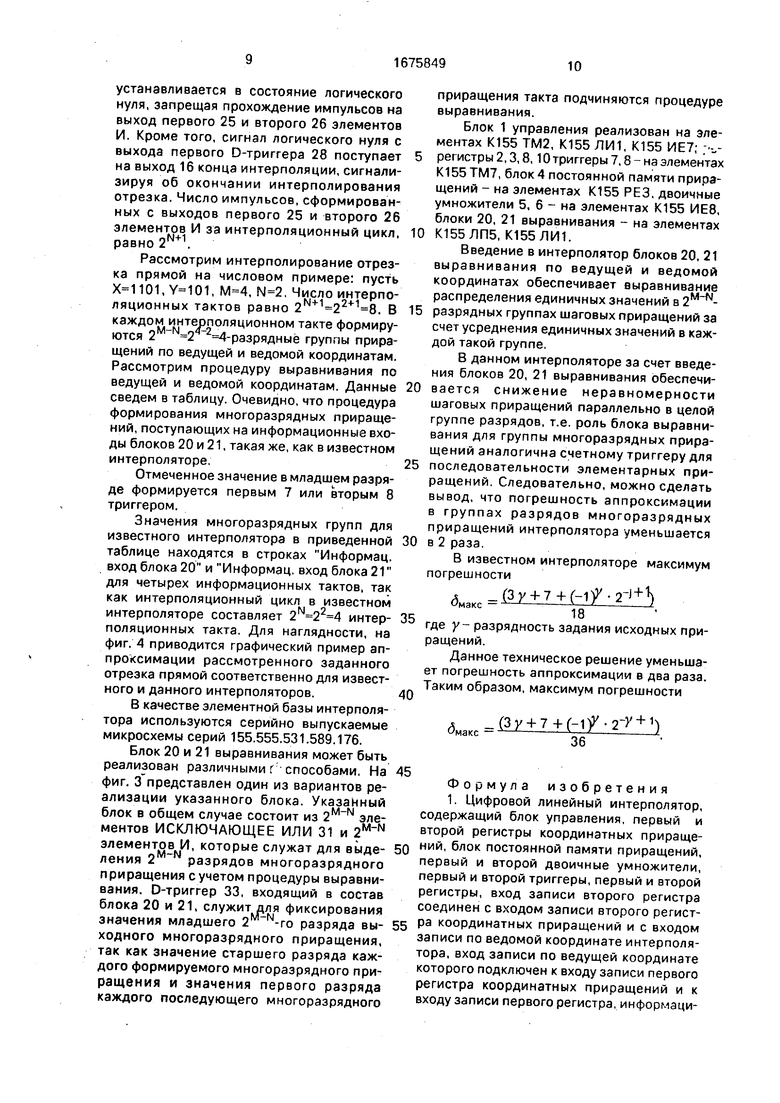

На фиг. 1 представлена структурная схема цифрового линейного интерполятора; на фиг. 2 - функциональная схема реализации блока управления; на фиг, 3 - функциональная схема реализации блока выравнивания; на фиг. 4 - пример аппроксимации заданного отрезка прямой соответственно для известного и данного интерполятора.

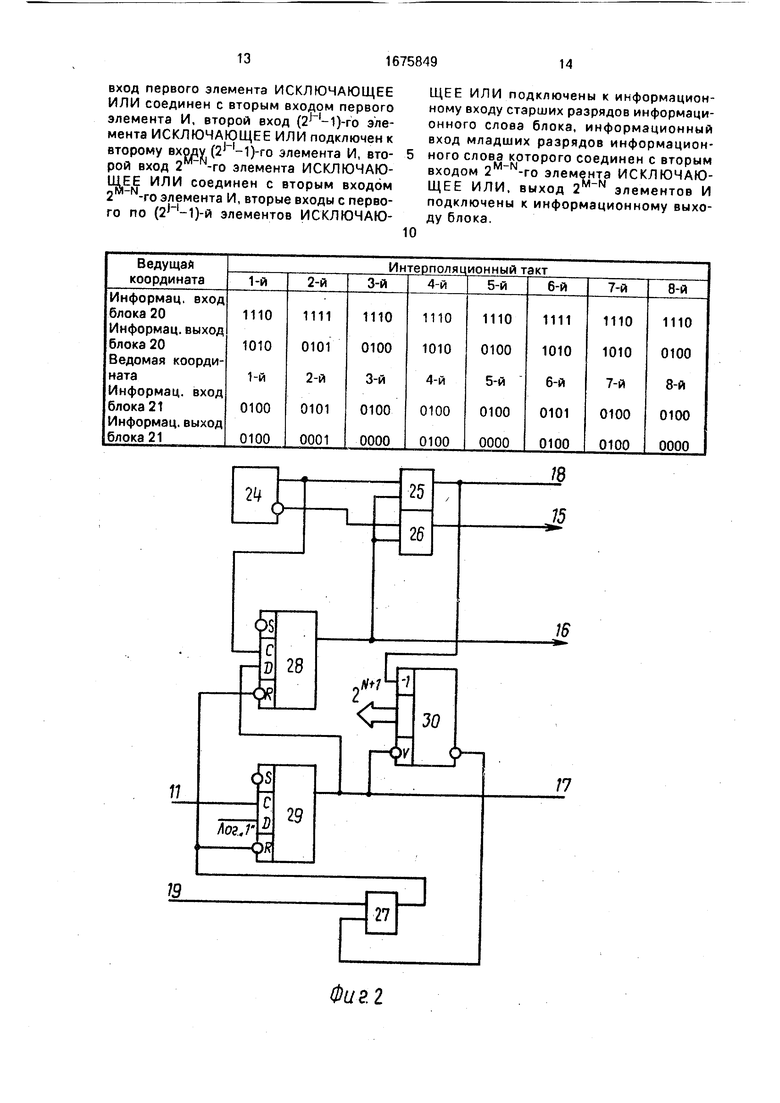

Цифровой линейный интерполятор содержит блок 1 управления, первый 2 и второй 3 регистры координатных приращений, блок 4 постоянной памяти приращений, первый 5 и второй 6 двоичные умножители, первый 7 и второй 8 триггеры, первый 9 и второй 10 регистры, вход 11 пуска, вход 12 записи по ведущей координате, информационный вход 13, вход 14 записи по ведомой координате, стробирующий выход 15, выход 16 конца интерполяции, установочный 17 и сигнальный 18 выходы блока управления, вход 19 начальной установки интерполятора, первый 20 и второй 21 блоки выравнивания, информационные выходы по ведущей 22 и по ведомой 23 координатам. Блок 1 управления содержит генератор 24 импульсов, первый 25, второй 26 и третий 27 элементы И, первый 28 и второй 29 D- триггеры, счетчик 30.

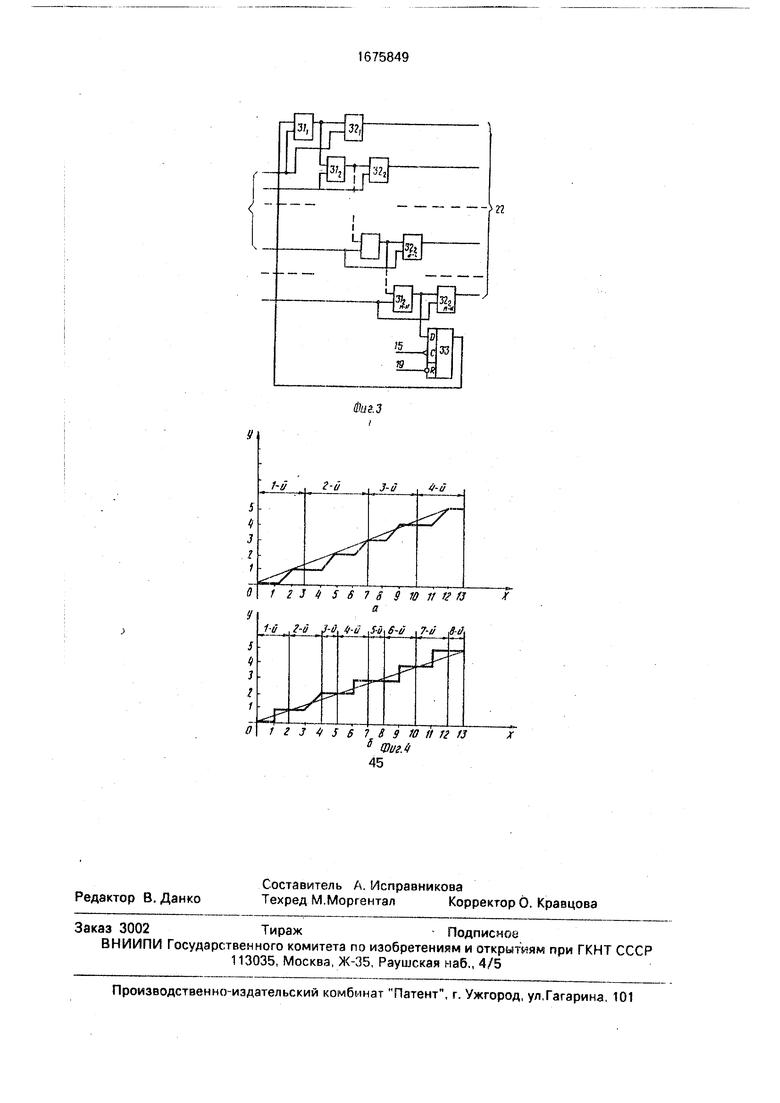

Каждый блок 20 и 21 выравнивания содержит элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 31i, 312,...312H-1312M N, элементы И 32i, 322,...322H-i, , D-триггер 33.

Блок 1 управления предназначен для синхронизации работы интерполятора.

Первый 2 и второй 3 регистры координатных приращений служат для приема и хранения N младших разрядов М-разрядных координатных приращений X и Y, определяющих

заданный отрезок прямой. Значения приращений X и Y поступают по входу 13 интерполятора последовательно во времени. Запись N младших разрядов координатного приращения в первый регистр 2 координатного приращения производится единичным уровнем на входе 12 интерполятора. Запись N младших разрядов во второй регистр

3координатного приращения производится единичным уровнем на входе 14 интерполятора. Выходы первого регистра 2 координатных приращений подключены к информационным входам первого двоичного умножителя 5, выходы второго регистра 3 координатных приращений - к

информационным входам второго двоичного умножителя 6.

Принцип работы двоичного умножителя 5 и 6 данного интерполятора аналогичен принципу работы двоичного умножителя 5

и 6 - формируется последовательность импульсов, пропорциональная весам управляющего кода на его информационном входе.

Организация блока 4 постоянной памяти приращений такая же как в известном интерполяторе. Информационная емкость блока

4постоянной памяти приращений рассчитывается по формуле

Е - ( -1)

при организации x 2м м-1-разрядных слов.

Блок 4 постоянной памяти приращений служит для хранения разрядов

2 м-разрядных приращений, формируемых за один интерполяционный такт. Блок 4 постоянной памяти приращений соединен адресными входами с M-N старшими разрядами информационного входа 13 интерполятора, по которому последовательно во времени поступают значения координатных приращений Д X и Л Y. Первый 5 и второй 6 двоичные умножители служат для

формирования значения младшего разряда 2м -разрядного приращения, формируемого за один интерполяционный такт. Выход первого двоичного умножителя 5 соединен с информационным входом первого триггера 7, который служит для фиксации

л М-Гч

значения младшего разряда 2 -разрядного приращения, формируемого за один интерполяционный такт по координате X. Выход второго умножителя б соединен с информационным входом второго триггера 8, который служит для Фиксации значения младшего разряда 2 -разрядного приращения, формируемого за один интерполяционный такт по координате Y.

Первый 9 и второй 10 регистры служат для хранения 2м -1-разрядов 2 -разрядного приращения по координате X м Y соответственно. Их значения остаются неизменными до момента поступления новых исходных данных.

Запись значения 2м м-1-разрядов 2м м-разрядных приращений, формируемых за один интерполяционный такт, в регистр 9 производится с выходов блока 4 постоянной памяти приращений при наличии на его адресных входах M-N старших разрядов координатного приращения X и при поступлении сигнала логической единицы на вход 12 интерполятора. Запись значений 2м -1 разрядов 2м м-разрядных приращений, формируемых за один интерполяционный такт, во второй регистр 10 производится с выходов блока 4 постоянной памяти при наличии на его адресных входах M-N старших разрядов координатного приращения Y и при поступлении сигнала логической единицы на вход 14 интерполятора.

Блоки 20 и 21 выравнивания идентичны по всей структуре и служат для выравнивания неравномерности распределения единичных импульсов в группах элементарных приращений по ведущей и ведомой координате, формируемых соответственно на ин- формационных выходах по ведущей и ведомой координате, вследствие чего погрешность аппроксимации уменьшается в два раза. На информационный вход старших разрядов информационного слова бло- ка 2 выравнивания поступают значения старших разрядов 2м м-разрядного информационного слова, а на информационный вход младших разрядов информационного слова - значение младшего разряда. Стробирующий вход блоков 20 и 21 выравнивания соединен со стробирующим выходом 15 интерполятора. Установочный вход блоков выравнивания соединен с входом 19 начальной

установки интерполятора. Информационный выход 22 блока 20 соответствует ведущей координате, а информационный выход 23 блока 21 - ведомой координате.

Генератор 24 импульсов в блоке 1 управления служит для выработки импульсной последовательности, тактирующей работу блока 1 управления. Сигнал логического нуля на выходе 16 интерполятора сигнализирует об окончании интерполирования заданного отрезка прямой и готовности интерполятора принять значения координатных приращений нового отрезка прямой.

Выход второго элемента И 26 является стробирующим выходом 15 интерполятора. Значение логической единицы на указанном выходе сигнализирует о достоверности выходных данных на информационных входах 22 и 23 интерполятора. Выход первого элемента И 25 соединен с входом считывания первого 5 и второго 6 двоичных умножителей и входом записи первого 7 и второго 8 триггеров, а также подключен к вычитающему входу счетчика 30. Счетчик 30 служит для формирования импульса отрицательной полярности по окончании воспроизведения заданного отрезка прямой, т.е. после отработки устройством 2 интерполяционных тактов. До поступления сигнала Пуск счетчик 30 находится в режиме записи содержимого информационных разрядов в счетчик, так как с прямого выхода D-триггера 20 поступает сигнал логического нуля, который является активным по отношению к сигналу записи в счетчик 30. На информационный-вход счетчика 30 монтажным способом поступает значе- ние2м+1.

Первый вход третьего 27 элемента И соединен с входом 19 начальной установки интерполятора. Сигналом отрицательной полярности на указанном входе первый 28 и второй 29 D-триггеры, первый 5 и второй 6 двоичные умножители устанавливаются в нулевое состояние, так как выход третьего элемента И 27 соединен с R-входом первого 28 и второго 29 D-триггера и установочным входом первого 5 и второго 6 двоичных умножителей. Второй вход третьего элемента И 27 соединен с выходом переноса счетчика 30. Управляющий вход D-триггера 29 подключен к входу 11 пуска интерполятора, а информационный D-вход 29 D-триггера 29 - к входу логический единицы.

Интерполятор работает следующим образом.

В основе изобретения лежит возможность однозначного формирования группы

из 2м N элементарных приращений по ведущей и ведомой координате по алгоритму, а затем выравнивание неравномерности распределения единичных импульсов в указанных группах с помощью блоков 20 и 21 выравнивания. Как и в известном устройстве, в рассматриваемом линейном интерполяторе значение N младших разрядов М-разрядных координатных приращений запоминаются в регистрах 2 и 3. M-N старших разрядов координатных приращений поступают на адресные входы блока 4 постоянной памяти, с выходов

.

которого 2 -1 -разрядов шаговых приращений записываются в регистры 9 и 10. Младший разряд 2м м-разрядных приращений формируется N-разрядным двоичным умножителем 5 и б, на информационные входы которых с выходов регистров 2 и 3 поступают значения N-младших разрядов координатных приращений X и Y соответственно. Таким образом, процедура формирования 2м м-разрядных групп элементарных приращений на выходах регистров 9,10 и триггеров 7, 8 осуществляется аналогично,как в известном интерполяторе. Затем указанные группы поступают на информационные входы блоков 20 и 21 выравнивания и подвергаются процедуре выравнивания, т.е. происходит уменьшение неравномерности единичных импульсов в группах многоразрядных приращений. После этого многоразрядные приращения считываются внешнему устройству.

Рассмотрим процедуру выравнивания с помощью блоков 20 л 21. Так как указанные блоки идентичны, рассмотрим принцип работы блока 20, который соответствует ведущей координате. Процедура выравнивания заключается в однозначном получении 2м -разрядной группы элементарных приращений, в которой распределение единичных импульсов такое же, как при пропускании последовательно-пошаговым способом 2 элементарных приращений через счетный триггер. Например, пусть на информационные входы блока 20 выравнивания поступает код 10100101. Если такую кодовую комбинацию предварительно пропустить через счетный триггер, получим 10000100. Следовательно, на выходе блока выравнивания в каждом интерполяционном такте должны однозначно получить код 10000100. Кроме того, значение последнего (младшего) разряда каждой формируемой группы и значение первого (старшего) разряда каждой последующей группы должны подчиняться правилу согласно процедуры выравнивания. Например, пусть на информационные входы блока

20 выравнивания за два интерполяционных такта поступает код 10100101/10100100. Тогда на выходе блока выравнивания за два интерполяционных такта получим код

10000100/10000100.

Следует отметить, что интерполяция заданного отрезка прямой в данном интерполяторе осуществляется за 2N+1 интер- поляционных тактов, а в известном

0 интерполяторе за 2 интерполяционных тактов. Увеличение в два раза числа интерполяционных тактов получается вследствие того, что число единичных шагов в много- - разрядных группах после процедуры вы5 равнивания уменьшается в два раза.

Блок 1 управления работает следующим образом. Сигналом отрицательной полярности на входе 19 начальной установки второй

29и первой 28 D-триггеры устанавлива- 0 ются в нулевое состояние. Следовательно, на выходах 15-18 выставляются значения логического нуля. Так как на прямом выходе D-триггера 29 формируется значение логического нуля, то в счетчик

5 30 записывается значение 2 , сформированное монтажным путем на его информационном входе.

При поступлении сигнала логической единицы на вход 11 пуска интерполятора

0 D-триггер 29 устанавливается в состояние логической единицы, разрешая тем самым работу счетчика 30 в счетном режиме. Кроме того, указанный сигнал поступает на выход 17 блока 1 управления и разрешает

5 работу первого 5 и второго б двоичных умножителей. Передним фронтом импульса, поступающего с прямого выхода генератора 24 импульсов, первый D-триггер 28 устанавливается в состояние логической

0 единицы, поскольку на его информационный вход поступает сигнал логической единицы с выхода второго D-триггера 29. Описанные действия обеспечивают строгую присинхронизацию цикла интерполя5 ции к переднему фронту импульса, формируемого генератором 24 импульсов, после поступления сигнала логической единицы на вход 11 пуска интерполятора. С каждым импульсом с выхода генератора

0 24 импульсов при единичном значении первого D-триггера 28 значение счетчика

30уменьшается на единицу. При переходе счетчика 30 с нулевого состояния в 2 , где N+1 - разрядность счетчика, на его

5 выходе переноса Р формируется импульс отрицательной полярности, который устанавливает второй D-триггер 29 в состояние логического нуля, С появлением переднего фронта импульса с генератора 24 импульсов первый D-триггер 28 также

устанавливается в состояние логического нуля, запрещая прохождение импульсов на выход первого 25 и второго 26 элементов И. Кроме того, сигнал логического нуля с выхода первого D-триггера 28 поступает на выход 16 конца интерполяции, сигнализируя об окончании интерполирования отрезка. Число импульсов, сформированных с выходов первого 25 и второго 26 элементов И за интерполяционный цикл, равно 2N+1.

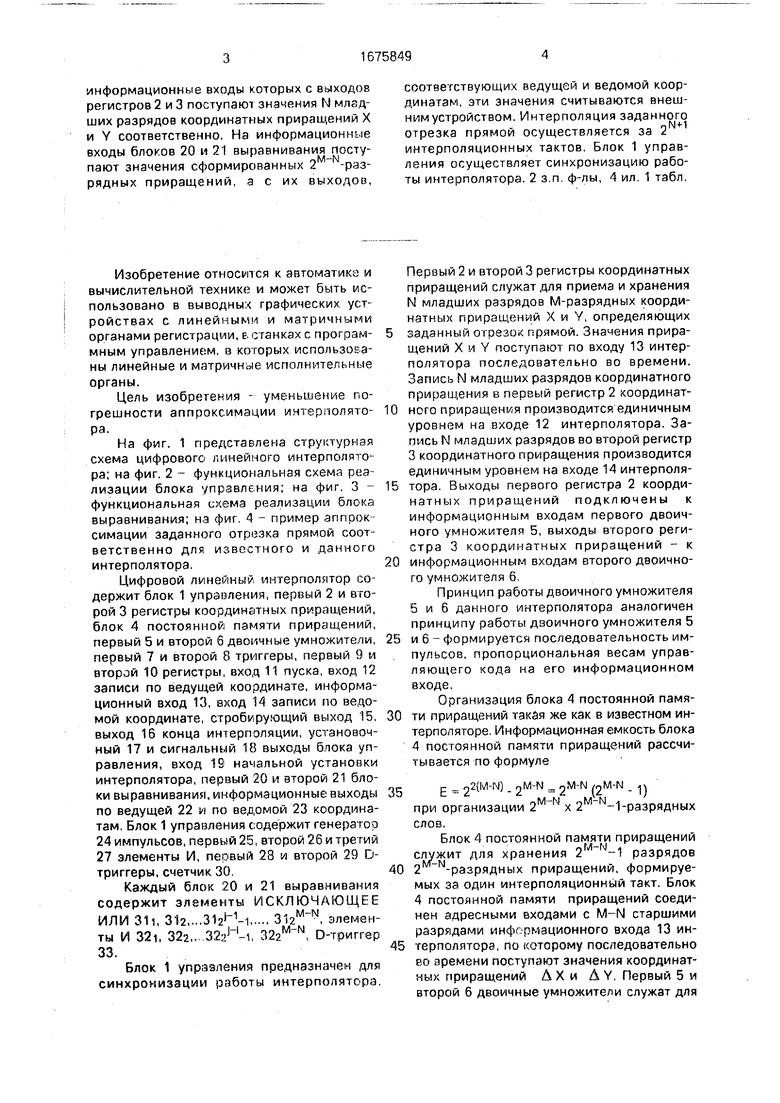

Рассмотрим интерполирование отрезка прямой на числовом примере: пусть , , , . Число интерполяционных тактов равно 2 8. В каждом интерполяционном такте формируются 4-разрядные группы приращений по ведущей и ведомой координатам. Рассмотрим процедуру выравнивания по ведущей и ведомой координатам. Данные сведем в таблицу. Очевидно, что процедура формирования многоразрядных приращений, поступающих на информационные входы блоков 20 и 21, такая же, как в известном интерполяторе.

Отмеченное значение в младшем разряде формируется первым 7 или вторым 8 триггером.

Значения многоразрядных групп для известного интерполятора в приведенной таблице находятся в строках Информац. вход блока 20 и Информац. вход блока 21 для четырех информационных тактов, так как интерполяционный цикл в известном интерполяторе составляет интерполяционных такта. Для наглядности, на фиг. 4 приводится графический пример аппроксимации рассмотренного заданного отрезка прямой соответственно для известного и данного интерполяторов.

В качестве элементной базы интерполятора используются серийно выпускаемые микросхемы серий 155.555.531.589.176.

Блок 20 и 21 выравнивания может быть реализован различными г способами, На фиг. З представлен один из вариантов реализации указанного блока. Указанный блок в общем случае состоит из 2Л ментов ИСКЛЮЧАЮЩЕЕ ИЛИ 31 и 2 элементов И, которые служат для выделения разрядов многоразрядного приращения с учетом процедуры выравнивания. D-триггер 33, входящий в состав блока 20 и 21, служит для фиксирования значения младшего 2 N-ro разряда выходного многоразрядного приращения, так как значение старшего разряда каждого формируемого многоразрядного приращения и значения первого разряда каждого последующего многоразрядного

эле,M-N

приращения такта подчиняются процедуре выравнивания.

Блок 1 управления реализован на элементах К155 ТМ2, К155 ЛИ1, К155 ИЕ7; ;-„регистры 2,3,8,10 триггеры 7,8-на элементах К155ТМ7, блок 4 постоянной памяти приращений - на элементах К155 РЕЗ, двоичные умножители 5, 6 - на элементах К155 ИЕ8, блоки 20, 21 выравнивания - на элементах

К155ЛП5, К155ЛИ1.

Введение в интерполятор блоков 20, 21 выравнивания по ведущей и ведомой координатах обеспечивает выравнивание распределения единичных значений в 2M-Nразрядных группах шаговых приращений за счет усреднения единичных значений в каждой такой группе.

В данном интерполяторе за счет введения блоков 20, 21 выравнивания обеспечивается снижение неравномерности шаговых приращений параллельно в целой группе разрядов, т.е. роль блока выравнивания для группы многоразрядных приращений аналогична счетному триггеру для

последовательности элементарных приращений. Следовательно, можно сделать вывод, что погрешность аппроксимации в группах разрядов многоразрядных приращений интерполятора уменьшается

в 2 раза.

В известном интерполяторе максимум погрешности

(Зу + 7+НУ-2 J + t)

18

где у- разрядность задания исходных приращений.

Данное техническое решение уменьшает погрешность аппроксимации в два раза. Таким образом, максимум погрешности

макс

Омакс -

(3y + l +(-rf + 1) 36

45

Формула изобретения 1. Цифровой линейный интерполятор, содержащий блок управления, первый и второй регистры координатных прираще5Q ний, блок постоянной памяти приращений, первый и второй двоичные умножители, первый и второй триггеры, первый и второй регистры, вход записи второго регистра соединен с входом записи второго регист55 pa координатных приращений и с входом записи по ведомой координате интерполятора, вход записи по ведущей координате которого подключен к входу записи первого регистра координатных приращений и к входу записи первого регистра, информационный вход которого соединен с информационным входом второго регистра и с выходом блока постоянной памяти приращений, адресные входы которого подключены к M-N старшим разрядам информационного входа устройства, N младших разрядов информационного входа устройства соединены с информационными входами первого и второго регистров координатных приращений, информационный выход второго регистра координатных приращений соединен с информационным входом второго двоичного умножителя, информационный выход которого соединен с информационным входом второго триггера, вход записи которого соединен с входом записи первого триггера, сигнальным выходом блока управления и входом считывания первого и второго двоичного умножителя, установочный вход второго двоичного умножителя соединен с установочным выходом блока управления и установочным входом первого двоичного умножителя, информационный вход которого соединен с информационным выходом первого регистра координатного приращения, а информационный выход первого двоичного умножителя соединен с информационным входом первого триггера, стро- бирующий выход блока управления является стробирукщим выходом интерполятора, выход конца интерполяции блока управления является выходом конца интерполяции интерполятора, а вход пуска блока управления является входом пуска интерполятора, отличающийся тем, что, с целью уменьшения погрешности аппроксимации интерполятора, в него введены первый и второй блоки выравнивания, информационные входы старших разрядов информационного слова которых соединены с информационными выходами первого и второго регистров соответственно, информационные входы младших разрядов информационного слова первого и второго блоков выравнивания подключены к выходам первого и второго триггеров соответственно, вход начальной установки интерполятора соединен с входом начальной установки блока управления и установочными входами первого и второго блоков выравнивания, стробирующие входы которых соединены со стробирующим выходом блока управления, а информационные выходы первого и второго блоков выравнивания являются информационным выходом интерполятора по ведущей координате и информационным выходом интерполятора по ведомой координате соответственно.

входу третьего элемента И соответственно, установочный R-вход второго D-триггера соединен с выходом третьего элемента И и установочным R-входом первого D- триггера, информационный D-вход которого соединен с выходом второго D-триггера, установочным выходом блока управления и установочным входом счетчика, вычитающий вход которого соединен с сигнальным выходбм блока управления и

выходом первого элемента И, первый вход которого соединен с прямым выходом генератора импульсов и управляющим С- входом первого D-триггера, первый вход второго элемента И подключен к инверсному выходу генератора импульсов, выход первого D-триггера соединен с вторыми входами первого и второго элементов И и с выходом конца интерполяции блока управления, стробирующий выход которого подключей к выходу второго элемента И, информационный D-вход второго D-триггера соединен с шиной логической единицы, выход переноса счетчика подключен к второму входу третьего элемента И.

приращений, N-количество младших разрядов координатных приращений А X и A Y), D-триггер, управляющий С-вход и установочный R-вход которого являются.управляющим и установочным входами

блока соответственно, выход D-триггера соединен с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к первому входу второго элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ, выход которого соединен с первым входом второго элемента И и с первым входом (2н-1)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к первому входу (2JH-1)-ro элемента И (где

,..., М, N) и к первому входу

2м -го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с первым входом 2м -го элемента И и с информационным D-входом D-триггера, второй

вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с вторым входом первого элемента И, второй вход ()-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к второму входу (2 |-1}-го элемента И, второй вход 2м -го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с вторым входом 2 N-ro элемента И, вторые входы с первого по (2н-1)-й элементов ИСКЛЮЧАЮ

5

с

Лог.

29

г

Фиг 2

ЩЕЕ ИЛИ подключены к информационному входу старших разрядов информационного слова блока, информационный вход младших разрядов информационного слова которого соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход элементов И подключены к информационному выходу блока.

Ј77

з;.

JHU1

/-i -P-i 3-0 4-i/ 5-й 6-й 7-и №

о г г j 4 s б 7 8 9 w ft гг н 6 Фиг.4 45

33

| ЦИФРОВОЙ ЛИНЕЙНЫЙ ИНТЕРПОЛЯТОР | 0 |

|

SU344415A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Цифровой линейный интерполятор | 1987 |

|

SU1434406A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1991-09-07—Публикация

1989-05-03—Подача