(54) УМНОЖИТЕЛЬ ЧАСТОТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой умножитель частоты | 1983 |

|

SU1164857A1 |

| Умножитель частоты | 1979 |

|

SU834697A1 |

| Умножитель частоты | 1990 |

|

SU1797113A1 |

| Устройство для умножения частоты сигналов | 1974 |

|

SU528567A1 |

| УМНОЖИТЕЛЬ ЧАСТОТЫ | 1971 |

|

SU312373A1 |

| Устройство для управления процессом смешения жидкостей | 1986 |

|

SU1429092A1 |

| Следящий умножитель частоты | 1979 |

|

SU851406A1 |

| Цифровой электромагнитный толщиномер | 1988 |

|

SU1839228A1 |

| Умножитель частоты следования периодических импульсов | 1980 |

|

SU980094A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU991614A2 |

Изобретение относится .к цифровой измерительной технике.

Известный умножитель частоты с уравновешиванием, в котором в качест1ве элемента сравнения частотных сигналой применен реверсввный счетчи;к, -кроме него содержит также преобразователь «код-на пряжение, управляемый генератор и счетчик обратной озязи. Такой умножитель характеризуется широким диапазоном умножаемых частот и достаточ ю больши1м значением коэффициента умножения, однако отличается большой длительностью переходного процесса лри изменении входной частоты, а также малым диапазоном изменения его коэффициента умножения, что значительно ограничивает область его нрименения, особенно в диапазоне низких и ин фраН изких .

Цель изобретения -повышение быстродействия умножителя частоты и расширение диапазона его коэффициента умножения.

Это достигается тем, что умножитель содержит схемы И, одни входы которых соединены с выходами блока управления, другие-с выходом делителя частоты, а их выходы падключены соот1ветствен:но ко входу реBepiCHBHoro счетчика и к другО:Му входу второй схемы ИЛИ, наборное поле, вторую группу схем И и третью схему ИЛИ, выход которой соединен с выходом умножителя

частоты, а входы подключены к выходам схем «И второй группы, входами соединенных соответст вснно с выходами наборного поля г. прямыми выходалги разрядных тр}1ггеров счетчика обратной связи.

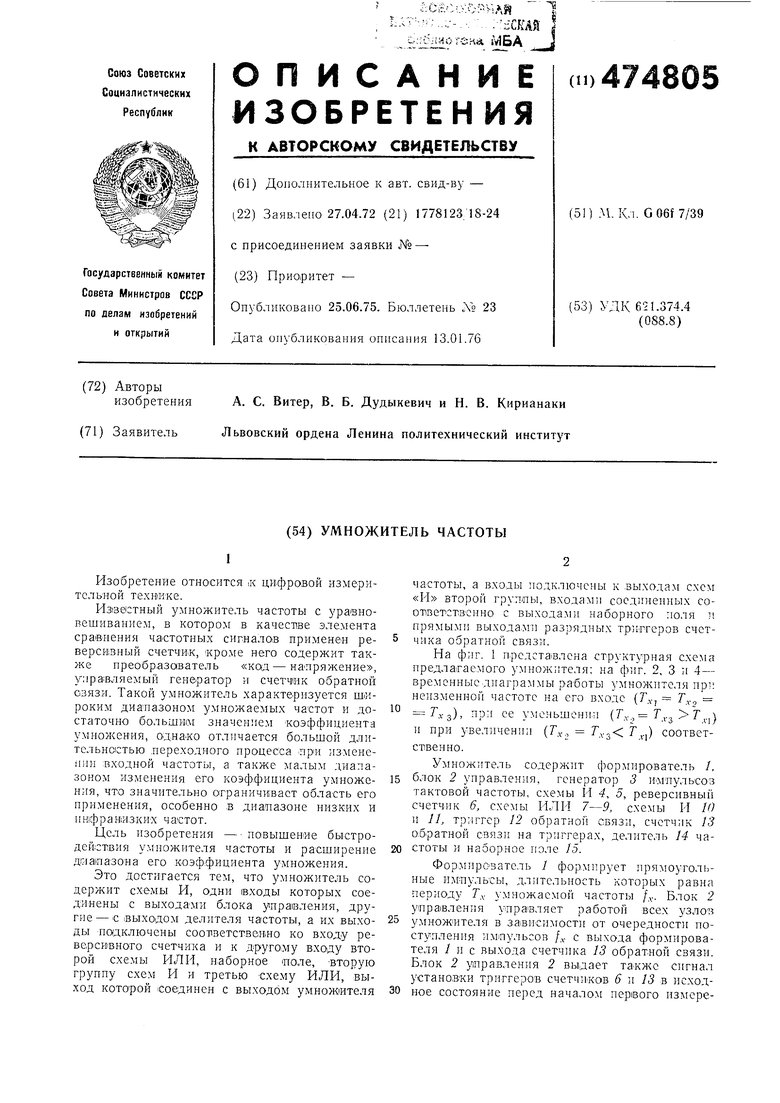

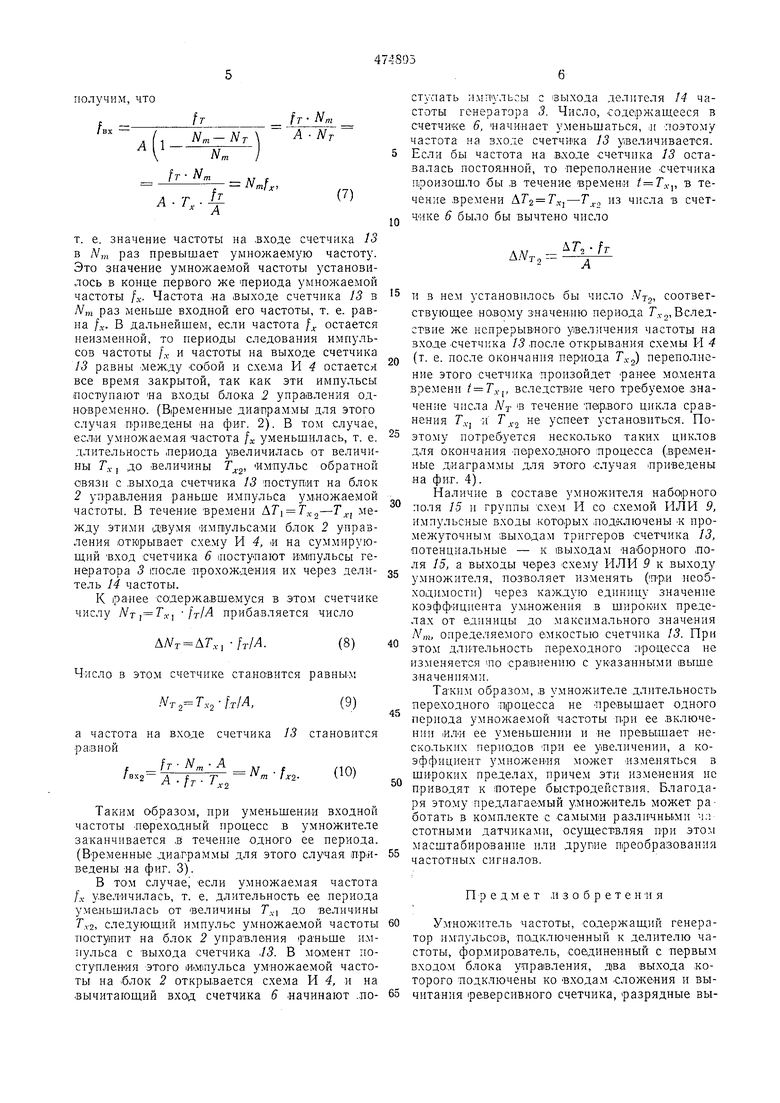

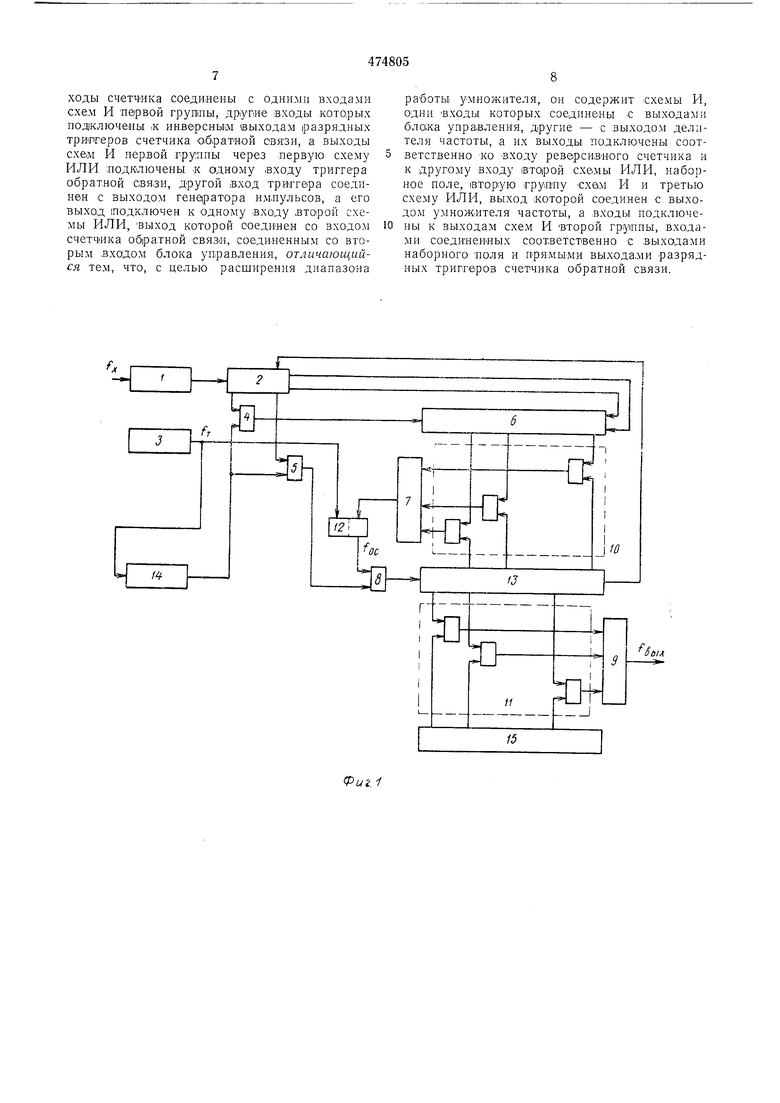

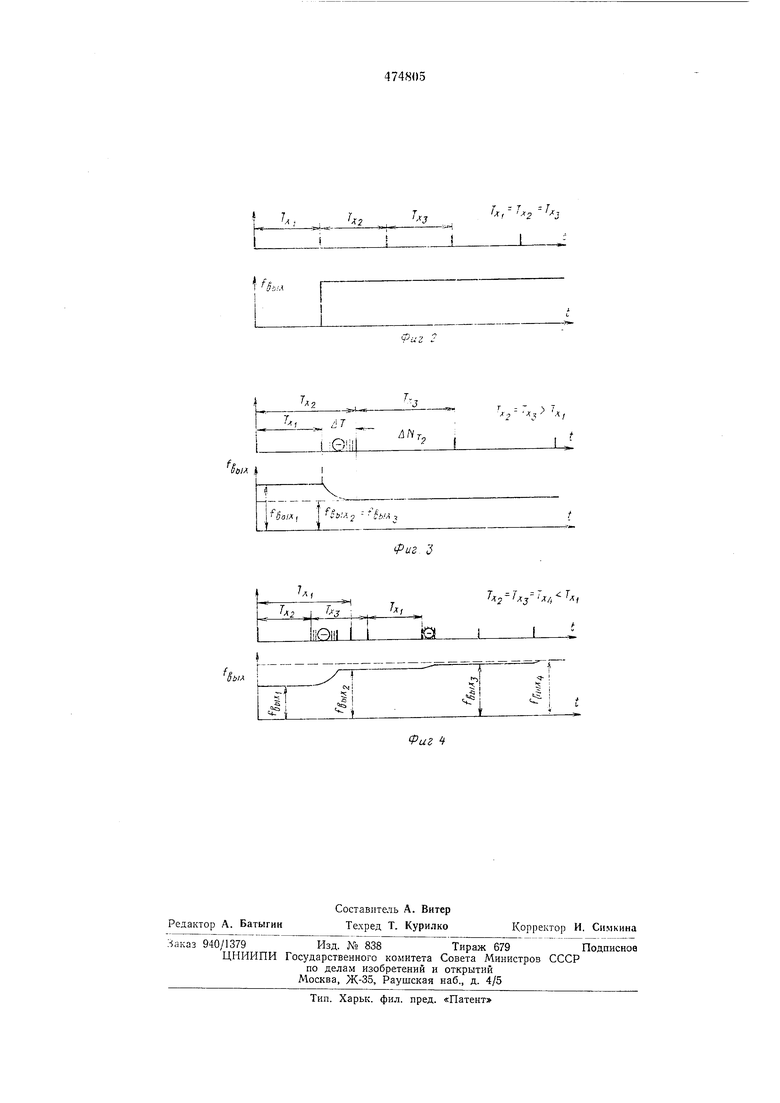

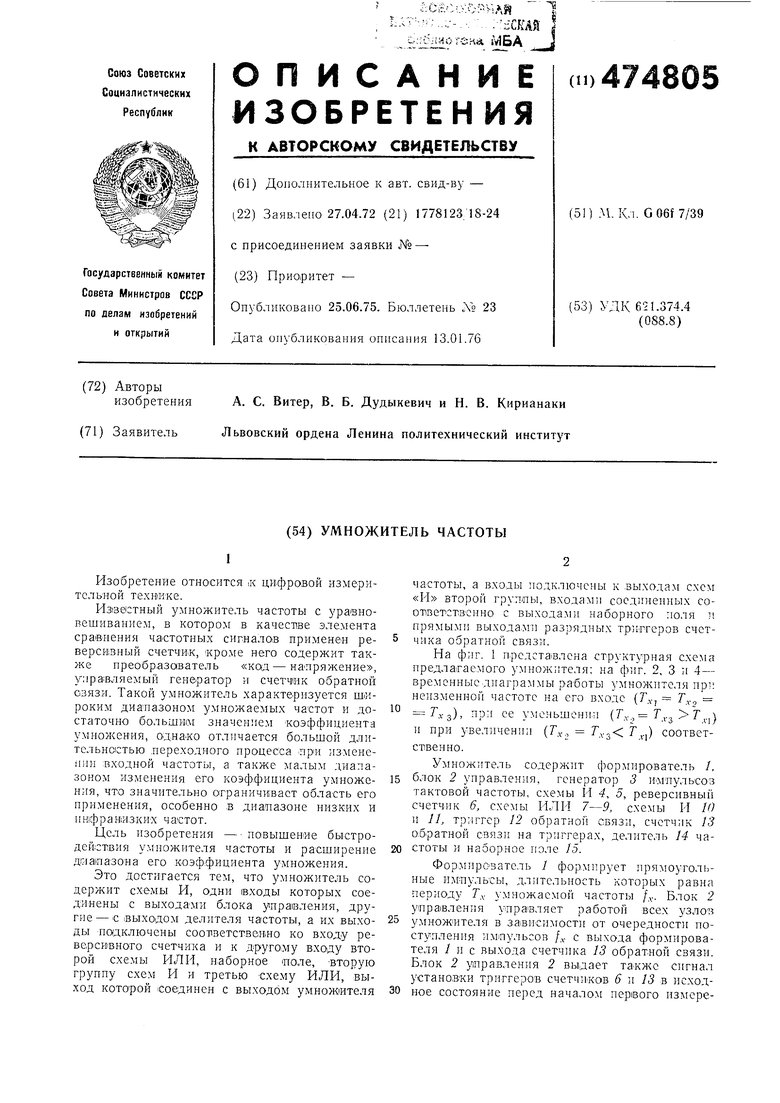

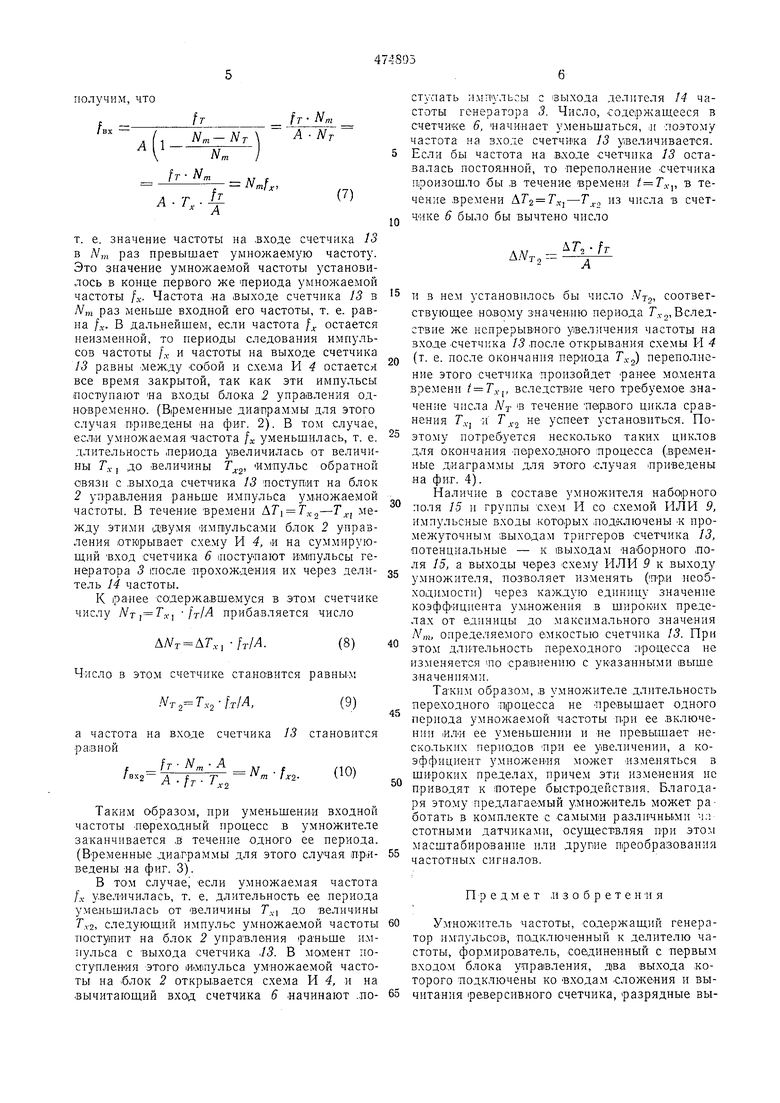

Иа фиг. 1 п.редста влена структурная схема предлагаемого умножителя: на фиг. 2, 3 и 4- временные диаграммы работы умнол ителя ир неизменной частоте на его входе (5.v, Г., Гх. д), при ее уменьшении (Гд.,, Г,. Т .,) и при увеличении (Г., Гтз п) соответственно.

Умнож1 тель содержит формирователь /, блок 2 уиравления, генератор 3 Иl гпyльcoз тактовой частоты, схемы И 4, 5, реверсивный счетчик 6, схемы ИЛИ 7-9, схемы И 10 и 11, триггер 12 обратной связи, счетчик 13 обратной связи на триггерах, делитель }4 ча0 стоты и наборное поле 15.

Формирователь / формирует прямоугольные импульсы, длительность которых равна периоду Гд. умножаемой частоты /д.. Блок 2 управления уира вляет работой всех узлов

умножителя в за1ВПС11Мости от очередности поступленпя импульсов /д. с выхода формирователя / и с выхода счетчика 13 обратной связи. Блок 2 уиравления 2 выдает сигнал установки триггеров счетчи сов 6 и 13 в исход0 ное состояние перед началом первого измереШ1Я, формирует управляющие сигналы на входы «Сложение л-i «Вычитание реверсивного счетчика и сигналы для упра1вления схемы И 4 и 5. Генератор 3 генерирует Имтульсы тактовой частоты, которые подаются на вход выключения триггера 12 обратной связи неиосредсрвенно и на входы схем И 4 и 5-после предварительного деления частоты их следования делителем 14 частоты в А раз, где А - основаНИе системы счисления, принятой при зюстроенИи счетчиков 6 и 13.

Схема И 4 лрп наличии управляющего сигнала с блока 2 управления пропускает имтгульсы с выхода делителя 14 частоты на счетный вход счетчика 6, которые будут у вела-1чивать или уменьшать число, за гисаиное в нем, в зависимости от того, на вход, «Сложение или «Вычитание, подаются управляющие импульсы с блока 2 управления. Схема И 5 .подает имшульсы на вход счетчика 13 Обратной связи, однаКо, в отличпе от схелил И 4, включается в работу только окончания HepiBoro периода TviГрупиа схем И 10 со схемой ИЛИ 7 на выходе предназначена для выборки импульсав цифровой обратной связи, которые подаются на вход триггера 12 обратной овязи. Последн1ИЙ сл.ужит для запомина:нпя имнульсов цифровой обратной-связи на время до прихода следующего имэтульса свыхода генератора 5 HMIH у льсс(в тактовой частоты,которые подаются на его другой вход - вход выключенсчи. Прн этомна выходе триггера/2 образуется п,миульс, который подается на вход счетчика 13 через cxCiMy ИЛИ 8, на второй вход которой подаются импульсы с выхода схемы И 5.

Группа схем И // со схемой ИЛИ 9 на выходе нредназ.начена для уменьшения коэ{)ф1 Цнента ум.ножения cNin до / через каждую единицу путем выборки больщего или меньшего числа импульсов со счетч 1ка 13 обратной связи. Наборное поле 15 Иредна3:наЧе.ио для задания требуемого значения коэффициента умножения умножителя. Импульсы с выхода набор:пого ,поля 15 1;о:даются на входы с.хем И 1 и определяют выходную частоту у множител5.

УлГноЖИтель работает следующим образом.

Иеред люда чей иа вход умножителя входной частоты о,н ириводится в исхсдиое состоя Бие, В котором схемы И 4 и 5 закрыты, в счетчике 5 установлено число Л ,,,, а в счетчике 13 число, равное нулю. С приходом первого имюулыса ум;-юл аемой частоты /. схема И 4 открывается и импульсы тактовой частоты генератора 3 после деления делителе, 14 частоты в Л раз постуиают иа вычитающий вход счетчика 6. В течение периода Т на зход этого счетча1ка постуиит

,fт/A(1)

импульсов, и |будет записано число

,-Л,. Л«-Л,(2)

где N,„ - A - коэффициент пересчета счетчиков 6 и 13;

п - количество разрядов этих счетчпков.

После окончаиия ;периода 7. закрывается схема И 4, и открывается схема И 5. Имиульсы с частотой следования frA -поступают через схему ИЛИ S на 1вход счетчика 13 и изменяют состояния его триггеров. Ироме к -точные выходы триггеров счетчика 13 подключены к импульсным входам вентилей (схем И) груииы 10. К потенциальным входам этих веитилей .подключены основные выходы триггеров счетчика 6. , если к тем или ниым веитилям подключены триггеры старщего разряда счетчика 6, то к этим же вентилям иодключены выходы триггеров младщего разряда счетчика 13, и «аооорот. Ири наличии разрещающего шотенциала ,на выходе соответствующего триггера счетчика 6 ири переходе трИггера счетчика 13 из нулевого и единичное состояние на выходе соответству оил,его вентиля появится имиульс цифровой обратной связи, который через схему ИЛИ 7 поступит на вход триггера 12 и вызовет его :1:ереход из исходного нчлевого в единичное состояпие.

Следующий импульс частоты /т, поступая па второй вход триггера 12, вызовет его оироки,дываиие из ед-шичного в нулевое состояние. Импульс, сш1мае-мый п:ри этом с выхода этого триггера, через ИЛИ 8 поступает на вход счетчика 13. Если же с выхода соответствующего триггера счетчи-ка 6 снимается запирающий потенциал, то импульс на выходе соответствуюи1,его вентиля отсут1ст1вует и дополнительный импульс на вход счетчика 13 не поступит. Таким oi6pai30M, на вход счетчика /5 Шоступает последовательность импульсов с частотой следования /г/Л с выхода делителя 14 частоты, а также .-последовательность импульсов цифровой обработки связи, средняя частота которых определяется кодом числа /Voc, содержащегося в счетчике 6. Для делителя частоты, охваченного положительной цифровой ооратной с.вязью, справедливы соотношения:

(3)

+/ос

)- . f

(4)

ас пос / вх

где: /вх - частота еледОВания импульсов па

входе счетчика 13;

К пос - коэффициент положительной об55ратной связи.

Иа основании (3) и (4) можем записать:

Г

(1-Л-лос)Л

с учетом значения /Спос- разного

Л„, Nn, ,„-- N,n

олучим, что

fr N,n

fj

/вх -- A NT

А Nn,

. fr-Nm ., f ;- - mfjf

A Г.

(7)

A T. e. значение частоты на .входе счетчика 13 в Л ,п раз превышает умножаемую частоту. Это значение умножаемой частоты установилось в конце первого же периода умножаемой частоты fx- Частота -на выходе счетчика 13 в /Vm раз меньше входной его частоты, т. е. равна fx. В дальнейшем, если частота / остается неизменной, то периоды следования импульсов частоты fx и частоты на выходе счетчика 13 равны :между собой и схема И 4 остается все время закрытой, так как эти импульсы поступают на входы бло-ка 2 упра1вления одновременно. (В|ременные диа лраммы для этого случая приведены «а фиг. 2). В том случае, есл.и умножаемая частота fx уменьшилась, т. е. длительность .периода увеличилась от величины TXJ до величины Т., Импульс обратной связи с .выхода счетчика 13 поступит на блок 2 управления раньше импульса умножаемой частоты. В течение времени , между этими Двумя Имп1ульсами блок 2 управления открывает схему И 4, « на суммирующий ВХОД счетчика 6 аюступают имтульсы генератора 5 1Г10сле Прохождения их через делитель 14 частоты. К 1ранее содержавшемуся в этом счетчике числу 1т1А прибавляется число АЛ/т А7,, -IrlA. Число в этом счетчике становится равны-м NT,-Tx,-h-IA,(9) а частота на входе счетчика 13 становится равной fr-N.A 2 л.т /-наA.fr-T Таки.м образо.м, ири уменьшении входной частоты переходный процесс в умножителе заканчивается в течение одного ее периода. (Временные диаграммы для этого случая приведены на фиг. 3). В том случае; если умножаемая частота fx увеличилась, т. е. длительность ее периода уменьшилась от величины TX до величины 7д-2, следующий импульс у.множаелюй частоты поступит на блок 2 управления раньше и.мпульса с выхода счетчика ./. В момент поступления этого И|.м1пульса умножаемой частоты на 1блок 2 открывается схема И 4, и на вычитающий вход счетчика 6 начинают .лоступать импульсы с вы.хода 14 частоты генератора 3. Число, содержандееся в счетчике 6, начинает уменьшаться, л поэтому частота на входе счетчика 13 увеличивается. Если бы частота на входе счетчика 13 оставалась постоянной, то переполнение счетчика произошло бы в течение времени / Г.г,, в течение времени Т2 .,, из числа в счетчике 6 было бы вычтено число ДГа fr A.Vr, и в нем установилось бы число .Vj.,, соответствующее новому Значен;ию периода TV, Вследствие же непрерывного увеличения частоты на входе счетчика 13 лосле открывания схемы И 4 (т. е. после окончания периода Тх переполнение этого счетчика произойдет мо,мента времени Гд.,, вследствие чего требуемое значение числа NT щ течение первого цикла сравнения r.vj и Г д., не успеет установиться. Поэтому потребуется несколько таких циклов для окончания Пере.ходного процесса (временные диаграммы для этого случая приведены на фиг. 4). Наличие в составе умножителя наборного поля 15 и группы схем И со схемой ИЛИ 9, импульсные входы .которых подключены к про.межуточным выходам триггеров счетчика 13, потенциальные - к выходам наборного поля 15, а выходы через схему ИЛИ 9 к выходу умножителя, позволяет изменять (прп необхоаилюсти) через каждую единицу значение коэффициента умножения в широких пределах от едпницы до максимального значения Nm, определяемого емкостью счетчика 13. При этом длительность переходного процесса не изменяется шо сравнению с указанными выше значениями. Таким образом, в умножителе длительность переходного процесса не превышает одного периода умножаемой частоты при ее включении |ИЛИ ее уменьшении и не превышает нескольких периодов При ее увеличении, а коэффициент умножения может изменяться в широких пределах, причем эти изменения не привадят к потере быстродействия. Благодаря этому предлагаемый умножитель может работать в комплекте с самыми различными чл стотными датчиками, осуществляя при этом масштабирование или другие преобразования частотных сигналов. Предмет изобретения Умножитель частоты, содержащий генератор импульсов, подключенный к делителю частоты, фор.мирователь, соединенный с первым входо.м блока упра1вления, два вы.хода которого подключены ко входам сложения и вычитания реверсивного счетчика, разрядные выходы счетчика соединены с одними входами схе,м И Первой группы, др|упие входы которых подключены :К инверсным выходам разрядных триггеров счетчика о братной связи, а выходы схем И первой группы через лервую схему ИЛИ подключены к одному входу триггера обратной связи, другой вход триггера соединен с выходом гене1ратора имлульсов, а его выход подключен к одному входу .второй схемы ИЛИ, ВЫХОД которой соединен со входом счетчика обратной связи, соединенным со вторым .входом блока управления, отличающийся тем, что, с целью расширения диапазона

умножителя, он содержит схемы И, одни ВХОДЫ которых соединены с выходами бло;ка управления, другие - с выходом делителя частоты, а их выходы подключены соответственно ко входу реверсивного счетчика и к другому входу второй схемы ИЛИ, наборное поле, вторую группу схем И и третью схему ИЛИ, выход которой соединен с выходом умноЖИтеля частоты, а входы подключеиы к выходам схем И второй группы, входами соединенных соответственно с выходами наборного ноля и прямыми выхода.ми разрядных триггеров счетчика обратной связи.

i I

2

Ь

%M tf

Д

saw, I сь:/.2 -

Л

Ji

J

-J

ГJ

, д:, л,

4/v.

Авторы

Даты

1975-06-25—Публикация

1972-04-27—Подача