1

Изобретение относится к области автоматики и вычислительной техники и быть использовано в устройствах измерения и преобразования частоты.

Известно узкодиапазонное быстродействующее устройство умножения частоты 1, основанное на логической обработке кода периода входиого сигнала, которое содержит генератор, измеритель «приращения периода входного сигнала, двоичный умножитель, схему вычитания частот и схему управления. При этом выход двоичного умножителя подключен к входу схемы вычитания частот, второй вход которой соединен с генератором, а выход - со входом двоичного умножителя. Код «приращения периода по окончании последнего переписывается в регистр двоичного умножителя, в результате чего на выходе схемы вычитания частота будет ностоянное число раз выше входной.

Недостатком такого устройства является узкий входной диапазон, не превыщающий

вх...

где /в

и /в

максимальное

/в

и минимальное значения умножаемой частоты, соответственно.

Наиболее близким техническим решением к данному изобретению является умножитель

частоты, содержащий генератор, выход которого соединен со входами блока управления и со входом узла вычитания, другой вход которого подключен к выходу элемента ИЛИ, входы которого соединены с выходами элементов И, входы из которых подключены к выходам соответствующих разрядов регистра и первого двоичного счетчика, информационный вход которого соединен с выходом узла вычитания, второй двоичный счетчик регистр, элементы И, второй регистр и узел сравнения; выходы второго двоичного счетчика подключены к одним из входов узла сравнения и через элементы И, другие входы которых соединены с выходом блока управления,-ко входам второго регистра, выходы которого подключены к другим входам узла сравнения и через другие элементы И, вторые входы которых соединены с выходом узла сравнения, к соответствующим входам первого регистра, информационный вход второго счетчика подключен к выходу блока управления, второй вход которого соединен со входной щиной.

Недостатком этого умножителя является узкий входной диапазон. Смещение диапазона в принципе легко достигается изменением частоты генератора, однако при этом приходится либо ограничиваться наименьшим коэффициентом умножения (что определяет больщую погрешность устройства), либо это приводит к

увеличению задержки на онерацию умножения (генерирование умноженной частоты на выходе устройства в соответствии со значением периода начнется по прохождению нескольких периодов).

Цель изобретения - уменьшение погрешности и расширение входного диапазона.

Это достигается тем, что в умножитель введен блок изменения коэффициента деления, к выходам которого подключены управляюидие входы первого и второго двончпых счетчиков и узла сравнения, а входы блока изменения коэффициента деления соединены с выходом блока управления и выходами первого и второго двоичных счетчиков.

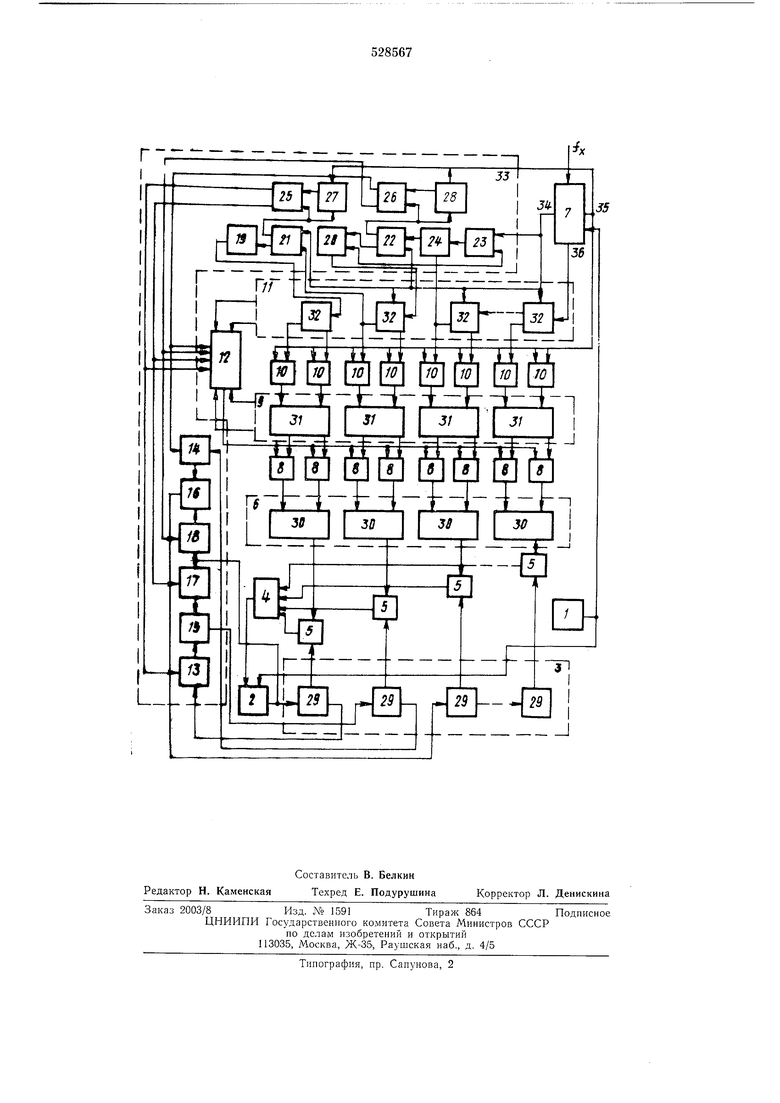

На чертеже показана блок-схема предлагаемого устройства.

Устройство содержит генератор 1; узел вычитания 2; двоичный счетчик 3; элемент ИЛИ 4; элементы И 5; регистр 6; блок управления 7; элементы И 8; регистр 9; элементы И 10; двоичный счетчик 11; узел сравнения 12; элементы И 13, 14; элементы ИЛИ 15, 16; элементы И 17-20; триггеры 21-23; элемент И 24; триггеры 25, 26; элементы И 27, 28; триггеры 29, образующие двоичный счетчик 3; триггеры 30, 31, образуюш.ие регистры 6 и 9 соответственно; триггеры 32, образующие двоичный счетчик 11; узлы 13-28 образуют блок изменения коэффициента деления 33; щины блока управления 34-36.

Устройство работает следуюншм образом. Предположим сначала, что элементы И 19, 20, 13 и 14 открыты, а элементы И 17 и 18 закрыты соответствующими потенциалами с триггеров 21, 22, 25, 26.

Кроме того диапазон входных частот равен 3-4 кГц, а нредельная рабочая частота элементов, на которых выполнено устройство, составляет 1024 кГц. В этом случае максимальное значение коэффициента умножения соста,д „,-„ „

вит М ZOO. Соответственно, ко4 кГц

эффициент деления двоичных счетчиков 3 и 11 будет также равным 256.

Умножаемая частота fx поступает на блок управления 7.

Первым же импульсом с генератора, выделенным на выходе блока управления, осуществляется перепись кода из счетчика 11 в регистр 9. Затем, сигналом с выхОлЧа блока управления 7, осуществляется сброс счетчика 11 в исходное состояние, соответствуюн1,ее двум единицам.

При таком вьшолнении узла измерения приращения периода в процессе формирования кода в двоичном счетчике 11 происходит одно переполнение этого счетчика.

Значение кода Л в двоичном счетчике 11

определяется какЛ -256 (256 - ко/.Iэффициент деления счетчика, fj. - частота генератора 1).

Значение кода Л из двоичного счетчика 11 переписывается в регистр 9, а затем, в течение следующего периода, импульсом с узла сравпеппя 12 в регистр 6.

Частота на выходе двоичного умножителя /д.у. (схема И 4) определяется соотношением:

f „

НГ

где fen - частота на выходе узла вычитания 2. В свою очередь

/свЛ

/со-Гг-/Д.у /Л256 + /У):

256

откуда fcB fx Таким образом на выходе узла вычитания 2 формируется умноженная частота. Назначение регистра 9 и узла сравнения

12 - исключение динамической погрешности

при изменении частоты выходного сигнала за

счет введения постояпного запаздывания на

умножение.

При равенстве прямого кода в двоичном

счетчике 11 и обратного кода в регистре 9 узел сравнения кодов 12 формирует сигнал, по которому код из регистра 9 переписывается в регистр 6. В этом случае относительно начала нериода сигнала, значение кода этого

периода переписывается в регистр 6 по истечении постоянного времени Тз, равного Тз 2-256-Ti. (TI- - длительность периода сигнала с генератора 1). Действительно, Тз т,.(256 + V + Л ) (где

Л - обратное значение кода нрирашения периода) .

Так как геперирование умноженной частоты в соответствии со значением периода входного сигнала начинается с постоянной задержкой относительно начала этого периода, то каждому периоду входпого сигнала ставится в соответствие импульсов на выходе узла вычитания 2. Работа устройства рассматривается из

предположения, что открыты элементы И 13, 14, 19, 20. К концу измерения периода они будут также открыты.

Сигналом сброса с выхода двоичный счетчик И и триггеры 21, 22 возвращаются в исходное состояние, при котором элементы И 19 и 20 закрыты. Затем на вход двоичного счетчика 11 поступают импульсы с частотой генератора 1. После прохождения 62 импульсов,

триггер 23 переключится и откроется элемент И 24. После следующих 64 импульсов сигналом с элемента И 24 переключится триггер 22, откроется элемент И 20 и подтвердится состояние триггера 26, при котором закрыты

элементы И 28, 18 и открыт элемент И 14. После поступления в двоичный счетчик следующих 128 импульсов сработает триггер 21, откроется элемент И 19 и подтвердится состояпие триггера 25, при котором открыт элемент

И 13 и закрыты элементы И 27, 17.

5

Таким образом, после прохождения 256 импульсов относительно начала очередного периода в двоичный счетчик 11 заппсан «ноль, после чего формируется код «приращения периода.

При диапазоне входных частот 6-8 кГц общее число импульсов, поступающих в двоичный счетчик 11, не превысит 254, поэтому триггер 21 к концу периода не переключится, элемент И 27 окажется открытым для сигнала перезаписи с выхода 35. Сигналом с выхода элемента И 27 триггер 25 переключится, закроется элемент И 13 и откроется элемент И 17, т. е. коэффициент деления двоичного счетчика 3 уменьшится в два раза. В два раза изменится и коэффициент умножения. Кроме того, не будет выполняться сравнение соответствующего разряда двоичного счетчика 11 и регистра 9 в узле сравнения 12.

При диапазоне входных частот 12-16 кГц в счетчик 11 пройдет не более 126 импульсов за период, т. к. открытым для сигнала сброса окажется также элемент И 28. По сигналу сброса переключится триггер 26, закроется элемент И 14, откроется элемент И 13 и не будет выполняться сравнение соответствующего разряда счетчика 11 и регистра 9. Коэффициент умножения станет равным 64. Из рассмотрения работы устройства следует, что для диапазона входных частот 24-32 кГц в устройство необходимо ввести ряд узлов, аналогичных по назначению и включению элементам И 13, 14, элементам И 17, 18, элементам И 19, 20, элементам И 27, 28, триггерам 21, 22, триггерам 25, 26 и элементам ИЛИ 15, 16.

Использование предлагаемого изобретения в измерительных системах позволит повысить точность измерительных устройств и применять одну и ту же аппаратуру для работы с большим классом частотных датчиков и преобразователей, что выгодно как с экономической точки зрения, так и с точки зрения простоты и удобства обслуживания.

6 Формула изобретения

Устройство для умножения частоты сигналов, содержащее генератор, выход которого

соединен со входами блока управления и со входом узла вычитания, другой вход которого подключен к выходу элемента ИЛИ, входы которого соединены с выходами элементов И, входы каждого из которых подключены к выходам соответствующих разрядов регистра и нервого двоичного счетчика, информационный вход которого соединен с выходом узла вычитания, второй двоичный счетчик, регистр, элементы И, второй регистр и узел сравнения, выходы второго двоичного счетчика подключены к одним из входов узла сравнения и через элементы И, другие входы которых соединены с выходом блока управлення, - ко входам второго регистра, выходы которого

подключены к другим входам узла сравнения и через другие элементы И, вторые входы которых соединены с выходом узла сравнения, к соответствующим входам первого регистра; информационный вход второго счетчика подключен к выходу блока управления, второй вход которого соединен со входной шиной, о тл и чающееся тем, что, с целью уменьшения погрешности и расширения входного диапазона, в него введен блок изменения коэффициента деления, к выходам которого подключены управляющие входы первого и второго двоичнььх счетчиков и узла сравнения, а входы блока изменения коэффициента деления соединены с выходом блока управления

и выходами первого и второго двоичных счетчиков.

Источники информации. нр1 нятые 40во внимание при экспертизе:

1.Авт. св. АО 404173 кл. Н ОЗВ, 19/00, 28.06.68.

2.Авт. св. Лд 354412 кл. G 06F, 7/52. 02.01.69.

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты следования импульсов | 1981 |

|

SU966848A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU993451A1 |

| Умножитель частоты | 1986 |

|

SU1385230A1 |

| Устройство для определения объемного расхода жидкости | 1989 |

|

SU1723440A1 |

| Устройство для дифференцирования частотно-импульсных сигналов | 1977 |

|

SU732904A1 |

| Умножитель частоты | 1979 |

|

SU907781A1 |

| Устройство умножения частоты следования импульсов | 1975 |

|

SU528695A1 |

| Умножитель частоты | 1978 |

|

SU790328A1 |

| Устройство для измерения частоты | 1987 |

|

SU1465803A1 |

| УМНОЖИТЕЛЬ ЧАСТОТЫ | 1973 |

|

SU404173A1 |

Авторы

Даты

1976-09-15—Публикация

1974-01-16—Подача