О1 00 0

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРИЕМНОЕ УСТРОЙСТВО ГИДРОЛОКАТОРА БОКОВОГО ОБЗОРА | 1993 |

|

RU2060516C1 |

| Функциональный преобразователь | 1983 |

|

SU1115069A1 |

| Устройство для предварительной фильтрации входных сигналов узкополосных цифровых фильтров | 1990 |

|

SU1739481A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2502128C2 |

| Многоканальное устройство для ввода аналоговых данных | 1986 |

|

SU1335972A1 |

| Устройство для анализа распределений случайных процессов | 1984 |

|

SU1164734A1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Устройство для преобразования телевизионного стандарта | 1986 |

|

SU1343562A1 |

| УСТРОЙСТВО для ПРОСТРАНСТВЕННО-ВРЕМЕННОГО СЕЙСМИЧЕСКОГО АНАЛИЗА | 1973 |

|

SU393742A1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

Изобретение относится к радиотехнике и может быть использовано в радиоприемных устройствах, работающих в условиях воздействия мощных нестационарных помех с негауссовским распределением вероятностей мгновенных значений. Цель изобретения - увеличение отношения мощности полезного сигнала к мощности помехи с несимметричным законом распределения плотности вероятности мгновенных значений и неизвестной мощностью. Введенные в устройство счетчик 13, блоки 11, 12 оперативной памяти, блок 3 стабилизации средней мощности, генератор 1, АЦП 6 и сумматоры 14, 4 позволяют обеспечить запоминание входной реализации помехи, оценку ее числовых характеристик и вычисление оптимальных уровней процесса на выходе устройства, а также расширить динамический диапазон подавляемых помех. 2 ил.

Фаг.1

; Изобретение относится к радиотехijiHKe и может быть использовано в ра- ;}щоприемкьгх устройствах, работающих ф условиях воздействия мощных неста- щонарных помех негауссовским распределением вероятностей мгновенных зна- .

; Цель изобретения - увеличение от- ошения мощности прлезного сигнала 1 мощности помехи с несимметричным laKOHoM распределения плотности веВ

оятности мгновенных значений и неиз

щестной мощностью.

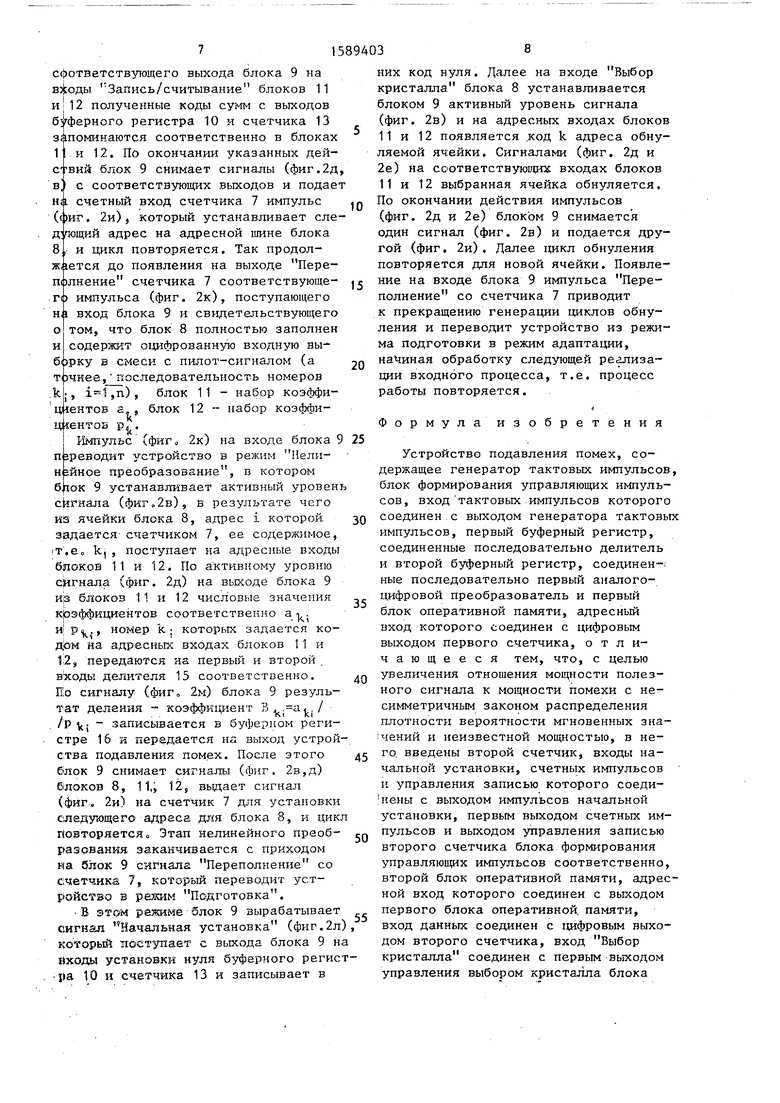

На фиг о 1 представлена структурная электрическая схема устройства годавления помех; на фиг. 2 - эпюры управляющих сигналов устройства.

Устройство подавления помех содер т генератор 1 пилот-сигнала, гене- Р|атор 2 -тактовых импульсов, блок 3 с|табилизации средней мощности, второ С умматор 4, первый аналого-цифровой феобразователь 5, второй аналого- 1:|ифровой преобразователь 6, первый с1четчик 7, первый блок 8 оператив- н|ой памяти, блок 9 формирования уп- Р|авляю цих импульсов, первый буферный р|егистр 10, третий блок 1 1 оперативней памяти, второй блок 12 оперативней памяти, второй счетчик 13, первы сумматор 14, делитель 15, второй бу- ферньй регистр 16.

Устройство работает следующим об- pjasoM.

В устройстве реализуется адаптив- нелинейная обработка реализации выходного процесса в п отсчетов по критерию минимума среднего квадрата о|шибки (СКО), выделение детерминированного сигнала S;, наблюдаемого в а|ддитивной смеси с входным процессом к, и кспользуется представление ам- л литудной характеристики устройства в виде обобщенного полинома

f(x)iв.p(x),

где B-i - параметры настройки амплитудной характеристики устройства;

Р Ч,(х)

I /-1

, f-z. или X

где Z - пороги квантования входного процесса (в данном случае - равномер кого квантования): z,z . .+dz, /32

,К К-1

const.

Система ортогональных функции Ч,(х) обладает следующими свойствами

если Z. i X Z к 1«-1

если x-cz 1ШИ X 9 Z j,

0

5

0

i/ fe(x)(x)0 при kjfv; Cf2(x) ef(x). Ее генератором является обычный аналого-цифровой преобразователь (АЦП) с п уровнями квантования на выходе, так как код числа на его выходе соответствует попаданию значения напряжения на его входе в интервал, в котором равна единице только одна функция с номером, равным этому числу, остальные функций на этом интервале, а значит, и при этом входном напряжении, равны нулю. Таким образом, в АЦП значение функции () в i-й отсчет времени с числом k. соответствует номеру выбранного входным напряжением х. интервала.

Оптимальные уровни квантования В. обеспечивают минимум

cko Cf(x,.+S,.)-SO2

i LiB If (x.+s.)

i bi т

и-удовлетворяют системе m линейных уравнений вида

(x.-fsV)cf()

V.1

{.1 я

,.+S,), ,m,

KDTopbte в силу ортогональности функций (f(x) упрощаются

V,|(x,-bS.)|.SiC(x(+S.), с

k ТТй;

и дают следующее решение и алгоритм адаптации:

В.

a,/Pt,

где а (x.-bS.); р ,.+ +S,), ,m.

Таким образом, оптимальное нелинейное преобразова:ние входного процесса имеет вид

.S,)-,,).

Устройство работает в режимах адаптации, э процессе которого вычисляются коэффициенты а Pjt и собственно оптимального нелинейного преобразования. Так как функции qi,(x) имеют непересекающиеся области определения, то расчет аци рц сводится к определению номера k функции Ч, (х) по отсчету входного процесса, что осуществляет АЦП, и к сложению содержимого области памяти с адресом k с сигналом S (при вычислении а) KSIK с единицей (при вычислении р.) . После

перебора входной выборки объема п в соответствукщих областях памяти будет храниться набор коэффициентов а. и р . Таким образом реализуется вычисление коэффициентов а, и р, по рекуррентным формулам:

,; . Для осуществления после этого оптимального нелинейного преобразования необходимо преобразованную с помощью АЦП в последовательность номеров входную выборку запомнить в отдельной области памяти, чтобы затем, выбирая из этой области соответствующий отсчету входного процесса х. +S . номер .kj, передавать на выход резул ьтат деления , являющийся отсчетом выходного оптимально-нелинейно преобразованного процесса. После обработки каждой входной реализации необходимо перед следующей обработкой устройство подавления помех перевести в исходное состояние, т.е. обнулить ячейки памяти, отведенные под коэффициенты а и р, что осуществляется в режиме подготовки.

Управление работой устройства подавления помех во всех режимах осуществляется блоком 9. Работу блока 9 и всего устройства иллюстрируют временные диаграммы на фиг. 2.

В режиме адаптации на вход блока 3, являющегося входом устройства, поступает процесс х., содержащий полезный сигнал. С выхода блока 3, обеспечивающего деление входного сигнала на его эффективное значение, стабилизированный по средней мощности процесс X . поступает на первый вход сумматора 4, на второй вход которого, а также на вход аналого-цифрового преобразователя 6 подает с выхода генератора 1 пилот-сигнал S,-. Коэффициенты передачи сумматора 4 по первому и второму входам не равны и устанавливаются такими, чтобы отношение сигнал/помеха на выходе сумматора А не превьш1ало -20 дБ. С вьгхода сумматора 4 полученная смесь пилот158

5(3 55

сигнала и процесса х. поступает на вход аналого-цифрового преобразователя 5. Быстродействие устройства определяется частотой тактовых импульсов, поступающих с выхода генератора 2 на тактовые входы аналого-цифровых пре- . образователей 5 и 6 и синхронизирующий вход блока 9. Оба аналого-цифровых преобразователя 5 и 6 по сигет . е

1589403

налу на входе Преобразование, поступающему с выхода блока 9 (фигЛа):/ вырабатывают код числа k ., соответст вующий уровню входного напряжения

x.+Sj, устанавливают этот код на своем выходе и сигнализируют об этом активным уровнем на выходе Готовность данных. По сигналу Готовность ных (фиг. 2б), поступающему на вход блока 9, последний формирует импульсы (фиг. 2в, г), поступающие на входы блока 8 и осуществляющие запись в него установленного на выходе анало15 го-цифрового преобразотеля 5 кода k. по адресу i, который определяется со35

держимым счетчика 7. Разрядность счетчика 7 и емкость блока 8 определяют объем выборки, который может обраба- 20 тываться устройством. Далее блок 9 снимает сигнал (фиг. 2г), оставляя активным уровень на входе Выбор кристалла блока 8, и записанньй код k. устанавливается на выходе блока 8 и 25 на адресных входах блоков 11 и 12. Количество разрядов адресной шины блоков 11 и 12 равно количеству разрядов шины данных блока 8 и аналого- цифрового преобразователя 5 и опре- 30 деляется выбранным числом уровней квантования m в аналого-цифровом преобразователе 5. Далее блок 9 устанавливает на соответствующем вы- ходе сигнал (фиг. 2д), который, поступая на входы Выбор кристалла блоков 11 и 12, осуществляет считы- вание записанньк в этих блоках кодов К Р соответственно. Код числа а с выхода блока 11 поступает на вход до сумматора 14, на другом входе которого установлен код с выхода аналого- цифрового преобразователя 6, соответ- ствукйций отсчету пилот-сигнала S;, а с выхода блока 12 код числа р поступает на вход счетчика 13, где запоминается с приходом на синхронизирующий вход импульса (фиг. 2ж) с блока 9. С выхода сумматора 14 цифровой код суммы содержимого бло- (3 ка 11 с цифровым кодом пипот-сигнапа подается на вход буферного регистг . ра 10. Импульс (фиг. 2з), поступая с соответствующего выхода блока 9 на синхронизирующий вход буферного ре- 5 гистра 10, осуществляет запись в буферный регистр 10 этого кода, а поступая на счетньм вход счетчика 13, - сложение содержимого блока 12 с единицей. Далее по сигналу (фиг. 2е) с

5

сфответствующего выхода блока 9 на в:|соды Запись/считывание блоков 11 иМ2 полученные коды сумм с выходов буферного регистра 10 и счетчика 13 запоминаются соответственно в блоках li и 12. По окончании указанных действий блок 9 снимает сигналы (фиг.2д, в) с соответствующих выходов и подает н счетный вход счетчика 7 импульс (оиг. 2и)J который устанавливает сле

д:/тощий адрес на адресной шине блока 8 и цикл повторяется. Так продолжается до появления на выходе Переполнение счетчика 7 соответствующего импульса (фиг. 2к), поступающего на вход блока 9 и свидетельствующего о том, что блок 8 полностью заполнен и содержит оцифрованную входную вы- б(|)рку в смеси с пилот-сигналом (а т|зчнее, последовательность номеров ,k|j, i-1 ,п) , блок 11 - набор коэффи- ьфентов а,J блок 12 набор коэффи- 1фентоБ р, . Импульс (фиг i

2к) на входе блока 9 п греводит устройство в режим Иели- нгйное преобразование, в котором блок 9 устанавливает активный уровен сигнала (фиг.2в), в результате чего из ячейки блока 8, адрес i которой. задается счетчиком 7, ее содержимое, iT.e k,, поступает на адресные входы блоков 11 и 12. По активному уровню сигнала (фиг. 2д) на выходе блока 9 из блоков 11 и 12 числовые значения крэффициентов соответственно а-. И: Р., номер k; которых задается кодом на адресных входах блоков 11 и 1;2, передаются иа первый и второй , входы делителя 15 соответственно. По сигналу (фиго 2м) блока 9 результат деления - коэффициент З..а../

.. .К,1 КI

Р Vi записывается в буферном регистре 16 и передается на выход устройства подавления помех. После этого блок 9 снимает сигналы (фиг. 2в,д) блоков 8, 11,i 12, вьщает сигнал (фиг, 2и) на счетчик 7 для установки следующего адреса для блока В, и цик Повторяется о Этап нелинейного преоб- Е азования заканчивается с приходом на блок 9 сигнала Переполнение со счетчика 7, который переводит устройство в режим Подготовка.

В этом режимеблок 9 вырабатывает сигнал Начальная установка (фиг.2л), который лоступает с выхода блока 9 на входы установки нуля буферного регист- -ра 10 и счетчика 13 и записывает в

них код нуля. Далее на входе Выбор кристалла блока 8 устанавливается

блоком 9 активный уровень сигнала (фиг. 2в) и на адресных входах блоков 11 и 12 появляется код k адреса обнуляемой ячейки. Сигналами (фиг. 2д и 2е) на соответствуюищх входах блоков 11 и 12 выбранная ячейка обнуляется. По окончании действия импульсов (фиг. 2д и 2е) блоком 9 снимается один сигнал (фиг. 2в) и подается другой (фиг. 2и). Далее цикл обнуления повторяется для новой ячейки. Появле- ние на входе блока 9 импульса Переполнение со счетчика 7 приводит к прекращению генерации циклов обнуления и переводит устройство из режима подготовки в режим адаптации, на 1иная обработку следующей реализации входного процесса, т.е. процесс работы повторяется.

Формула изобретения

Устройство подавления помех, содержащее генератор тактовых импульсов, блок формирования управляющих импульсов, вход тактовых импульсов которого соединен с выходом генератора тактовых импульсов, первый буферный регистр, соединенные последовательно делитель и второй буферный регистр, соединен-; ные последовательно первый аналого- цифровой преобразователь и первый блок оперативной памяти, адресный вход которого соединен с цифровым выходом первого счетчика, отличающееся тем, что, с целью увеличения отношения мощности полезного сигнала к мощности помехи с несимметричным законом распределения плотности вероятности мгновенных зна- чений и неизвестной мощностью, в него, введены второй счетчик, входы начальной установки, счетных импульсов и управления записью которого соеди- |нены с выходом импульсов начальной установки, первым выходом счетных импульсов и выходом управления записью второго счетчика блока формирования управляющих импульсов соответственно, второй блок оперативной памяти, адресной вход которого соединен с выходом первого блока оперативной, памяти, вход данных соединен с цифровым выходом второго счетчика, вход Выбор кристалла соединен с первым выходом управления выбором кристалла блока

формирования управляющих импульсов, вход управления записью-считыванием соединен с первым выходом управления записью-считыванием блока формрфова- ния управляющих импульсов, а выход соединен с первым входом делителя и входом данных второго счетчика, третий блок оперативной памяти, вход данных которого соединен с выходом первого буферного регистра, адресный вход соединен с выходом первого блока оперативной памяти, вход Выбор кристалла соединен с первым выходом уп10

является входом устройства, и вто сумматор, другой вход которого со нен с выходом генератора пилот-си ла, а выход соединен с сигнальным входом первого аналого-цифрового образователя, вход счетных импуль первого счетчика соединен с вторы выходом счетных импульсов блока ф мирования управляющих импульсов, выход сигнала переполнения соедин с входом си нала смены режима раб блока формирования управляющих им пульсов, эыходы сигнала Готовнос

равления выбором кристалла блока Фор- ,5 данных первого аналого-цифрового

1мирования управляющих импульсов, вход управления записью-считьгаанием соединен с первым выходом .управления записью-считыванием блока формирования управляющих импульсов, а выход jn соединен с вторым входом делителя, соединенные последовате льно генератор пилот-сигнала, второй аналого-цифровой преобразователь, вход тактовых импульсов которого соединен с выходом 25 генератора тактовых импульсов, а вход управления преобразованием соединен с входом управления преобразованием первого аналого-цифрового преобразователя и выходом управления преобра- зо зованием блока формирования управляющих импульсов, и первый сумматор, другой вход которого соединен с выходом третьего блока оперативной памяти, а выход соединен с входом данного первого буферного регистра, соединен- ные последовательно блок стабилизации средней мощности, вход которого

преобразователя соединен с входом пускающего импульса блока формиров ния управляющих импульсов, вход В бор кристалла и вход управления з писью-считыванием первого блока оп ративной памяти соединены с вторым выходом управления выбором кристал и с вторым выходом управления запи считыванием блока формирования упр ляющих импульсов соответственно, вход управления записью второго бу ферного регистра, выход которого я ляется выходом устройства, соедине с выходом сигнала управления запис второго буферного регистра блока ф мирования управляющих импульсов, вход начальной установки и вход сч тывания первого буферного регистра соединены с выходом начальной уста новки и первым выходом счетных импульсов блока формирования управля щих импульсов соответственно.

является входом устройства, и второй сумматор, другой вход которого соединен с выходом генератора пилот-сигнала, а выход соединен с сигнальным входом первого аналого-цифрового преобразователя, вход счетных импульсов первого счетчика соединен с вторым выходом счетных импульсов блока формирования управляющих импульсов, а выход сигнала переполнения соединен с входом си нала смены режима работы блока формирования управляющих импульсов, эыходы сигнала Готовность

данных первого аналого-цифрового

данных первого аналого-цифрового

преобразователя соединен с входом запускающего импульса блока формирования управляющих импульсов, вход Выбор кристалла и вход управления записью-считыванием первого блока оперативной памяти соединены с вторым выходом управления выбором кристалла и с вторым выходом управления записью считыванием блока формирования управляющих импульсов соответственно, вход управления записью второго буферного регистра, выход которого является выходом устройства, соединен с выходом сигнала управления записью второго буферного регистра блока формирования управляющих импульсов, вход начальной установки и вход считывания первого буферного регистра соединены с выходом начальной установки и первым выходом счетных импульсов блока формирования управляющих импульсов соответственно.

ta «сэ «э

п:э oj V ст)

- ХГ

| Устройство подавления помех | 1985 |

|

SU1338079A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-08-30—Публикация

1988-11-09—Подача