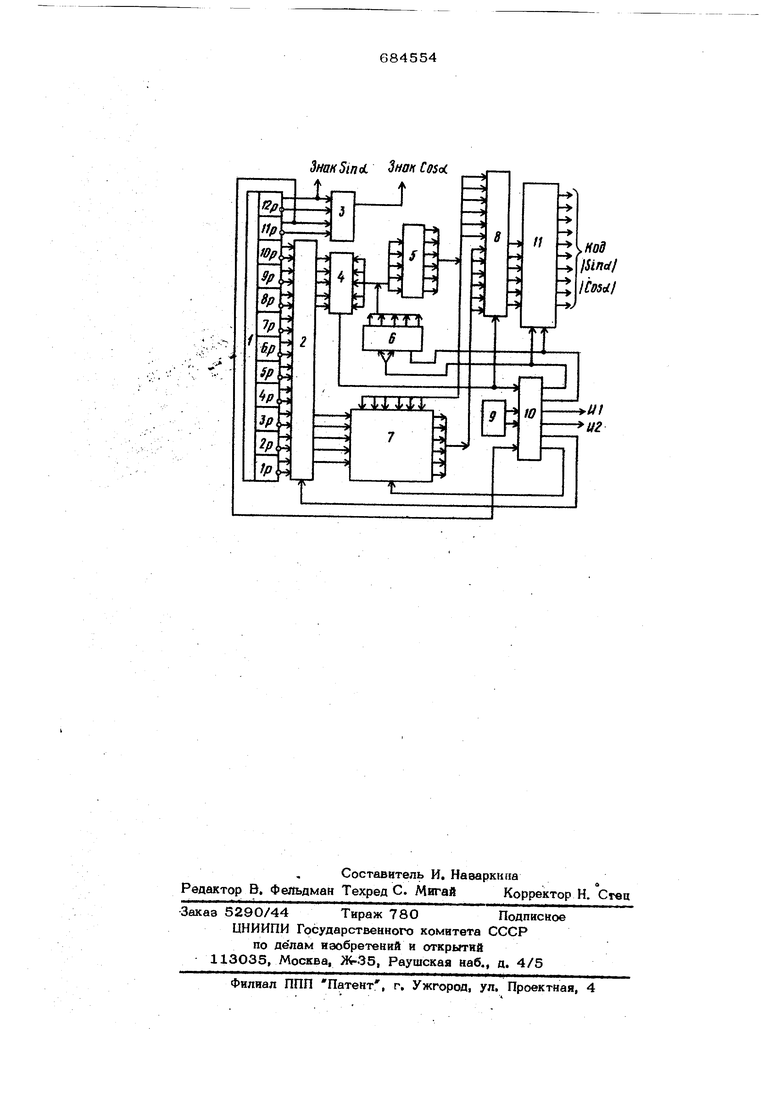

Изобретение относится к вычислительной технике, в частности к специализированным вычислителим и предназначено для преобразования параллельного Korib угла в код синуса и код косинуса. Известны устройства, которые вырабатывают код синуса и код косинуса по параллельному коду утла. Самыми быстродействующими из этих устройств являются преобразователи (генераторы), выполненные на постоянных запоминающих устройствах (ПЗУ). Однако при увеличении точности (разрядности) воспроизведения функщА увеличивается емкость ПЗУ, что затрудняет фи зическую реализацию последних. Известно также, что для воспроизведения функций наиболее .широкое применение получил метод кусочио-линейнсЛ аппроксимации, так как наряду с простотой он обеспечивает требуемую точность. 1аибопее близким к изобретению является преобразователь кода угла в кода синуса и косинуса, содержащий датчикиpaspsiAHoro кода, выходы младших разрядов которого соединены со входами первого коммутатора кодов, а выходы старших paspscAOB - со входами блока определения эвака косинуса, цифровой компаратор, запоминающее устройство с ia-2-К адресными к 1ходами, счетчик импульсов, множителШ блок и генератор импульсов З1, Функовонирование известного преобразователя основано на использовании принципа кусочно-линейной аппроксимаций. Этот преобразователь может вырабатьгаать синус или косинус аргумента, npeACTBBJraHного параллельным кодом, и работает циклически. Генератор импульсов (эталошюго синусоидального чвспоимпульгного кода от О до ЭО) содержит (п-2) разрядный счетчик, ПЗУ-, имеющее (n-2-K) адресных входов и К выходов, множительное устройство, образующее с К младшими разрядами счетчика чисЬлоимпуньсный прео азователь (множительный блок, один из сомножителей которого представлен параллельным кодом, а другой - числоим пульсным), числовые входы которого под ключены к выходам ПЗУ, у которого адресные входы соедршены с выходами (п 2-к) старших разрядов счетчика , Длительность цикла преобразования за висит от величины ct. и няходится в пределах от1. , где t - период частоты следования тактовых импульсов источника синхроимпульсов;п. - разрядность аргумента. Так как при преобразовании с выходов одного из коммутаторов кода, снимается код приведенного apry NieHra р или , а с выходов другого - & или , то в силу специфики представления информации двоичным кодом приведенный аргумент будет представлен на выходах одного из коммутаторов кода с методической погреш ностью, так как (М2лг.а-), где р - часть аргумента oL определяемая кодом (п. -2) младших разрядов аргу мента oL . Это приводит к соответствующим погре ностям определения функций, точность вос произведения которых в этом устройстве недостаточна еще из-за того, что вес младшего раз|эяда воспрЬизводимой функции 2-(п-3) больше, чем (2l3t2 радиан) вес младшего разряда датчика аргумента , Поэтому в устройстве повысить точность воспроизведения функций можно тол ко путем увеличения разрядности датчика, что, с свою очередь, приводит к увеличению длительности цикла преобразования. Недостатками преобразователя являет- ся невысокая точность и малое быстродей ствие,. Целью изобретения является повышение точности и быстродействия устройства. Поставленная цель достигается тем, что в преобразователь кода угла в коды синуса и косинуса введены сумматор и блок синхронизации, выходы к младших разрядов первого коммутатора кодов соединены со входами второго сомножителя множительного блока, остальные выходы первого коммутатора соединены со входами первого кода цифрового компаратора, входы второго кода которого объединены с адресными входами запоминаю.щего устройства и подключены к выходам счетчика импульсов, К + 1 выходов запоминаЕощего устройства соединены со входами пе вого сомножителя множительного блока и с одними из входов второго коммутатора кодов, другие входы которого соединены с выходами множительного блока, выходы второго коммутатора кодов соединены со входами сумматора, выход цифрового компаратора подключен к управляющему входу второго коммутатора кодов и к одному из входов блока синхронизации, другие входы которого соединены с выходами генератора импульсов и с выходом одного из старших разрядов датчика л -разрядного кода, один из выходов блока синхронизации соединен с установочными входами сумматора и счетчика импульсов, второйсо счетными входами -счетчика импульсов и тактовым входом сумматора, третий выход блока синхронизации соединен с управляющим входом первого коммутатора кодов, а четвертый выход - с входом коррекции множительного блока. . На. чертеже приведена структурная схема, поясняющая сущность предлагаемого изобретения. Схема выполнена для преобразования двенадцатиразрядного кода аргумента сС в одиннадцатиразрядный код sintS. и одинадцатираерядный код cos е Преобразователь содержит датчик 1 П - разрядного кода (прямого и инверс- . ного двенадцатиразрядного кода), коммутатор кодоЬ 2, подключенньА к выходам десяти млайШИх } аврядов датчика 1, блок 3 определения знака косинуса, подключенный м выхойам двух старших разрядов датчика 1, .цифровой компаратор 4, запоминающее устройство 5, имеюшве пять адресных входов и шесть выходов, счетчик 6- импульсов, множительный блок 7, коммутатор кодов 8, генератор- импульсов 9, блок синхронизации 10, сумматор 11 (накапливающий десятиразряцный), входы которого подключены через коммутатор кодов 8 к выходам множительного блока 7 и. к выходам запоминающего устройства 5, подключенным ко входам первого сомножителя множительного блока 7, входы второго сомножителя которого подсоединены к выходам пяти младших разрядов коммутатора кодов 2, остальные выходы которого соединены с входами первого кода цифрового компаратора 4, входы второго кода которого соединены с адресными входами запоминающего устройства 5 и подключены к выходам счёгчика 6, у которого счетный вход и вход установки в нуль соединены соответственно с тактовым входом и с одноименным входом выходного сумматора 11 и подключены к соответствующим выходам блока синхро- низации 10, один из входов которого соединен с выходом цифрового компаратора 4, подсоединенным к управляющему входу коммутатора кодов 8, а другие подключены к выходам генератора импульсов 9 и к выходу одиннадцатого разряда датчика 1, при этом один из выходов блока синхронизации 10 соединен с управляющим входом коммутатора кодов 2, а другой подключен к корректирующему входу множительного блока 7. Запоминающее устройство 5 выполнено по, схеме дещифратора - щифратора на логических комбинационных элементах и содержит дещифратор пятиразрядного кода и шифратор, работой которого управляет дешифратор таким образом, что на выходах шифратора вырабатывается шестиразр5Щный код углового коэффициента Ki 1-го участка аппроксимации. Множительный блок 7 содержит четыре шести разрядных параллельных комбинационных сумматора, четыре группы элементов И и группу элементов 2И-2И-ИЛИ, р ботой которой управляет логический блок, подключенный к корректирующему входу и к входу младщего разряда второго сомножителя множительного блока, а каждый другой разряд второго сомножителя управляет работой соответствующей группы эле-, ментов И, при этом входы первого{срмно жителя множительного блока подключены ко входам логических групп, выходы которых соединены со входами соответствующих сумматоров, соединенных между собой . соответствующим образом, с выходов одного из сумматоров снимается щестир з- рядный код произведения. Сумматор 11 содержит десятиразрядный регистр на триггерах THnaD V и да- пятиразрядный параллельньй комбинационный сумматор, выходы которого соединены со входами регистра, выходы послед- рего соединены со входами одного из елагаемых сумматора, входы другогослагэе- мого которого подключены к входам спага мого сумматора 11. Преобразователь выполнен на элементной базе, триггеры которой переключают- ся в моменты после окончания тактовых импульсов на их синхронизующих входах. Работа предлагаемого устройства заключается в следующем. Преобразователь по двенадцатиразряд- ному коду аргумента .() циклически вырабатывает одиннадцатираэрядные коды sindk. и cose , а также форКли- рует импульс (И1) конца определения коа . н {И2) импульс конца определения ода собоС и выдает эту информацию на выоды. С гарщие разряды у кодов sincn и собчЛ. и знаковые определяются гГо двум старигам разрядам датчика 1. Поэтому двенадцатый разряд датчика 1 является знаковым разрядом кода Stnot- f а знаковый разряд кода coscn. вырабатывается блоком 3 определения знака косинуса как сумма по модулю два логические значения одиннадцатого и нвенадцатого радр5шов датчика 1, Определение кодов чисел б пл1 R|cos«i.| осуществляется методом кусочноглиней ной аштроксимадии с использованием известных тригонометрических формул приведения. Аппроксимация фугжций производится в угле от нуля до , который на32 равных участка, т. е. м 1числеяиефункции|в пЬ11 или функции1с08,| производится по приведенному углу или десятираэрядный код которого снимается с выходов коммутатора кодов 2, -2К-2. угол, величина которого опреляется прямым кодом десяти младщих разрядов датчика 1; Р«-23 г ,i-1 - угол, величина 5: ai. 2 которого определяется инверсным кодом десяти младщих разрядов датчика 1, 2 л ai - Соответственно весовой и разрядный коэффициенты i -го разряда кода датчика 1, Перед началом цикла преобразования в счетчике 6 и сумматоре 11 содержатся результаты предыдущего цикла преобразования. Для определенности будем считать, что, начиная с этого момента и до окончания цикла преобразования, код oL не изменяется, а О, т. е. перед началом цикла преобразования с выходов Коммугагора кодов 2 снимается код Jb . Цикл преобразования начинается с приходом or гвиерагора импульсов 9 на блок синхронвзашш 10 старт-импульса. По этому нмаульсублок синхронизации 10 устанавливает нуль счетчик 6 и сумматор 11, а затем пропускает на счетный вход счетчика 6 и тактовый вход сумматора 11 серию кмпульсов, число которых равна, + i-fO . , . ,у ai .2 } о участка ап .j проксимации, определяемой пятью стар шими разрядами кода, причем i. жет принимать значе ния из ряда О, 1, 1 oJ-« Код старших разрядов г сиимемый с коммутатора кодов 2, сравнивается с (t) текущим кодом счетчика 6 при помощи цифрового компаратора 4. При этом цифровой компаратор 4 вырабатьтвает логический сигнал F таким обра зом, что, если PI jt (t) , то F О, а если Pi, f(t , то F 1. С цифрового компаратора 4 сигнал F поступает на один из входов блока синхронизации 1О и управляет работой коммутатора кодов 8 таким образом, что если F О, то коммутатор кодов 8 подключает на входы сумматора 11 вьЬсоды запоминающего устройства 5, а если , то - выходы множитель ного блока 7. На выходах запоминающего устройства 5, адресные входы которого подключены к выходам счетчика 6, вырабатывается последовательно шестиразрядный код углового коэффициента Ко, Kf, ...К} ...,Ki. . Причем под угловым коэффициентом К, поднимается код числа (np + -sinfi - ), вес младшего разряда которого равен 2. Так как преобразователь выполнен на элементной базе, которой переключаются в моменты после окончания импульсов на их синхронизирующих входах ,то после окончания 4--го импульса в вь,ход ном сумматоре содержится код (, синуса в начале -го участка .аппроксима они,а на выходах множительного блока 7 которые подключены через коммутатор кодов 8 к входам сумматора 11, вырабаты- вается шестиразрядный код К. .,, . где Д 21 а -2 - число между О ii И , определяемое пятью младшими раз рядами кода . Поэтому после окончания последнего импульса серии № i с выходов сумматоpa 11 будет сниматься код числа Sinjbj. + Ki-4pi |s notf После этого блок синхронизации 10 подлючает на выходы коммутатора кола 2 од Р и вырабатывает на выход устройтва импульс (И1) окончания первого пеиода преобразования, по которому сниматся с выходов преобразователя код&1П«/. а этом период Т1 заканчивается, и наинается период Т2, в котором блок синронизации вновь генерирует импульс усановки в нуль счетчика 6 и сумматора 1, а затем на счетный вход счетчика б тактовый вход сумматора 11 пропускает т генератора импульсо серию № 2 имульсов, причем Н2 i + 1, -. ««40 - номер участка n..-Jr аппроксимации, определяемый пятью старшими разрядами кода . Так как во втором периоде вычисле ;ие со ji/про изводится по приведенному углу J9 представленному на выходах коммутатора кодов с методической погрешностью 23С 2 радиан, то блок синхронизации в течение периода Т 2,на корректирующий вход множительного блока 7 вырабатывает сигнал логической i, по которому в момент.действия последнего импульса серии № 2 иа входы сумматора 11 через коммутатор кодов- 8 будет подаваться с выходов множительного блока 7 код числа Kj-(). После окончания последнего импульса серии № 2 блок управления подключег на выходы коммутатора кодов 2 код /i и вырабатывает импульс конца преобразования - ° ь,ходов сумматора U может сниматься код числа sinAj 1-Кр(АД . Z) , д., где81Пр - начальное значение синуса на . участке аппроксимации. На этом цикл вычислений заканчивается, а следующий цикл начинается ront ко с приходом от генератора импульсов 9 на блок синхронизации 10 очередного сТарт-импульса. Как следует иа описания работы устройства длительность цикла работы прв образователя является величиной постоянной и равной T.i.() -t , где t. - период частоты следования тактовых импульсов генератора wvпульсов. В общем случае длительность времени цикла преобразователя составляет где п - разрядность датчика 1; (Г)-2-Х) - число старших раарадов датчика 1, по которым, производится вычисление функции в начале 1- -го участка аппроксимации; число младших разрядов датчика 1, по которым производится вычисление приращения функции на j -ом участке аппроксимации; число участка аппроксимании. Технико-экономическая эффективность изобретения заключается в том, что предлагаемый преобразователь кода угла в код синуса и код косинуса не сложнее прототи па, но имеет более высокую точность и быстродействие, что позволяет его исполь зовать в качестве легкоканального преобразователя. Применение изобретения позволит повы сить точность и скорость обработки инфор мации. , Формула изобретения Преобразователь кода угла в коды сину са и косинуса, содержащий датчик д -раэ рядного кода, выходы младших разрядов которого соединены со входами первого коммутатора кодов, а выходы старших раз рядов - со входами блока определения знака косинуса, цифровой компаратор, эа поминающее устройство с ft -2-К адресны ми выходами, счетчик, импульсов множительный блок и генератор импульсов, о т личаю-шийся тем, что, с целью повышения точности и быстродействия пре образователя, в него введены сумматор и блок синхронизации, выходы К младших разрядов первого коммутатора кодов соединены со входами второго сомножителя множительного блока, остальные выходы первого коммутатора соединены со входами первого кода цифрового компаратора, входы второго кода которого объединены с адресными входами запоминающего устройства и подключены к выходам счетчика импульсов, К + 1 выходов запоминающего устройства соединены со входами первого Сомножителя множительного блсжа и с одним из входов второго коммутатора кодов, другие входы которого соединены с выходами множительного блока, выходы второго коммутатора кодов соединены со входами сумматора, выход цифрового компаратора подключен к управляющему входу второго коммутатора кодов и к одному из входов блока синхронизации, другие входы которого соединеныс выходами генератора импульсов и с выходом одного из старших разрядов датчика rt -разрядного кода, один КЗ выходов блока синхронизации соединен с установочными входами сумматора и счетчика импульсов, второй - со счетными входами счетчика импульсов и тактовым входом сумматора, третий выход блока синхронизации соединен с управляющим входом первого коммутатора кодов, а чет вертьА выход - с входом коррекции множительного блока. Источники информапни, принятые во Мимакие нри экспертизе 1.Патент США № 3813528, кл. 235-152, 1972. 2.Авторское свидетельство СССР № 369448, кл. Н 03 К 5/156 1970, (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь кода угла | 1978 |

|

SU716042A1 |

| Цифровой генератор функций | 1989 |

|

SU1663607A1 |

| Цифровой вычислитель функций | 1986 |

|

SU1354187A1 |

| Цифровой синусно-косинусный преобразователь | 1977 |

|

SU780174A1 |

| Цифровой функциональный преобразователь | 1977 |

|

SU742947A1 |

| Синусно-косинусный функциональный преобразователь | 1981 |

|

SU970357A1 |

| Цифровой синусно-косинусный преобразователь | 1978 |

|

SU800923A1 |

| Синусно-косинусный преобразователь | 1986 |

|

SU1327095A1 |

| Цифровой преобразователь координат | 1977 |

|

SU742944A1 |

| Синусно-косинусный преобразователь | 1986 |

|

SU1302273A1 |

Авторы

Даты

1979-09-05—Публикация

1977-05-04—Подача