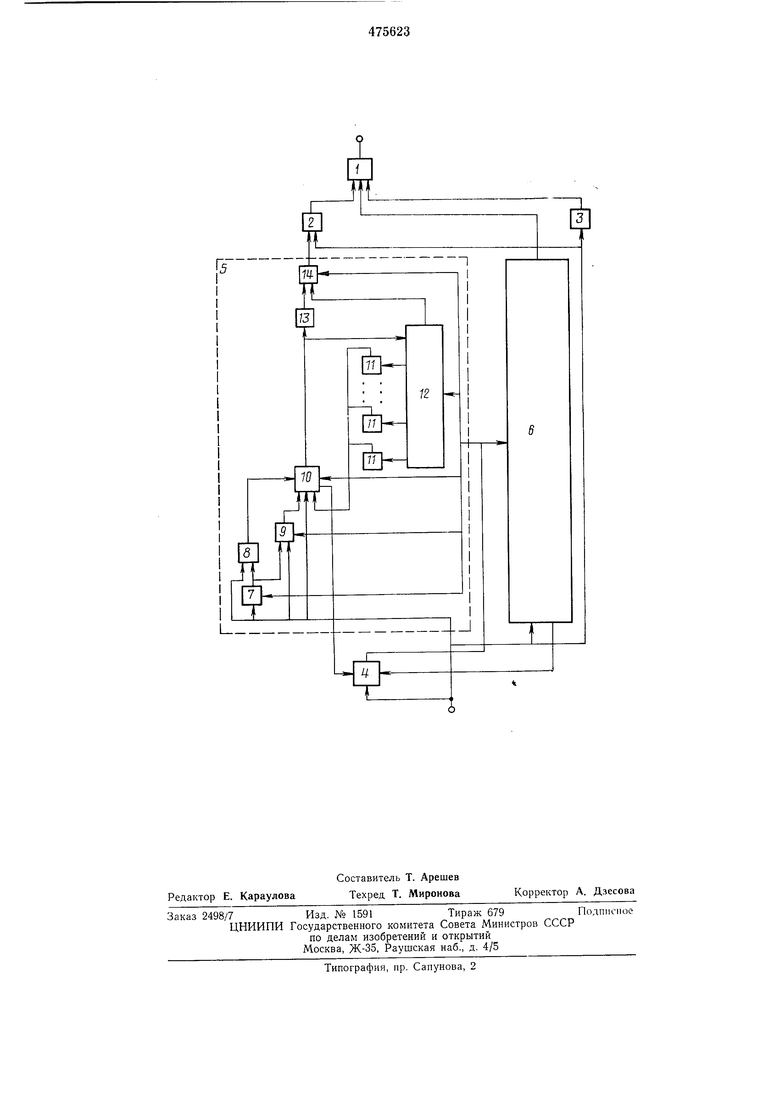

ми соответствующих регистров накопителя на регистрах, управляющий вход блока формирования индексов соединен с управляющими входами схемы «ИЛИ, накопителя на регистрах, распределителя сигналов, управляемого дешифратора, вычитателя, информационный вход блока формирования индексов соединен с информационными входами дешифратора, вычитателя, управляемого дешифратора, распределителя сигналов. На чертеже изображена схема предлагаемого устройства для формирования адресов. Устройство содержит сумматор 1, блок умножения 2, блок вычитания 3, схему управления 4, блоки 5 и 6 формирования индексов соответственно по первой и второй координатам. Каждый блок формирования индексов содержит вычитатель 7, дешифратор 8, управляемый дешифратор 9, распределитель сигналов 10, схемы 11 анализа нулевого содержимого регистров, накопитель 12 на регистрах, шифратор 13 и схему «ИЛИ 14. Устройство работает следующим образом. Адрес Aij элемента матрицы чисел с индексамиij(ie {1, 2,.... п,, JQ {1,2,..., /г,)) формируется на выходе сумматора 1 в результате суммирования адреса а первого элемента неискаженной матрицы размера и составляющих по координатам в соответствии с выражением An--a + n(i-)+(j-) (a-n) «г + УВеличины i и / вырабатываются на информационных выходах блоков 5 и 6 формирования индексов соответственно. Произведение формируется блоком умножения 2, а величина () - блоком вычитания 3. Блоки 5 и 6 аналогичны по составу и принципу действия. В состав этих блоков входит распределитель сигналов 10, на входы которого поступают логические векторы (двоичные слова) с выходов схем 11 анализа нулевого содержимого регистров, с информационного входа блока и с выхода управляемого дешифратора 9. На выходах распределителя сигналов 10 формируется последовательность чисел в коде «J из «Л. Отсчет номеров выходов производится слева направо. Нри подаче управляющего воздействия единица на выходе распределителя 10 может смещаться вправо (влево) на любое количество позиций с учетом циклической связи крайних разрядов распределителя. Закон смещения единицы па выходах распределителя определяется соответствующим логическим вектором, зафиксированным на его входах. Единицы возбуждаются только на тех выходах распределителя 10, которые соответствуют позициям логического вектора, содержащим «1. Код, задающий состояние, начиная с которого осуществляется формирование последовательности состояний Б распределителе 10, поступает с дешифратора 8. При выполнении различных индексных операций языка APL блок 5 формирования индексов работает следующим образом. Индексирование. Перед началом выполнения операции регистры накопителя 12 сигналом со схемы управления 4 устанавливаются в нулевое состояние, после чего в них засылаются соответствующие индексы. Закон смещения «1 на выходе распределителя сигпалов 10 определяется правильным логическим вектором, сформированным на выходах схем 11 анализа нулевого содержимого регистров (с учетом инвертирования). Код с выхода дешифратора 8 обеспечивает в-начале работы распределителя 10 возбуждение «1 на первом его выходе. В результате воздействия импульсных сигналов со схемы управления 4 распределитель 10 осуществляет последовательную адресацию регистров накопителя 12 по чтению, начиная с первого регистра. Вследствие этого из регистров извлекаются индексы, которые через схему «ИЛИ 14 поступают на выход блока. После того как из накопителя 12 на регистрах выбраны все индексы, в распределителе 10 формируется сигнал, который поступает в схему управления 4 и влечет за собой окончание операции. Сжатие. При этой операции закон смеп;ения «1 на выходе распределителя сигналов 10 определяется логическим вектором, поступающим в него с информационного входа блока. Код, формирующийся на выходе дешифратора 8, обеспечивает в начале работы распределителя 10 возбуждение «1 на том его выходе, который соответствует позиции крайней левой единицы в логическом векторе. В результате воздействия импульсных сигналов со схемы управления 4 на выходе распределителя 10 формируются числа в коде -«1 из «Л, поступающие на вход шифратора 13. С выхода шифратора двоичный код, соответствующий положению «1 в числе на выходе распределителя 10, через схему «ИЛИ 14 передается на выход блока. После того как на выходе распределителя 10 сформированы все числа, соответствующие единицам в логическом векторе, вырабатывается сигнал, поступающий в схему управления 4 и обусловливающий окончание операции. Реверс. Закон смещения «1 на выходе распределителя сигналов 10 в данном случае определяется правильным логическим вектором, сформированным на выходе управляемого дешифратора 9. Этот дешифратор осуществляет преобразование двоичных чисел, соответствующих номерам первой и последней единицы, в правильный логический вектор. Под правильным логическим вектором размера k понимается слово, содержащее k символов, представленных в алфавите {О, 1}, причем символы «1 образуют единственную группу, в которой между первым и последним символом «1 отсутствуют символы «о (например

001110, ООП). Правильный логический вектор может быть задан двумя числами: номером первой единицы вектора и номером последней единицы. Номера отсчитываются слева направо. В рассматриваемом случае номер первой единицы вектора равен единице, а номер последней единицы - П1. Значение признака реверса обеспечивает сдвиг «1 на выходе распределителя 10 влево. Код на выходе дешифратора 8 обеспечивает в начале работы распределителя возбуждение «1 на том его выходе, который соответствует позиции крайней правой единицы в правильном логическом векторе. В результате воздействия импульсных сигналов со схемы управления 4 на выходе распределителя 10 формируются числа, поступающие на вход шифратора 13. В дальнейшем блок работает так же, как и в случае операции сжатия.

Выбор. При выполнении рассматриваемой индексной операции формируется последовательность из Vi первых (если ) или последних (если tl 0) индексов по координате. В этом режиме работы закон смещения «1 на выходе распределителя сигналов 10 определяется правильным логическим вектором, сформированным на выходе управляемого дешифратора 9. Если , то номер первой единицы вектора равен единице, а номер последней- Vi.

Если , то номер первой единицы вектора равен (п1- -1}-U, а номер последней - rti. Величина («i + l)-fi вырабатывается вычитателем 7. Код, формирующийся на выходе дешифратора 8, обеспечивает в начале работы распределителя 10 возбуждение «1 на том его выходе, который соответствует позиции крайней левой единицы в правильном логическом векторе. В результате воздействия импульсных сигналов со схемы управления 4 на выходе распределителя 10 формируются числа в коде «1 из «N. В дальнейшем блок работает так же, как и в случае операции сжатия.

Отбрасывание. При выполнении рассматриваемой индексной операции формируется последовательность из (ni-Vi) первых (если ) или () последних (если ) индексов по координате. В этом режиме работы закон смещения «I на выходе распределителя 10 сигналов определяется правильным логическим вектором, сформированным на выходе управляющего дешифратора 9. Если , то номер первой единицы вектора равен единице, а номер последней- («i-Oi). Если , то номер первой единицы вектора равен (ui + 1), а номер последней - «i. Величины («1-vi} и (ui + l) вырабатываются вычитателем 7. Код, формирующийся на выходе дешифратора 8, обеспечивает в начале работы распределителя 10 возбуждение «1 на том его выходе, который соответствует позиции крайней левойединицы в правильном логическом векторе. В последующем блок работает так же, как и в случае операции сжатия.

Циклический сдвиг. В данном случае закон смещения «1 на выходе распределителя 10 сигналов задается правильным логическим вектором, сформированным на выходе управляемого дешифратора 9. Номер первой единицы вектора равен единице, а номер последней-HI. На вход дешифратора 8 поступает либо величина v, сдвига индексов по координате (если ), либо величина (tii-У) (если ). Величина («i-Vi) вырабатывается вычитателем 7. Код, формирующийся на выходе дешифратора 8, обеспечивает в начале работы распределителя 10 возбуждение на (tii-j-l)-M его выходе (если ), либо на («1-t)i+I)-M выходе (еслии1 0).

В результате воздействия импульсных сигналов со схемы управления 4 на выходе распределителя 10 формируются числа в коде «1 из «jV, поступающие на вход шифратора 13. В дальнейшем блок работает так же, как и в случае операции сжатия.

Схема управления 4 организует совместную работу блоков 5 и 6 формирования индексов по первой и второй координатам. Если адреса элементов матрицы формируются в результате «сканирования по строкам (по первой координате), то для каждого значения индекса по первой координате, формирующегося на выходе блока 5, производится формирование последовательности индексов по второй координате на выходе блока б. Изменение информации на выходе блока 5 осуществляется после выработки всех индексов по второй координате. При реализации операции «Транспозиция типа 21А осуществляется «сканирование матрицы по столбцам (по второй кооодинате). В этом случае для каждого значения индекса по второй координате, формирующегося на выходе блока 6, производится формирование последовательности индексов по первой координате на выходе блока 5. Изменение информации на выходе блока 6 осуществляется после выработки всех индексов по первой координате. При реализации операции «Транспозиция типа ПА формирование индексов по первой и второй координатам осуществляется одновременно. При выполнении операции «Формирование значения п и п, поступающие в блоки 5 и 6, определяются не параметрами неискаженного массива, а задаются в индексной операции. Операция «Выписывание представляет собой частный случай операции «Формирование, когда производный массив является вектором размера ni-n.

Предмет изобретения

1. Устройство для формирования адресов, содержащее сумматор, выход которого соединен с выходом устройства, отличающеес я тем, что, с целью расширения функциональных возможностей, в него введены блок умножения, блок вычитания, схема управления и блоки формирования индексов, причем первый вход сумматора соединен с выходом

олока умножения, один из входов которого соединен с информационным выходом одного из блоков формирования индексов, второй вход сумматора подсоединен к информационному выходу другого блока формирования индексов, третий вход сумматора соединен с выходом блока вычитания, управляющие входы блоков формирования индексов подсоединены к выходу схемы управления, два входа которой связаны с управляющими выходами блоков формирования индексов, а второй вход блока умножения, вход блока вычитания, третий вход схемы управления и информационные входы блоков формирования индексов подсоединены к входу устройства.

2. Устройство по и. 1, отличающееся тем, что блок формирования индексов содержит схему «ИЛИ, шифратор, накопитель на регистрах, схемы анализа нулевого содержимого регистров, распределитель сигналов, дешифратор, управляемый дешифратор, вычитатель, причем к информационному выходу блока формирования индексов подсоединен выход схемы «ИЛИ, первый вход которой соединен с выходом шифратора, входом соединенного с первым выходом распределителя сигналов и с адресным входом накопителя на регистрах, выход которого соединен с вторым входом схемы «ИЛИ, управляющий выход блока формирования индексов подсоединен к второму выходу распределителя сигналов, лервый и второй входы которого связаны с выходами дешифратора и управляемого дешифратора соответственно, первые входы которых связаны с выходом вычитателя, информационный вход распределителя сигналов соединен с выходами схем анализа нулевого содержнмого регистров, входы которых соединены с выходами соответствуюших регистров накопителя на регистрах, унравляюший вход блока формирования индексов соединен с унравляю1цими входами схемы «ИЛИ, наконителя на регистрах, распределителя сигналов, управляемого дешифратора, вычитателя, информационной вход блока формирования индексов соединен с информационными входами дешифратора, вычитателя, управляемого дешифратора, распределителя сигналов.

Г5

| название | год | авторы | номер документа |

|---|---|---|---|

| Конвейерное вычислительное устройство | 1987 |

|

SU1432512A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ В ТРОИЧНОЙ СИСТЕМЕ СЧИСЛЕНИЯ НА НЕЙРОНАХ | 2010 |

|

RU2453900C2 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1997 |

|

RU2116670C1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ С ИНТЕГРИРОВАННЫМИ МЯГКИМИ И ЖЕСТКИМИ РЕШЕНИЯМИ | 2011 |

|

RU2450464C1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ С МЯГКИМИ РЕШЕНИЯМИ | 2010 |

|

RU2428801C1 |

| Генератор случайного марковского процесса | 1989 |

|

SU1619263A1 |

| Устройство для извлечения квадратного корня | 1985 |

|

SU1259257A1 |

| Устройство для преобразования координат | 1980 |

|

SU898426A1 |

| Устройство для трансляции логических адресов в адреса памяти на магнитных дисках | 1981 |

|

SU966695A1 |

| Устройство для формирования изображений на экране электронно-лучевой трубки (ЭЛТ) | 1981 |

|

SU1032447A1 |

Авторы

Даты

1975-06-30—Публикация

1973-03-02—Подача