Изобретение относится к вычислительной технике, предназначено для извлечения квадратного корня и может быть использовано в высокопроизводительных специализированных вычислительных устройствах.

Целью изобретения является повышение быстродействия устройства.

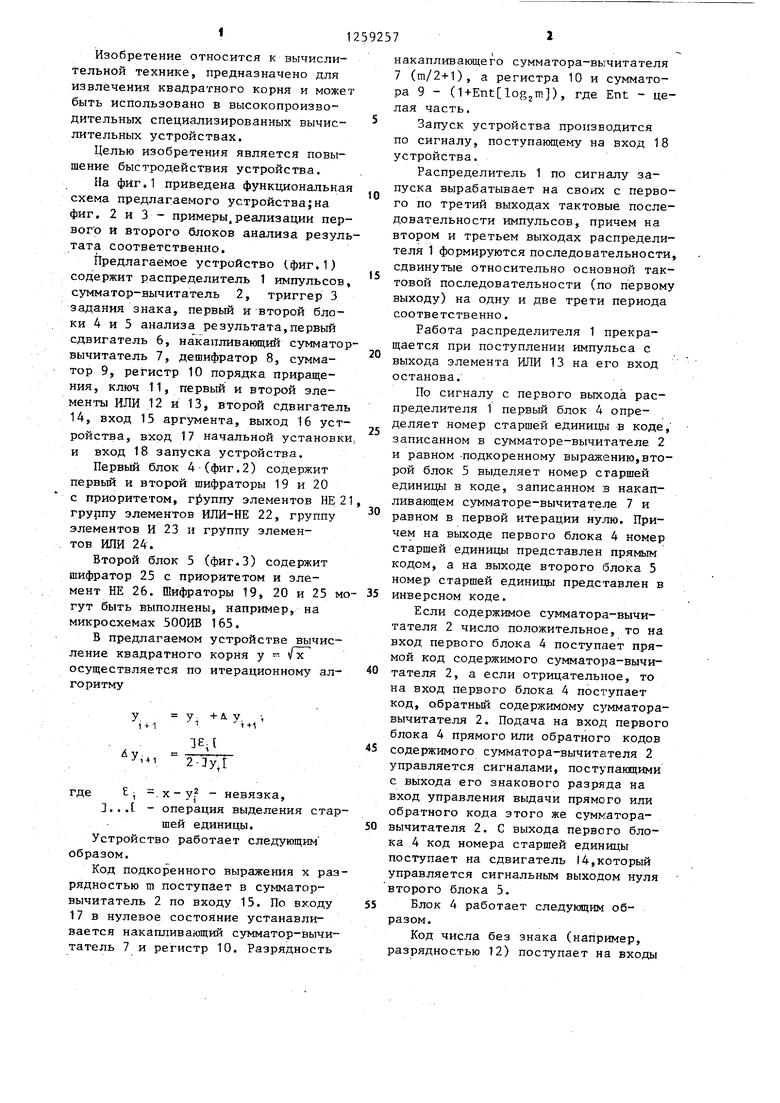

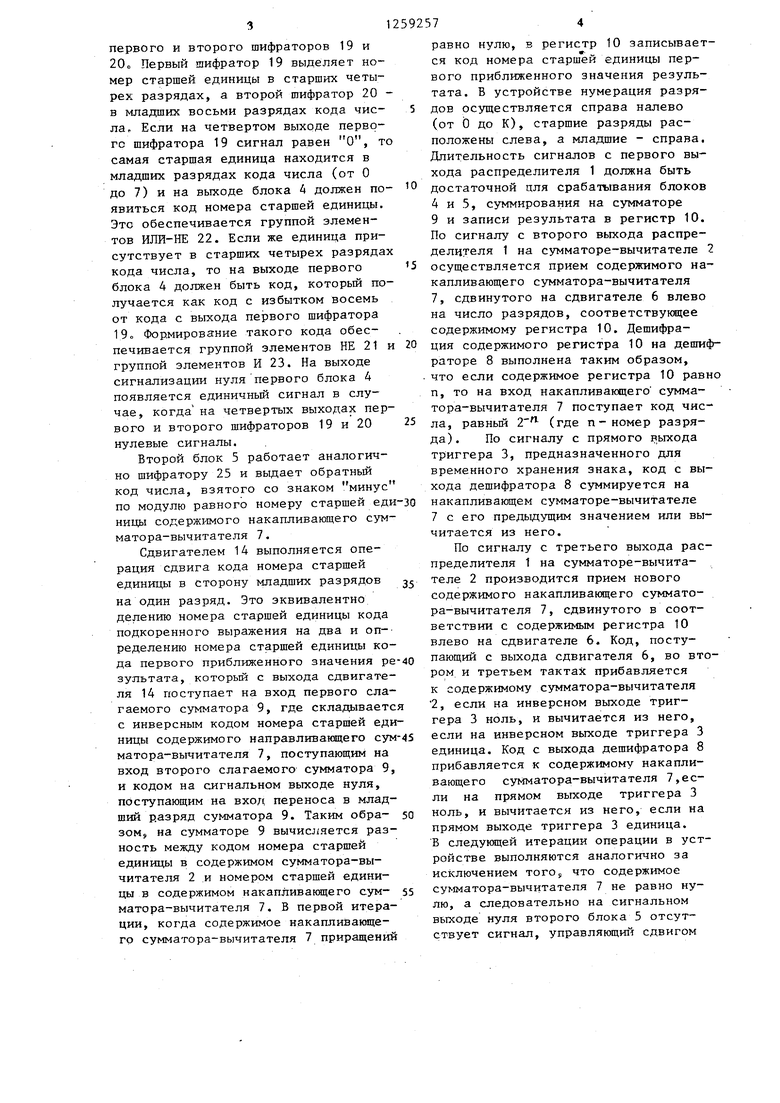

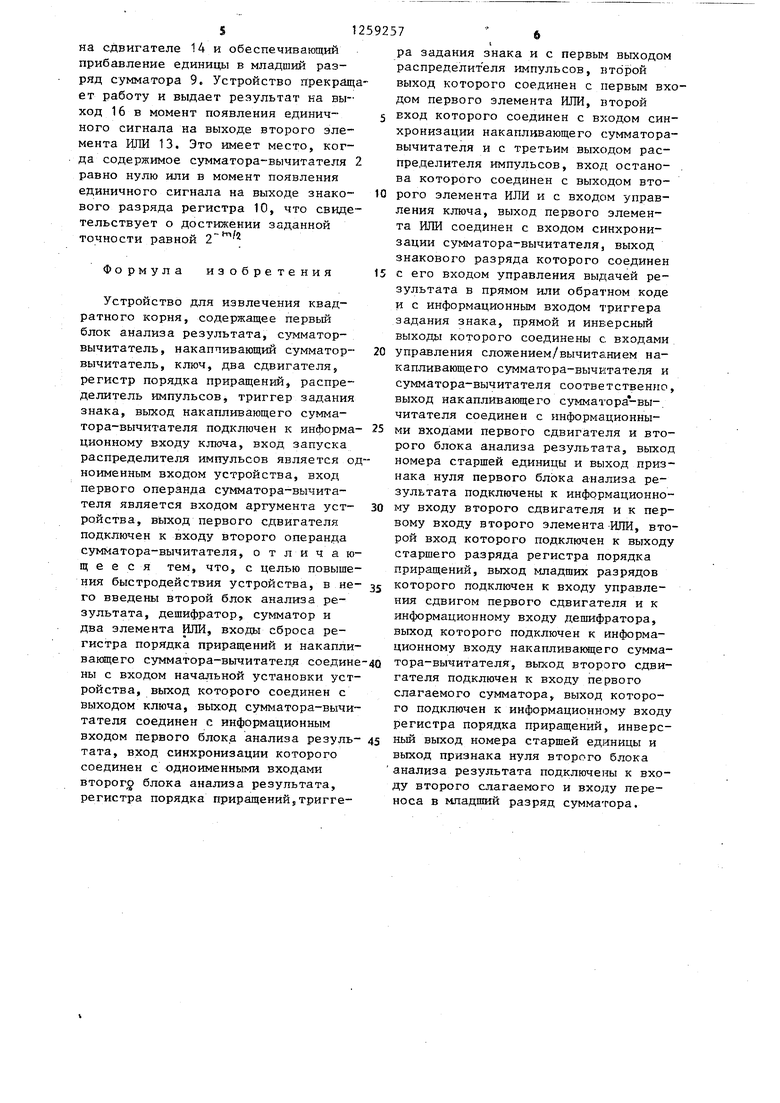

На фиг.1 приведена функциональная схема предлагаемого устройства;на фиг. 2 и 3 - примеры,реализации пер- вог о и второго блоков анализа результата соответственно.

Предлагаемое устройство (.фиг.1) содержит распределитель 1 импульсов, сумматор-вычитатель 2, триггер 3 задания знака, первый и второй блоки 4 и 5 анализа результата,первый сдвигатель 6, накапливаниций сумматор вычитатель 7, дешифратор 8, сумматор 9, регистр 10 порядка приращения, ключ 11, первый и второй элементы ИЛИ 12 и 13, второй сдвигатель 14, вход 15 аргумента, выход 16 устройства, вход 17 начальной установки и вход 18 запуска устройства.

Первьш блок 4 (фиг.2) содержит первый и второй шифраторы 19 и 20 с приоритетом, группу элементов НЕ 2 группу элементов ИЛИ-НЕ 22, группу элементов И 23 и группу элементов ИЛИ 24.

Второй блок 5 (фиг.З) содержит шифратор 25 с приоритетом и элемент НЕ 26. Шифраторы 19, 20 и 25 мо гут быть выполнены, например, на микросхемах 500ИВ 165.

В предлагаемом устройства вычисление квадратного корня у - vx осуществляется по итерационному алгоритму

У , +Д. у

,

1 +1

2-Зу,Г

где

Е, .x-yf

невязка.

Л,.. - операция выделения старшей единицы.

Устройство работает следующим образом.

Код подкоренного выражения х разрядностью m поступает в сумматор- вычитатель 2 по входу 15. По входу 17 в нулевое состояние устанавливается накапливающий сумматор-вычитатель 7 и регистр 10. Разрядность

10

(5

20

25

30

35

40

45

50

55

накапливающего сумматора-вычитателя 7 (m/2+l), а регистра 10 и сумматора 9 - (1+Ent logjtn), где Ent - целая часть.

Запуск устройства производится по сигналу, поступающему на вход 18 устройства.

Распределитель 1 по сигналу запуска вырабатывает на своих с первого по третий выходах тактовые последовательности импульсов, причем на втором и третьем выходах распределителя i формируются последовательности, сдвинутые относительно основной тактовой последовательности (по первому выходу) на одну и две трети периода соответственно.

Работа распределителя 1 прекращается при поступлении импульса с выхода элемента ИЛИ 13 на его вход останова.

По сигналу с первого выхода распределителя 1 первый блок 4 определяет номер старшей единицы -в коде, записанном в сумматоре-вычитателе 2 и равном -подкоренному выражению,второй блок 5 выделяет номер старшей единицы в коде, записанном в накапливающем сумматоре-вычитателе 7 и равном в первой итерации нулю. Причем на выходе первого блока 4 номер старшей единии;ы представлен прямым кодом, а на выходе второго блока 5 номер старшей единицы представлен в инверсном коде.

Если содержимое сумматора-вычитателя 2 число положительное, то на вход первого блока 4 поступает прямой код содержимого сумматора-вычитателя 2, а если отрицательное, то на вход первого блока 4 поступает код, обратньм содержимому сумматора- вычитателя 2i Подача на вход первого блока 4 прямого или обратного кодов содержимого сумматора-вычитателя 2 управляется сигналами, поступакщими с выхода его знакового разряда на вход управления выдачи прямого или обратного кода этого же сумматора- вычитателя 2. С выхода первого блока 4 код номера старшей единицы поступает на сдвигатель 14,который управляется сигнальным выходом нуля второго блока 5.

Блок 4 работает следующим образом.

Код числа без знака (например, разрядностью 12) поступает на входы

первого и второго шифраторов 19 и 20о Первый шифратор 19 выделяет номер старшей единицы в старших четырех разрядах, а второй шифратор 20 - в младших восьми разрядах кода чис- ла. Если на четвертом выходе первого шифратора 19 сигнал равен О, то самая старшая единица находится в младших разрядах кода числа (от О до 7) и на выходе блока А должен по- явиться код номера старшей единицы. Это обеспечивается группой элементов ИЛй-НЕ 22. Если же единица присутствует в старших четырех разрядах кода числа, то на выходе первого блока А должен быть код, который получается как код с избытком восемь от кода с выхода первого шифратора 19о Формировагние такого кода обеспечивается группой элементов НЕ 21 и группой элементов И 23, На выходе сигнализации нуля первого блока А появляется единичный сигнал в слу- чае, когда на четвертых выходах первого и второго шифраторов 19 и 20 нулевые сигналы.

Второй блок 5 работает аналогично шифратору 25 и вьщает обратный код числа, взятого со знаком минус по модулю равного номеру старшей еди ницы содержимого накапливающего сум- матора-вычитателя 7.

Сдвигателем 1А выполняется операция сдвига кода номера старшей единицы в сторону младших разрядов на один разряд. Это эквивалентно делению номера старшей единицы кода подкоренного выражения на два и оп-- ределению номера старшей единицы кода первого приближенного значения ре зультата, который с выхода сдвигате- ля 1А поступает на вход первого слагаемого сумматора 9, где складываетс с инверсным кодом номера старшей единицы содержимого направливанщего cyM матора-вычитателя 7, поступающим на вход второго слагаемого сумматора 9, и кодом на сигнальном выходе нуля, поступающим на вход переноса в младший разряд сумматора 9. Таким обра- зом, на сумматоре 9 вычис:;яется разность между кодом номера старшей единицы в содержимом сумматора-вы- читателя 2 и номером старшей единицы в содержимом накапливающего сум- матора-вычитателя 7. В первой итерации, когда содержимое накапливающего сумматора-вычитателя 7 приращений

равно нулю, в регистр 10 записывается код номера старшей единицы первого приближенного значения результата. В устройстве нумерация разрядов осуществляется справа налево (от О до К), старшие разряды расположены слева, а младшие - справа. Длительность сигналов с первого выхода распределителя 1 должна быть достаточной цля срабатывания блоков А и 5, суммирования на сумматоре 9 и записи результата в регистр 10. По сигналу с второго выхода распределителя 1 на сумматоре-вычитателе осуществляется прием содержимого накапливающего сумматора-вычитателя 7, сдвинутого на сдвигателе 6 влево на число разрядов, соответствующее содержимому регистра 10. Дешифрация содержимого регистра 10 на дешираторе 8 выполнена таким образом, . что если содержимое регистра 10 рав п, то на вход накапливающего сумматора-вычитателя 7 поступает код числа, равньш (где п - номер разряда). По сигналу с прямого в гхода триггера 3, предназначенного для временного хранения знака, код с выхода дешифратора 8 суммируется на накапливающем сумматоре-вычитателе

7с его предыдущим значением или вычитается из него.

По сигналу с третьего выхода распределителя 1 на сумматоре-вычитателе 2 производится прием нового содержимого накапливающего сумматора-вычитателя 7, сдвинутого в соответствии с содержимым регистра 10 влево на сдвигателе 6. Код, поступающий с выхода сдвигателя 6, во втором и третьем тактах прибавляется к содержимому сумматора-вычитателя 2, если на инверсном выходе триггера 3 ноль, и вычитается из него, если на инверсном выходе триггера 3 единица. Код с выхода дешифратора 8 прибавляется к содержимому накапливающего сумматора-вычитателя 7,если на прямом выходе триггера 3 ноль, и вычитается из него, если на прямом выходе триггера 3 единица,

8следующей итерации операции в устройстве выполняются аналогично за исключением того что содержимое сумматора-вычитателя 7 не равно нулю, а следовательно на сигнальном выходе нуля второго блока 5 отсутствует сигнал, управляющий сдвигом

5

на сдвигателе 14 и обеспечивающий прибавление единицы в младший разряд сумматора 9. Устройство прекращет работу и выдает результат на выход 16 в момент появления единичного сигнала на выходе второго элемента ИЛИ 13. Это имеет место, когда содержимое сумматора-вычитателя равно нулю или в момент появления единичного сигнала на выходе знакового разряда регистра 10, что свидетельствует о достижении заданной точности равной

Формула изобретения

Устройство для извлечения квадратного корня, содержащее первый блок анализа результата, сумматор- вычитатель, накативающий сумматор- вычитатель, ключ, два сдвигателя, регистр порядка приращений, распределитель импульсов, триггер задания знака, выход накапливающего сумматора-вычитателя подключен к информа- 25 ми входами первого сдвигателя и втоционному входу ключа, вход запуска распределителя импульсов является одноименным входом устройства, вход первого операнда сумматора-вычитателя является входом аргумента уст- ройства, выход первого сдвигателя подключен к входу второго операнда сумматора-вычитателя, отличающееся тем, что, с целью повышения быстродействия устройства, в не- го введены второй блок анализа результата, дешифратор, сумматор и два элемента ИЖ, входы сброса регистра порядка приращений и накапливающего сумматора-вычитатедя соедине ны с входом начальной установки устройства, выход которого соединен с выходом ключа, выход сумматора-вычитателя соединен с информационным входом первого блока анализа резуль- тата, вход синхронизации которого соединен с одноименными входами BToporg блока анализа результата, регистра порядка приращений,тригге6

ра задания знака и с первым выходом распределителя импульсов, выход которого соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с входом синхронизации накапливающего сумматора- вычитателя и с третьим выходом распределителя импульсов, вход остано- . ва которого соединен с выходом второго элемента ИЛИ и с входом управления ключа, выход первого элемента ИЖ соединен с входом синхронизации сумматора-вычитателя, выход знакового разряда которого соединен

с его входом управления выдачей результата в прямом или обратном коде и с информационным входом триггера задания знака, прямой и инверсный выходы которого соединены с входами

управления сложением/вычитанием накапливающего сумматора-вычитателя и сумматора-вычитателя соответствен}1о, выход накапливающего сумматора -вы-. читателя соединен с информационнырого блока анализа результата, выход номера старшей единицы и выход признака нуля первого блока анализа результата подключены к информационному входу второго сдвигателя и к первому входу второго элемента ИЛИ, второй вход которого подключен к выходу старшего разряда регистра порядка приращений, выход младших разрядов которого подключен к входу управления сдвигом первого сдвигателя и к информационному входу дешифратора, выход которого подключен к информационному входу накапливакицего сумматора-вычитателя, выход второго сдвигателя подключен к входу первого слагаемого сумматора, выход которого подключен к информационному входу регистра порядка приращений, инверсный выход номера старшей единицы и выход признака нуля второго блока анализа результата подключены к входу второго слагаемого и входу переноса в младший разряд сумматора.

2

Редактор О. Юрковецкая

Составитель А. Ушаков

Техред И.Попович Корректор Т.Колб

5122/46

Тираж 671 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,4

Риг,.3

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления квадратного корня | 1984 |

|

SU1264167A1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГАРИФМА | 1991 |

|

RU2006916C1 |

| Аналого-цифровой инкрементный умножитель | 1982 |

|

SU1057971A1 |

| Устройство для вычисления @ | 1983 |

|

SU1156067A1 |

| УСТРОЙСТВО СОВМЕСТНОГО КОДИРОВАНИЯ ГРАНИЦ ПРИ ИНТЕРВАЛЬНЫХ ВЫЧИСЛЕНИЯХ | 2012 |

|

RU2497180C1 |

| Преобразователь двоичных чисел в двоично-десятичные числа | 1980 |

|

SU941990A1 |

| Устройство для вычисления элементарных функций по алгоритму Волдера | 1982 |

|

SU1068933A1 |

| Устройство для обработки данных | 1987 |

|

SU1513443A1 |

Изобретение относится к облас- . ти вычислительной техники и позволя- ет сократить время итерационных вычислений значения квадратного корня. Устройство содержит распределитель импульсов, сумматор-вычитатель,триггер задания знака, первый и второй блоки анализа результата, первый и второй сдвигатели, накапливающий сумматор-вычитатель, дешифратор, сумматор, регистр порядка приращения,ключ, первый и второй элементы ИЛИ. Блоки анализа результата выделяют номер старшей единицы в поступающих на них кодах. 3 ил. с (О (Л С

| Оранский A.M | |||

| Аппаратурные методы в цифровой вычислительной тех- нике | |||

| Минск: Изд-во ВГУ им | |||

| В.И | |||

| Ленина, 1977, с, 147, рис | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Интегральные микросхемы: Справочник /Под ред | |||

| Б.В | |||

| Тарабрина | |||

| Изд | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| - М.; Энергоатомиз- дат, 1985, с | |||

| Кран машиниста для автоматических тормозов с сжатым воздухом | 1921 |

|

SU194A1 |

| Устройство для извлечения квадратного корня | 1978 |

|

SU732863A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-23—Публикация

1985-01-23—Подача