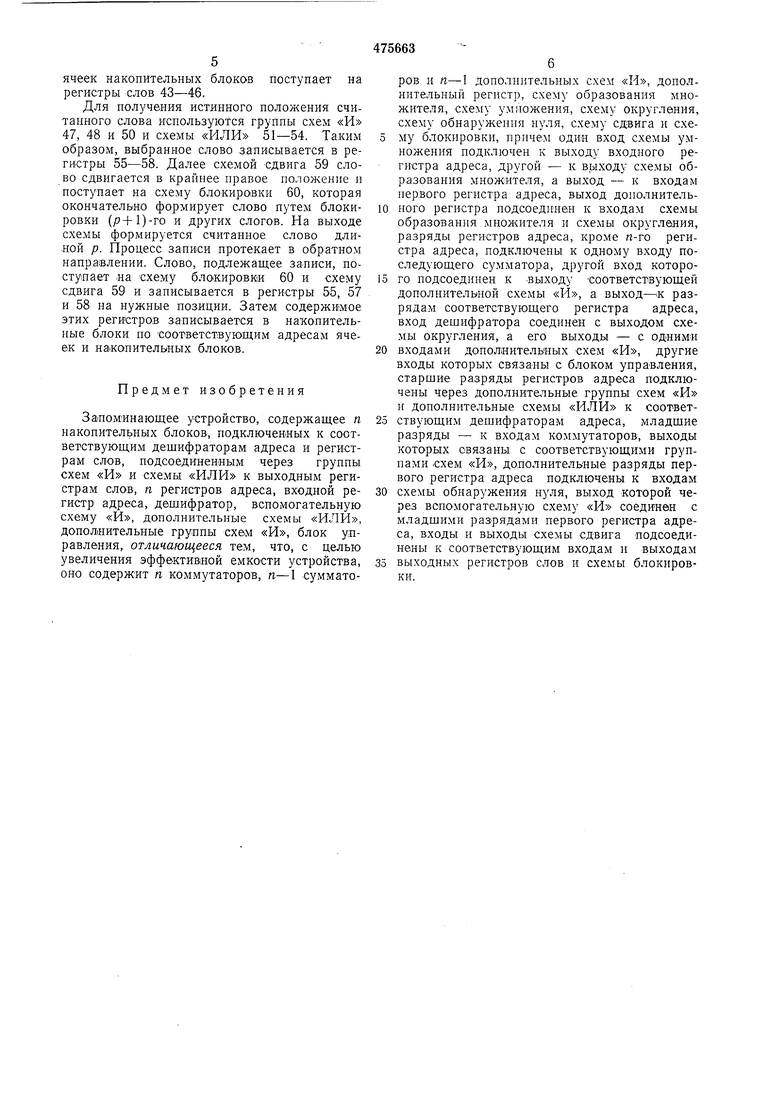

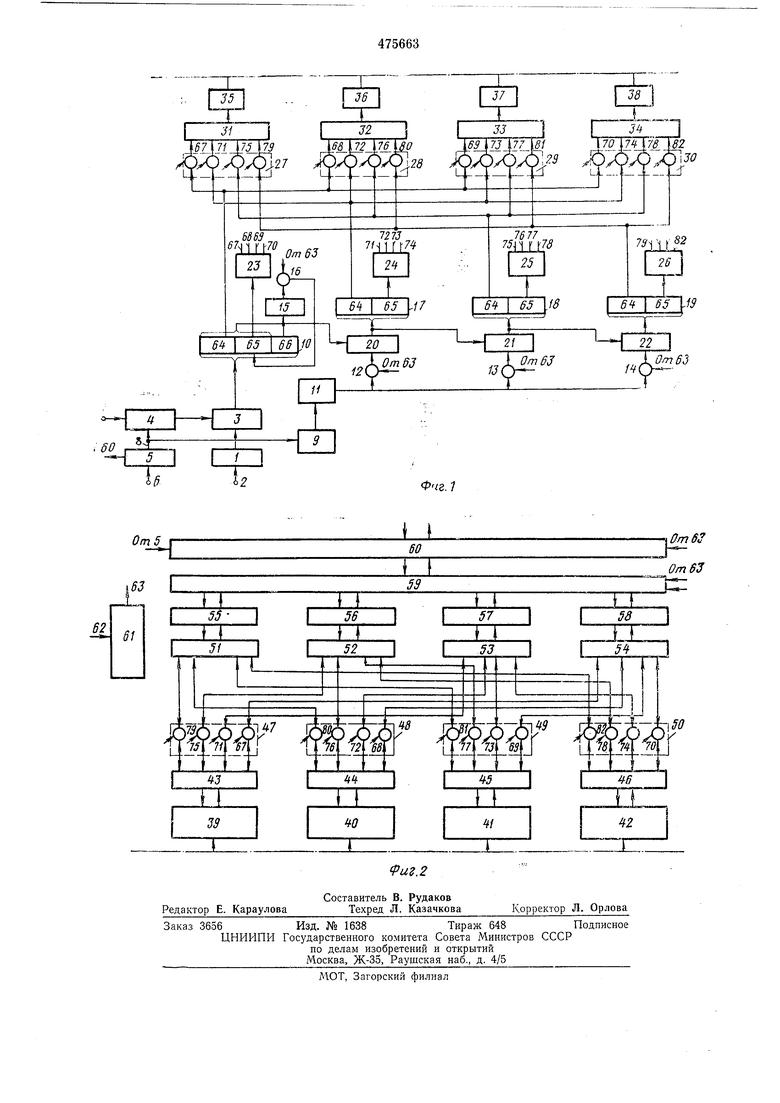

дополнительного регистра 5, имеющего вход 6. Схема образования множителя имеет также информационный вход 7. Выход 8 регистра 5 связан с входом схемы округления 9 (в сторону меньшего целого числа). Выход схемы 3 подсоединен к первому регистру адреса 10. Выход схемы 9 соединен с входом дешифратора 11, выходы которого связаны с входами дополнительных схем «И 12, 13 и 14. Выход схемы 15 обнаружения нуля подсоединен к одному из входов вспомогательиой схемы «PI 16. Разряды регистров адреса 17-19 подключены к выходам соответствуюндих сумматоров 20-22, одни входы которых подсоединены к выходам схем «И 12-14. Устройство содержит также коммутаторы 23-26, допол«нтельные группы схем «И 27-30, дополнительные схемы «ИЛИ 31-34, дешифраторы адреса 35-38, наконительные блоки 39-42, связанные с регистрами слов 43-46, подключенными через грунны схем «И 47-50 и схемы «ИЛИ 51-54 к выходным регистрам слов 55-58, схему сдвига 59, схему блокировки 60, блок управления 61, имеющий вход 62 и выход 63. Регистры адреса 10, 17, 18 и 19 содержат старщие 64 и младшие 65 разряды, а регистр 10, кроме того, и дополнительные разряды 66, которые подключены к входу схемы 15. Выход схемы «И 16 связан с разрядами 65 регистра адреса 10. Разряды 65 регистров 10, 17, 18 и 19 иодключены соответственно к коммутаторам 23-26. Разряды 64 регистров 10, 17, 18 и 19 нодсоединены через группы схем «И 27-30 и схемы «ИЛИ 31-34 к дешифраторам адреса 35-38, связанным с накопительными блоками 39-42. Входы и выходы схемы сдвига 59 подсоединены к соответствующим входам и выходам выходных регистров слов 55-58 и схемы блокировки 60. Один из входов схем «PI 12-14 связан с блоком управления 61. Разряды 64 и 65 регистра адреса 10 подключеиы к одному из входов сумматора 20. Выход каждого сумматора, кроме сумматора 22, подключен к входу последующего. Выходы 67-82 коммутаторов 23-26 подключены к входам соответствующих групп схем «И 27-30 и 47-50. Устройство работает следующим образом. Поиск нужной ячейки накопительного блока как при записи, так и при чтении осуществляется путем задания ее математического адреса А„ . Пусть длина слова в слогах равна р, а длина ячейки на копительиого блока /г, тогда коэффициент удлинения Поскольку заданный адрес не является физическим, то для его нолучения пользуются соотношением между Л„ , коэффициентом удлинения р н количеством накопительных блоков п: При обращении к устройству на вход 2 регистра 1 подается код адреса слова А, , на вход 6 регистра 5-код коэффициента удлинения р. На входе 7 схема 4 имеет постоянную величину - обратную числу иаконительпых блоков в устройстве ( - ). На выходе схемы 4 образуется код выражения--- . На входе схемы 3, согласно вырал :внию (2), получается значение Аф , которое поступает на входы регистра 10. Значение округляется в схеме 9, и через дешифратор И происходит подготовка к обращению в другие накопительные блоки. Адрес любого слова разделяется условно па три частн, номещаемые в разряды 64, 65 и 66. Первая часть является адресом ячейки накопительного блока, вторая часть - номером позиции, которую занимает последний слог слова, третья часть - номером накопительного блока, в котором хранится данный слог. Поскольку полученный адрес Лф является адресом конца слова, то для получения адресов ячеек в остальных накопительных блоках, количество которых онределяется схемой 9 посредством дещифратора 11, первая н третья части адреса Лф поступают на сумматор 20, на другой вход последнего, связанный с выходом схемы «И 12, поступает сигнал «-1. Полученный адрес ячейки второго накопительного блока поступает на вход регистра 17, а также для получения следующих адресов подается на вход сумматора 21. Аналогичным образом формируются адреса.ячеек всех накопительных блоков, где хранится или должно храниться слово. Часть адреса Лф поступает на схему 15. В случае срабатывания схемы 15, т. е. обнаружения нулем в третьей части адреса, в разряды 65 регистра адреса 10 поступает сигнал «-1. Так как из-за ну.л1ерацин позиций слогов в ячейке, например ячейки, состоящей из четырех слогов: 01, 10, 11, 00, при выполнении арифметической операции в схеме 3 происходит перенос единицы в старщий разряд, то для получения физического адреса Л ф необходимо вычесть «1 из содержимого разрядов 65 регистра 10. Преобразование адреса ячейки в сигнал осуществляется с помощью коммутаторов 23-26. Для определения накопительного -блока, к которому нужпо обратиться но полученному адресу ячейки, служат группы схем «И 27-30, схемы «ИЛИ 31-34 и коммутаторы 23--26. Преобразование адреса ячейки в сигнал осуществляется с помощью дешифраторов адреса 35-38. При чтении слово с нокомых

ячеек накопительных блоков поступает на регистры слов 43-46.

Для получения истинного положения считанного слова используются группы схем «И 47, 48 и 50 и схемы «ИЛИ 51-54. Таким образом, выбранное слово записывается в регистры 55-58. Далее схемой сдвига 59 слово сдвигается в крайнее правое положение и поступает на схему блокировки 60, которая окончательно формирует слово путем блокировки (р+1)-то и других слогов. На выходе схемы формируется считанное слово длиной р. Процесс записи протекает в обратном напра влении. Слово, подлежащее записи, поступает .на схему блокировки 60 и схему сдвига 59 и залисывается в регистры 55, 57 и 58 на нужные позиции. Затем содержимое этих регистров записывается в накопительные блоки по Соответствующим адресам ячеек и накопительных блоков.

Предмет изобретения

Запоминающее устройство, содержащее п накопительных блоков, подключенных к соответствующим дещифраторам адреса и регистрам слов, подсоединеи-ным через группы схем «И и схемы «ИЛИ к выходным регистрам слов, п регистров адреса, входной регистр адреса, дешифратор, вспомогательную схему «И, дополнительные схемы «ИЛИ, дополнительные группы схем «И, блок управления, отличающееся тем, что, с целью увеличения эффективной емкости устройства, оно содержит п коммутаторов, п-1 сумматоров и п-1 дополнительных схем «И, дополнительный регистр, схему образования множителя, схему умножения, схему округления, схему обнаружения нуля, схему сдвига и схему блокировки, причем один вход схемы умножения подключен к выходу входного регистра адреса, другой - к в.ыходу схемы образования множителя, а выход - к входам первого регистра адреса, выход донолнительного регистра подсоединен к входам схемы образования множителя и схемы округлелия, разряды регистров адреса, кроме п-го регистра адреса, подключены к одному входу последующего сумматора, другой вход которого подсоединен к выходу соответствующей дополнительной схемы «1-1, а выход- к разрядам соответствующего регистра адреса, вход дешифратора соединен с выходом схемы округления, а его выходы - с одними

входами дополнительных схем «И, другие входы которых связаны с блоком управления, старшие разряды регистров адреса подключеиы через дополнительные группы схем «И и дополнительные схемы «ИЛИ к соответствующим дешифраторам адреса, младшие разряды - к входам коммутаторов, выходы которых связаны с соответствующими группами схем «И, дополнительные разряды первого регистра адреса подключены к входам

схемы обнаружения нуля, выход которой через вспомогательную схему «И соединен с младшими разрядами первого регистра адреса, входы и выходы схемы сдвига подсоединены к соответствующим входам и выходам

выходных регистров слов и схемы блокировки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Ассоциативное запоминающее устройство | 1986 |

|

SU1388949A1 |

| УСТРОЙСТВО ДЛЯ ОБМЕНА ИНФОРМАЦИЕЙ Л1ЕЖДУ АБОНЕНТАМИ И ЦВМ | 1973 |

|

SU368607A1 |

| Устройство для изучения языка | 1990 |

|

SU1785029A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| КОМБИНИРОВАННАЯ ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1966 |

|

SU224910A1 |

| Запоминающее устройство | 1978 |

|

SU926712A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| Устройство для отображения графической информации на экране электронно-лучевой трубки | 1980 |

|

SU941987A1 |

Авторы

Даты

1975-06-30—Публикация

1973-05-08—Подача