1

Изобретение относится к области вычислительной техники и может быть использовано в радиотехнических устройствах, в частности в устройствах телеметрии, автоматики и ЦВМ.

В известном двухтактном регистре сдвига, образованном последовательно соединенными триггерами с непосредственными связями, для передачи информации используется накопление заряда в транзисторах.

Известиый регистр сдвига имеет малое быстродействие при требовании экономичности питания из-за большого времени восстановления транзисторов через большой нагрузочный резистор в промежутках между тактовыми импульсами; относительно узкий диапазон питающего напряжения и предъявляет жесткие требования к параметрам импульсов тактового напряжения.

Цель изобретения - обеспечить работу в широком частотном диапазоне при пониженном напряжении питания (1в) и минимальном токе потребления.

Эта цель достигается за счет соединения двух соседних триггеров через управляющий транзистор, база и коллектор которого подключены к разным плечам двух соседних триггеров, эмиттер подключен к одному из з,вух источников тактовых импульсов, а на

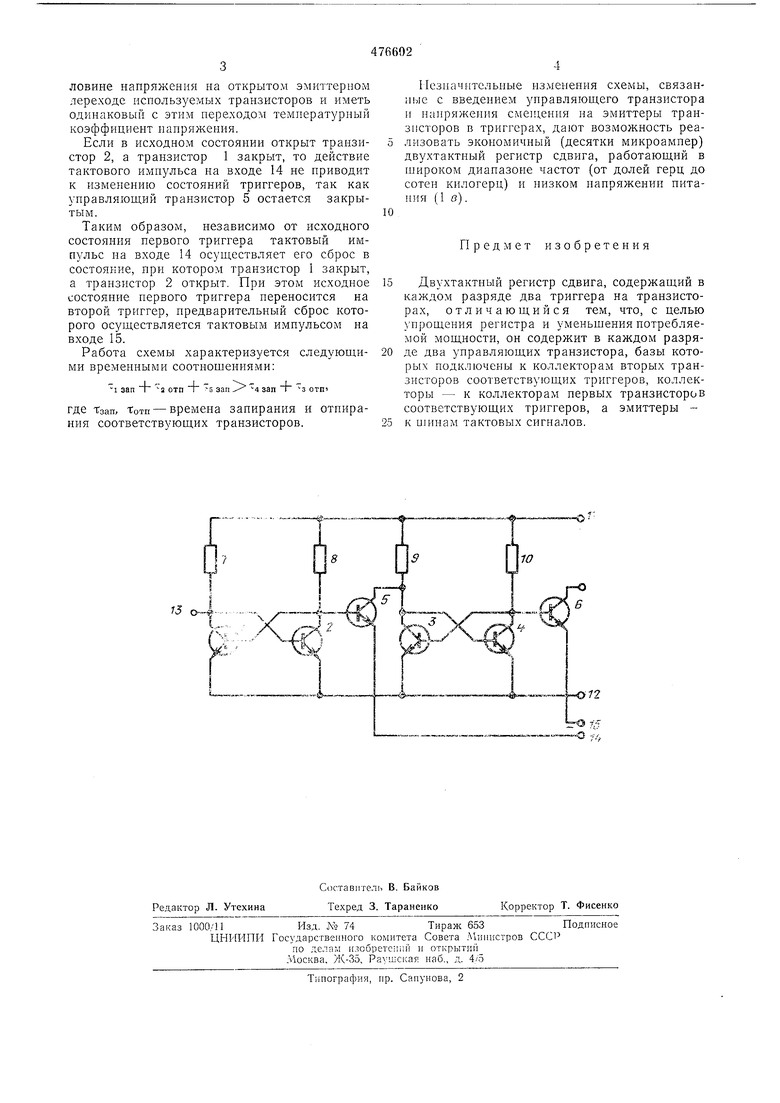

эмиттеры транзисторов, образующих каждый из триггеров, подано напряжение смещения. Цринципиальная электрическая схема одного разряда двухтактного регистра сдвига

приведена на чертеже.

Регистр содержит кремниевые транзисторы 1-4 типа п-р-п; управляющие кремниевые транзисторы 5, 6 типа п-р-п; коллекторные нагрузки 7-10; источник постоянного положительного напряжения 11, источник постоянного положительного напряжения смещения 12, информационный вход 13 разряда регистра сдвига и входы 14, 15 тактовых импульсов. Устройство работает следующим образом.

Цусть в исходном состоянии транзисторы 1 и 4 открыты, а транзисторы 2 и 3 закрыты. Цод действием тактового импульса на входе 14 воздействию импульса соответствует перепад напряжения от уровня Е до нуля, управляющий транзистор 5 открывается и щунтирует базовые входы транзисторов 1, 4, вызывая переброс обоих триггеров. После переброса триггеров транзистор 5 оказывается закрытым, так как его базовый вход шунтируется открывшимся транзистором 2.

Описанный процесс возможен лишь при правильном выборе величины напряжения смещения источника 12. Напряжение смещения должно быть приблизительно равно половине напряжения на открытом эмиттерном лереходе используемых транзисторов и иметь одинаковый с этим переходом температурный коэффициент напряжения.

Если в исходном состоянии открыт трапзистор 2, а транзистор 1 закрыт, то действие тактового импульса на входе 14 не приводит к изменению состояний триггеров, так как управляющий транзистор 5 остается закрытым.

Таким образом, независимо от исходного состояния первого триггера тактовый импульс па входе 14 осуществляет его сброс в состояние, при котором транзистор 1 закрыт, а транзистор 2 открыт. При этом исходное состояние первого триггера переносится на второй триггер, предварительный сброс которого осуществляется тактовым импульсом на входе 15.

Работа схемы характеризуется следующнмн временными соотногнениями:

i зап г отп т з зап 4 зап з отп

где Тзап, Тотп - времена запирания и отпирания соответствующих транзисторов.

Незначительные изменения схемы, связанные с введением управляющего транзистора и напряжения смеи1,епия на эмиттеры транзисторов в триггерах, дают возможность реализовать экономичный (десятки микроампер) двухтактпый регистр сдвига, работающий в широком диапазоне частот (от долей герц до сотен кплогерц) и низком напряжении нитапия (1 и).

Предмет изобретения

Двухтактный регистр сдвига, содержащий в каждом разряде два триггера на транзисторах, отличающийся тем, что, с целью упрощения регистра и уменьщения потребляемой мощности, он содержит в каждом разряде два управляющих транзистора, базы которых подключены к коллекторам вторых транзисторов соответствующих триггеров, коллекторы - к коллекторам первых транзисторов соответствующих триггеров, а эмиттеры к ошнам тактовых сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка памяти для регистра сдвига | 1980 |

|

SU868836A1 |

| Способ поиска дефектов в цифровых блоках и устройство для его осуществления | 1985 |

|

SU1260884A1 |

| ЯЧЕЙКА ОДНОТАКТНОГО РЕГИСТРА СДВИГА | 1971 |

|

SU317111A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1689991A1 |

| ЁФЛЁКСОМЁТР | 1972 |

|

SU342611A1 |

| РЕГИСТР СДВИГА | 1973 |

|

SU364029A1 |

| Двухтактный преобразователь | 1989 |

|

SU1676042A1 |

| Транзисторный двухтактный преобразователь напряжения | 1980 |

|

SU877761A1 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ | 2009 |

|

RU2422984C2 |

| Многоуровневая ячейка памяти | 1980 |

|

SU1067534A1 |

rj

Авторы

Даты

1975-07-05—Публикация

1973-06-29—Подача