3

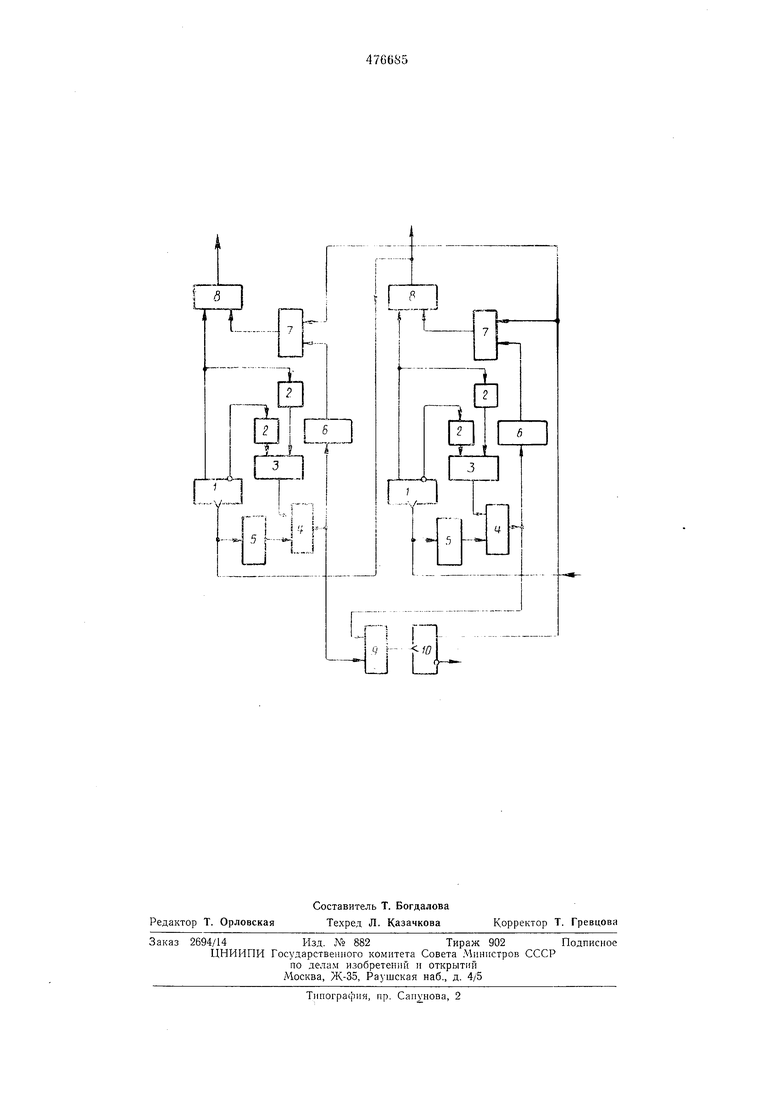

Состояние неисправного триггера при поступлении на его вход импульсов переноса с предыдущего разряда не изменяется, что приводит к отсутствию сигнала на входе схемы неравнозпачности 4, связанном с выходом схемы ИЛИ 3. Поэтому после возникновения неисправности входные импульсы неисправного триггера через элемент задержки 5 и схему неравнозначности 4 начинают поступать через элемент задержки 6 на первый вход схемы И 7, а через схему ИЛИ 9 - на счетный вход контрольного триггера 10, который перед началом работы счетчика устанавливается в нулевое состояние.

При переходе триггера 10 в единичное состояние появляется сигнал на выходе схемы И 7 и на связанном с ним первом входе схемы неравнозначности 8. При этом схема неравнозначности 8 осуществляет инвертирование сигнала, поступающего на ее второй вход с единичного выхода триггера 1.

Если триггер 10 находится в нулевом состоянии, то сигнал на выходе схемы И 7 отсутствует, и выходной сигнал схемы неравнозначности 8 совпадает с сигналом на единичном выходе триггера I.

Таким образом, при поступлении на вход неисправного триггера нечетного числа импульсов выходной сигнал разряда противоположен сигналу на единичном выходе триггера 1, а при четном числе импульсов - совпадает с этим сигналом.

При этом нормальная работа двоичного счетчика не нарушается. Элементы задержки 5 и 6 служат для синхронизации работы остальных узлов счетчика.

Предмет изобретения

Двоичный счетчик импульсов, содержащий в каждом разряде счетный триггер, выходы

которого через дифференцирующие цепи и схему ИЛИ соединены с нервым входом схемы неравнозначности, второй вход которой через элемент задержки подключен к счетному входу триггера, выходы схем неравнозначности всех разрядов соединены через схему ИЛИ со счетным входом контрольного триггера, отличающийся тем, что, с целью сохранения работоспособности при одиночных неисправностях, каждый разряд

дополнительно содержит двухвходовую схему И, вторую схему неравнозначности и второй элемент задержки, первый вход схемы И соединен с выходом контрольного триггера, а второй вход соединен через второй элемент

задержки с выходом первой схемы неравнозначности, первый вход второй схемы неравнозначности соединен с выходом схемы И, а второй вход второй схемы неравнозначности подключен к единичному выходу триггера

своего разряда, а выход второй схемы неравнозначности соединен со счетным входом триггера соседнего старшего разряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоичный счетчик импульсов с контролем ошибок | 1977 |

|

SU687601A1 |

| Реверсивный счетчик | 1977 |

|

SU738179A1 |

| Устройство для контроля | 1986 |

|

SU1330755A1 |

| Устройство для контроля схем сравнения | 1979 |

|

SU960822A1 |

| Программное устройство | 1977 |

|

SU734646A1 |

| Устройство для группового контроля логических блоков | 1986 |

|

SU1372323A1 |

| Пересчетное устройство | 1980 |

|

SU921093A1 |

| Пересчетное устройство с контролем | 1982 |

|

SU1019452A1 |

| Счетчик с контролем | 1988 |

|

SU1649523A1 |

| Устройство для поиска кратных неисправностей в однотипных логических блоках | 1978 |

|

SU781816A1 |

Авторы

Даты

1975-07-05—Публикация

1973-05-23—Подача