(54) РЕВЕРСИВНЫЙ СЧЕТЧЙК

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интегратор с контролем | 1975 |

|

SU540269A1 |

| Устройство для интегрирования функций | 1984 |

|

SU1242993A1 |

| Устройство для интегрирования функций | 1982 |

|

SU1070570A1 |

| Функциональный генератор | 1980 |

|

SU902022A1 |

| Коррелометр | 1980 |

|

SU1062717A1 |

| Устройство для дискретной записи и воспроизведения функций | 1981 |

|

SU982034A1 |

| СИНУСНО-КОСИНУСНЫЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1972 |

|

SU335703A1 |

| РЕВЕРСИВНЫЙ ДВОИЧНЫЙ СЧЕТЧИК | 1992 |

|

RU2047272C1 |

| Устройство задержки импульсов | 1981 |

|

SU974564A2 |

| Счетное устройство | 1984 |

|

SU1210221A1 |

Изобретение относится в области автоматики и может быть использовано в вычислительной и цифровой измерительной технике. ,

Известен реверсивный счетчик, содержащий счетные триггеры, триггер реверса, триггер-указатель кода, формирователь импульсов обращения и триггер знака 1.

Недостатком такого реверсивного , счетчика является наличие временной задержки между моментом поступления последнего импу.пьса входной последовательности на один из его входов и моментом выдачи результата .отсчета что снижает его быстродействие.

Известен реверсивный ,содержащий последовательно соединенные реверсивные счетные разряды, образующие счетчик, устройство индикации, схему выделения Нулевого состояния всех разрядов, триггер знака с ключами переключения, а также ключи коммутации входных сигналов и схемы ИЛИ. Вькода счетных разрядов соединены с входами устройства индикации, а: также через схему выделения нулевого состояния с управляющими входами К.ЛЮчей переключения триггера знака, выО

которого соединеходы

и

ны попарно С ч.етырьмя ключами коммутации входных сигналов. Другие входи этих ключей соединены с .клеммами счетных сигналов прямого и обратного, счетов. Выходы ключей попарно через ИЛИ соединены с Входами суммирования и .вычитания счетных разрядов. Отсчет производится только в

10 прямом коде 2,

Недос атком этбго счетчика являет сянизкхзе быстродействие. -Цель изобретёния-повышение быстрО действ11Я реверсивного счетчика.

20 дешифратора нулевого состояния, триггер знака, элемент И, один вход которого соединён с вькодом дешифратора нулевого состояния, яругой вход - с входной шиной знака, а выход - с

25 -входом триггера знака, введены ;:7Т йггёр реверса и элетмент неравно Га«неб й7 Ьдй - вход которого соединен с входной шиной знака, другой ;вход - с прямым выходом триггера зна30

ка, выход элемента неравнозначности соединей со счетньам входом триггера реверса, R-вход которого подключен к выходу дешифратора нулевого состояййя и к счетному входу триггера знака, причем счетный вход первого счетного разряда соединен с входной шиной счётных импульсов, вход вычйта; ййя разрядов соединен с пряКИМ выходом, а вход сложения-с 66ратйЕлм выходом триггера реверса.

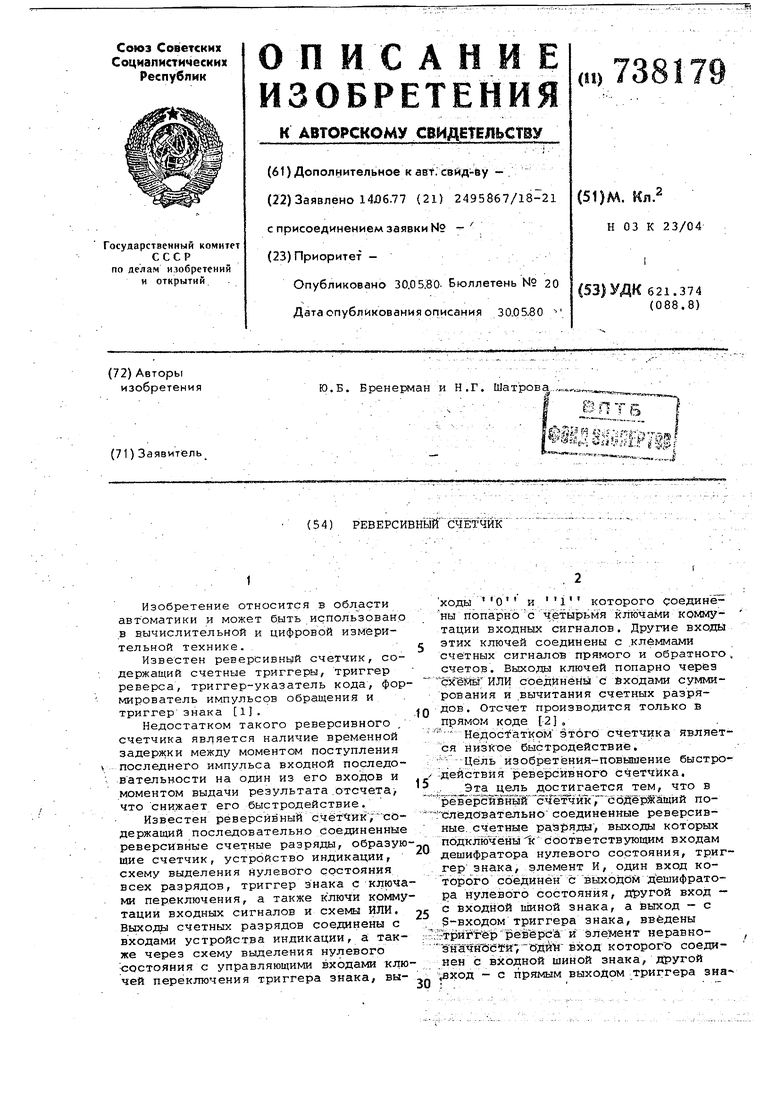

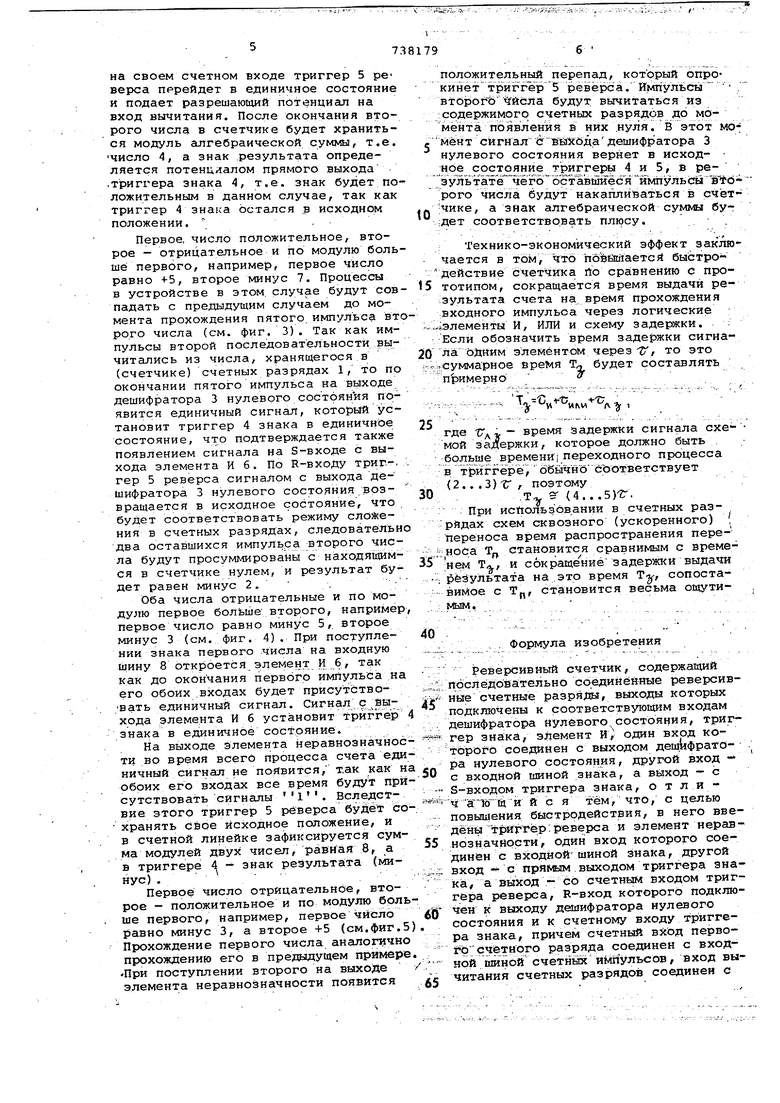

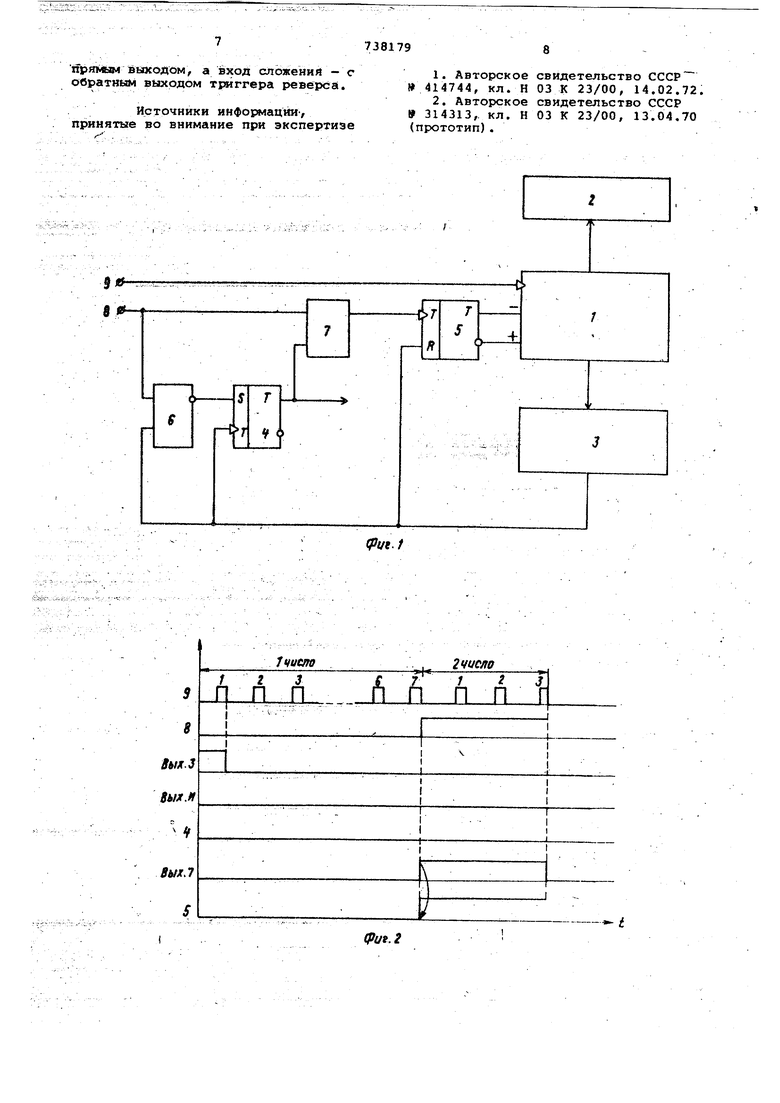

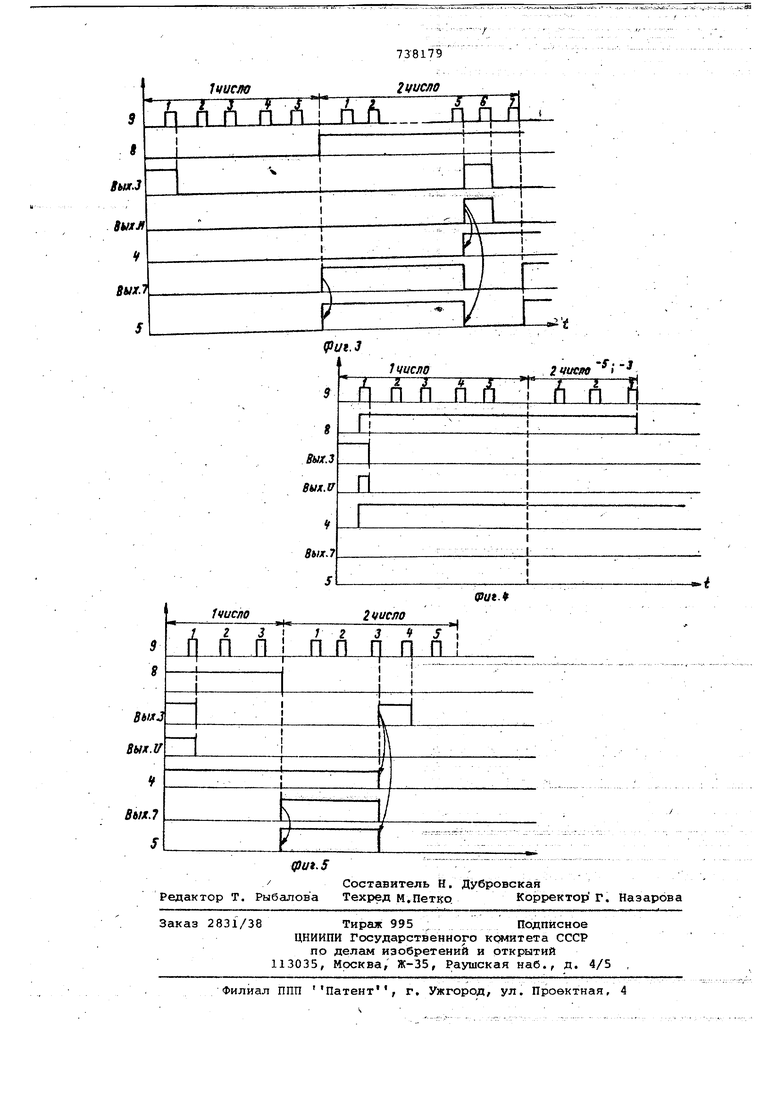

На фиг.1 приведена функциональная tiSeMi ё15г:йвйого счетчика; на . фиг. 2, 3, 4, 5 данйврейённйё ди- . ; .граммы ра1боты счетчика для различных -ко1 индШ ёттШ-т т&5М

тей. ,,,,.-,;„; . . , ; , ./

Реверсивный счетчик содёрж1 Т реверсивные счетные разряды 1, устройство 2 индикации, дешифратор 3 «S состояния всех разрядов счетчика, триггер 4 знака, триггер 5 реверса, элемент И б, элемент 7 нёравТгШначйдетй, - - Вйходы разрядов 1 соединены с вхо/дами устройства 2 emKsm« r fSKWe

через дешифратор 3 нулёвого сбе1гО я-. йия вЬех разрядов счетчика с R-BXO- . дснй триггёра 5 ревёрйа, счётййм ЁХО fifSvi триггера 4 знака и одним из вхо яов элемента и 6, ВторЬй вШ; элШёнта И подключен к шине 8 знййа входной последовательности, к которой также подключен один из входов злемента 7 неравнозначности. Выход элемента И б соединен с S-BX ojn@ flptirгера 4 знака, прямой выход которЪго соедййён с вторлм входом элемента 7 неравнозначности. Выход этого злеМёйта соедййен 1гр счётным входим триггера 5 реверса, прямой звыходкоTbpoirO подключен к входу вычитания счётвьах разрядов 1, а обратный выход - к входу суммирования. Счетный вХбД Первого разряда соединей с входной шиной 9;счетных импульсов;

предлагаемый реверсивный счетчик работает следующим образом.

В йсХрднОМсоётОянии триггеры 4, 5 уб ШоёЯёййв нулебоесостояние, элемент И б открыт по одному входу сигвалом с выхода дешифратора 3 йулевогЬ состояййя. С приходом первого-числа на входной шине 8 появляется сигнал, соответствующий зйак чйсла, причем знаку плюс соответствует нулевой уровень, а знаку минус - единичный. На шине 9 появляется первый йШульс первого числа. Знак riepBoro числа заЯШйдаеТся триггером 4 знака,иЧего сос Ьянйе не изменяется, если знак Числа совпадает со Эн Тйсяи

первого. Состояние триггера 5 рёвёрda в этом случае также не иэмёняется, и по окончании второго числа в счетных разрядах будет храниться сумма модулей Этих чисел.

В случае несовпадения знаков благодаря наличию элемента 7 йеравно7381Г9

значности в момент поступления второго числа изменит свое состояние триггер 5 реверса, который переведет счетные разряды в режим вычитания. Если BTopde число при этом меньше первого по модулю, то,после его окончания в счетных разрядах будет храниться модуль разности чисел, а в триггере 4 знака - знак большего, т.е. первого числа. Если же модуль второго числа больше иодуля первого, то в MdMeHT появления нуля во всех счётных разрядах изменится состояние триггеров 4 и 5 на противоположное. Триггер 5 ревёрСа заставит счетные разряды работать вновь в режиме суммирования И в результате в них зафиксируеТСЯ модуль разности двух чисел в прямом коде, а триггер 4 будет хранить знак второго числа.

Поясним работу реверсивного счетчика на.примерах. , Оба-числа положительные, и первое ЧИСЛО больше вТОрОго, например, пер- вое число +7, а второе +3. С приходом первого импульса первого числа состояние элементов б и 7 не изменяется. По окончании первого импульса сигнал на -выходе дешифратора 3 нулевого -состояния принимает нулевой ПОтёнцИал,ЧТОне оказывает влияния на состояние триггера 4 знака, который E earfiii5ye:T: niib на Положительный перепад на счётном входе. Так и триггер 5 реверса остается в исходнОм соСтоянии, то на входе суммиро- ,. вания счетных разрядов 1 остается п0тёнциал, и состояние счетных райрядов 1 после прохождения первого числа будет соответствовать числу 7. С приходом вТОрОгО. числа состояние триггера 4зйака и триггера 5 реверйа не изменяется из-за,совпадения нулевых потенциалов на входах элементов 6 и , поэтому, после прохожде:ййя второго числа в .счетной линейке

будет зафийСИров ана сумма .двух чисел, равная 10.

Первое число положительное, второё отрицательное и по модулю первое брльшеёТОроТО; например, первое чйсло равйо +7, а второе минус 3 (см. фиг. 2). Прохождение первого числа будет ПОЛНОСТЬЮ соответствовать предыдущему примеру, и после его окончания в счетной линейке будет храниться код числа 7, а триггеры 4 и 5 будут сохранять -ййЗсодное состояние. С приходом йтороГОчйсл ана входе схемы . И б появится единичный сигнал, но триггер 4- знака не изменит своего сЬстЬянй1й йй-За нулевого сигнала с Дешифратора 3 нулевого состояния на втором входе элемента И б. На выходе Элемента 7 неравнозначности появится

так как на его входах

сигнал

с выхода.

присутствуют сигналы

триггера 4 знака и i с входной шины.8 По .положительному перепаду

на своем счетном входе триггер 5 реверса перейдет в единичное состояние и подает разрешающий потенциал на вход вычитания. После окончания второго числа в счетчике будет храниться модуль алгебраической суммы, т.е. ЧИСЛО 4, а знак .результата определяется потенциалом прямого выхода .триггера знака 4, т.е. знак будет положительным в данном случае, так как триггер 4 знака остался в исходном положении. ,

Первое, число положительное, второе - отрицательное и по модулю больше первого, например, первое число равно -t-5, второе минус 7. Процессы в устройстве в этом, случае будут совпадать с предыдущим случаем до момента прохождения пятого импульса второго числа (см. фиг. 3). Так как импульсы второй последовательности вьачитались из числа, хранящегося в (счетчике) счетных разрядах 1, то по окончании пятого импульса на выходе дешифратора 3 нулевого состояния по явится единичный сигнал, которьГйустановит триггер 4 знака в единичное состояние, что подтверждается также появлением сигнала на S-входе с выхода элемента И б. По R-входу триг--, гер 5 реверса сигналом с выхода дешифратора 3 нулевого состояния врзвращаетс;я в исходное состояние, что будет соответствовать режиму сло ения в счетных разрядах, следовательно два оставшихся импуль.са второго числа будут просуммированы с находящимся в счетчике нулем, и результат будет равен минус 2. .

Оба числа отрицательные и по модулю первое больше второго, например, первое число равно минус 5,. второе минус 3 (см. фиг. 4). При поступлении знака первого числа на входную шину 8 откроется элемент И б, так как до окончания первого импульса на его обоих входах будет присутствовать единичный сигнал. Сигнал с ,йы- . хода элемента И б установит триггер 4 знака в единичное состояние.

На выходе элемента неравнозначности во время всего процесса счета единичный сигнал не появится, т.ак как на обоих его входах все время будут присутствовать сигналы . Вследствие этого триггер 5 реверса будет сохранять свое исходное положение, и в счетной линейке зафиксируется сумма модулей двух чисел, равная 8, а в триггере 4 знак реэульта:та (минус) .

Первое число отрицательное, второе - положительное и по модулю больше первого, например, первое число равно минус 3, а второе +5 (см.фиг.5) Прохождение первого числа аналог11чно прохождению его в предыдущем примере. При поступлении второго на выходе элемента неравнозна;чности появится

положительный перепад, который опрокинет тр иггёр 5 ревёрса. Импульсы . BToport егйсла будут вычитаться из . содержимсзго счетных разрядов до момёнта появления в них нуля.в этот момент Сигнале ахйдадешифратора 3 нулевого состояния вернет в исход- ;ное срстсэяние триггеры 4 и 5, в результате чё го ocTaJBiimecH импульсы второго гисла будут накапливаться в счетчике, а знак алгебраической суммы буO:дет соответствовать плюсу.

; Технико-экономический эффект заключается в том, 1то повышается быЬтродействие счетчика По сра1вненйю с про5тотипом, сокращается время выдачи ре;зультата счета на. время прохождения :Входного импульса через логические

элементы И, ИЛИ и схему задержки. : Если обозначить время задержки сигиа0ла ойним элементом через , то это

;|:Суммарное время Т будет составлять пЬимернб

-

5

где Тд J - время задержки сигнала схе-- мой задержки, которое должно быть больше времени переходного процесса в триггере, обычно сЪот ветствует (2...3)Т,. поэтому

0

.Т (4...5)С.

- При исйользов.ании в счетных раз- . рядах схем сквозного (ускоренного) переноса время распространения пере;НосаТ„ становится сравнимым с временем Т, и сокращениё задержки выдачи

5 результата на это время Т, сопоставимое с Т, становится весьма ощути- .

МЫМ. .

. . Формула изобретения

реверсивяьтй счетчик, содержащий последовательно соединённые реверсивные счетные разряда, выходы которых подключены к соответствующим входам дешифратора нулевого состояния, триггер зна;ка, элемент И, один вход которого соединен с выходом депгафрато- . ра нулевого состояния, другой вход - с входной шиной знака, а выход - с S-входом триггера знака, о т л и ч и и с я тем, что, с целью повышения быстродействия, в него введены Tpifrrep;peBepca и элемент неравнозначности, один вход которого соединен с входнойшиной знака, другой вход - с прямым выходом триггера знака, а. выход - со счётнь1М входом триггера реверса, R-вход которого подключен к выходу дешифратора нулевого состояния и к счетному входу триггера знака, причем счетный вход первоfiQ c4ieTHoro разряда соединен с входной шиной счетных импульсов, вход вычитания счетных разрядов соединен с

ifpHMBW выходом, a вход сложения - с обратным выходом триггера реверса.

Источники информации-, принятые во внимание при экспертизе

7 чист

г 3

Л

run

свидетельство СССР

03 К 23/00, 14.02.72.

свидетельство СССР

03 К 23/00, 13.04.70

2ЧЧСПО

Lh

i

Авторы

Даты

1980-05-30—Публикация

1977-06-14—Подача