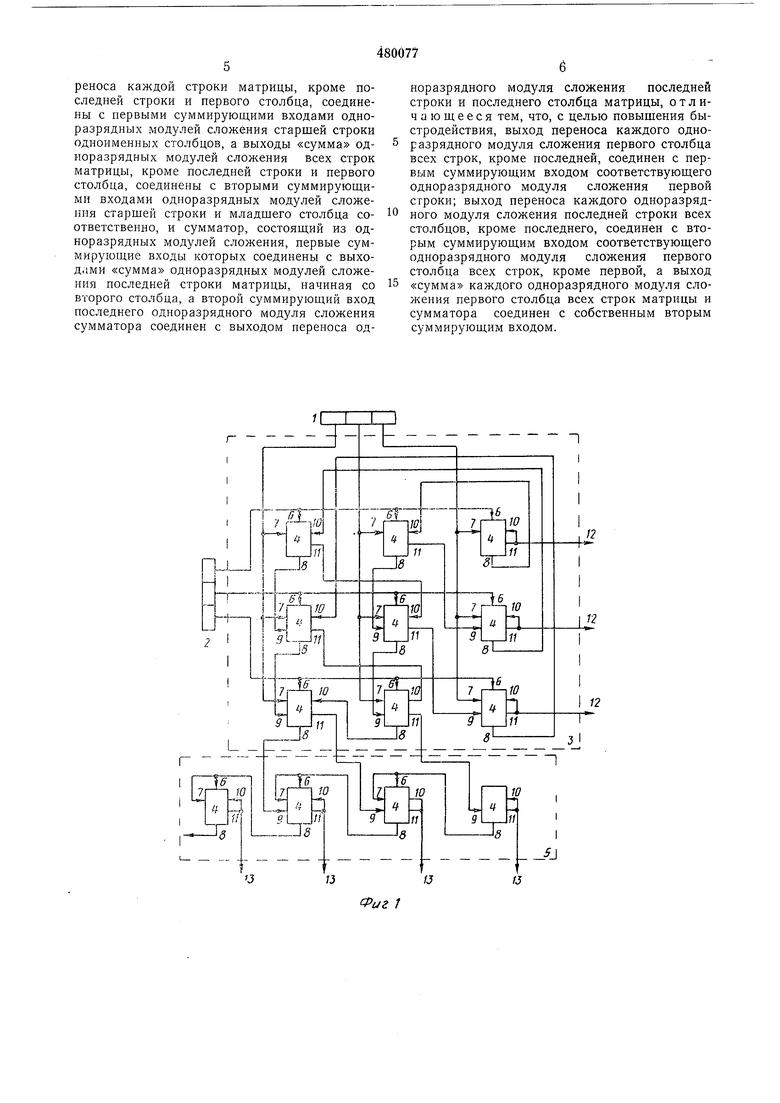

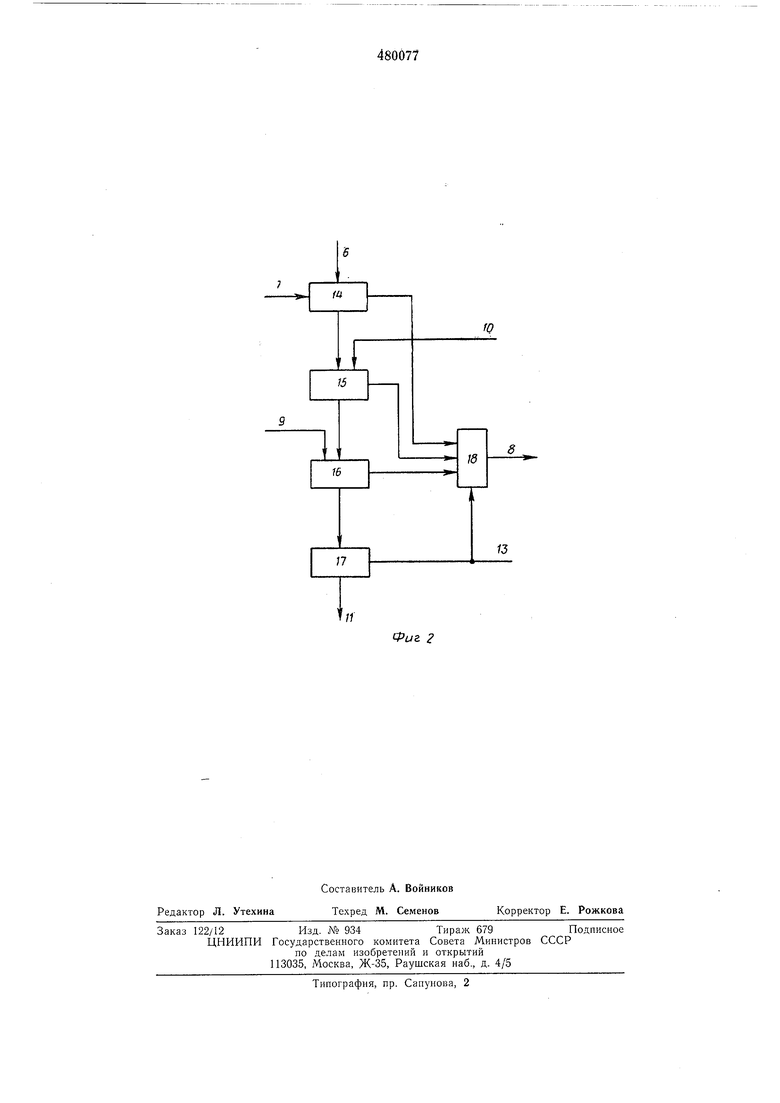

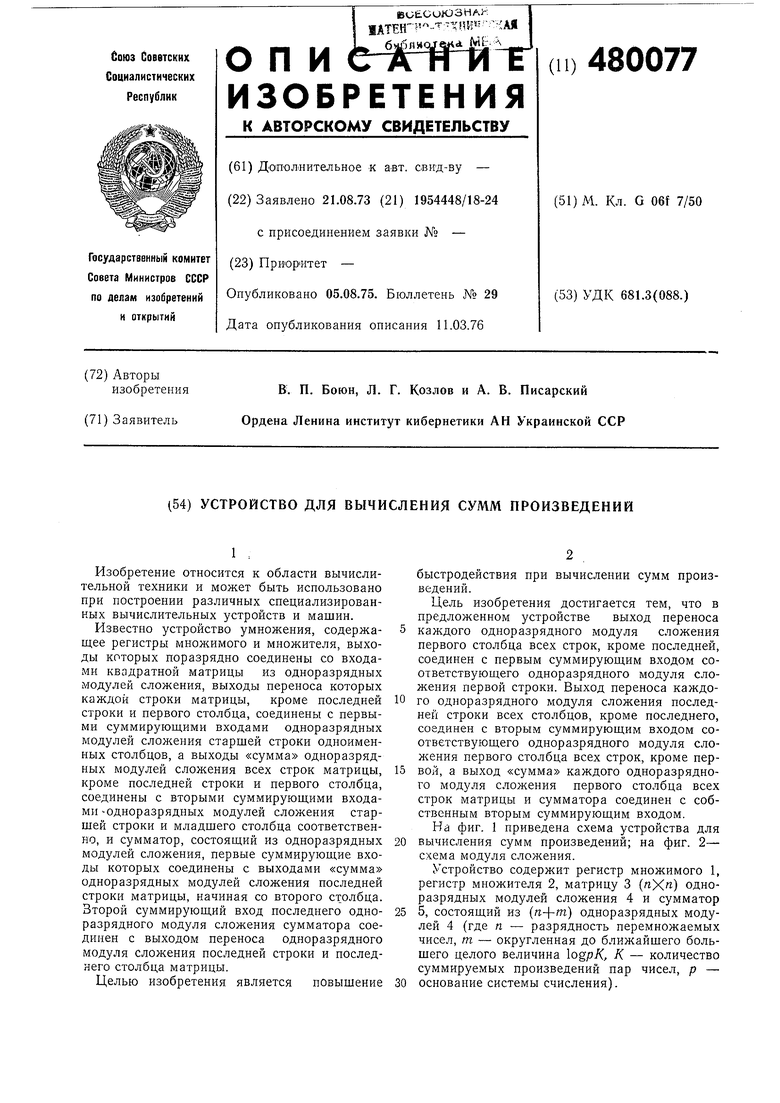

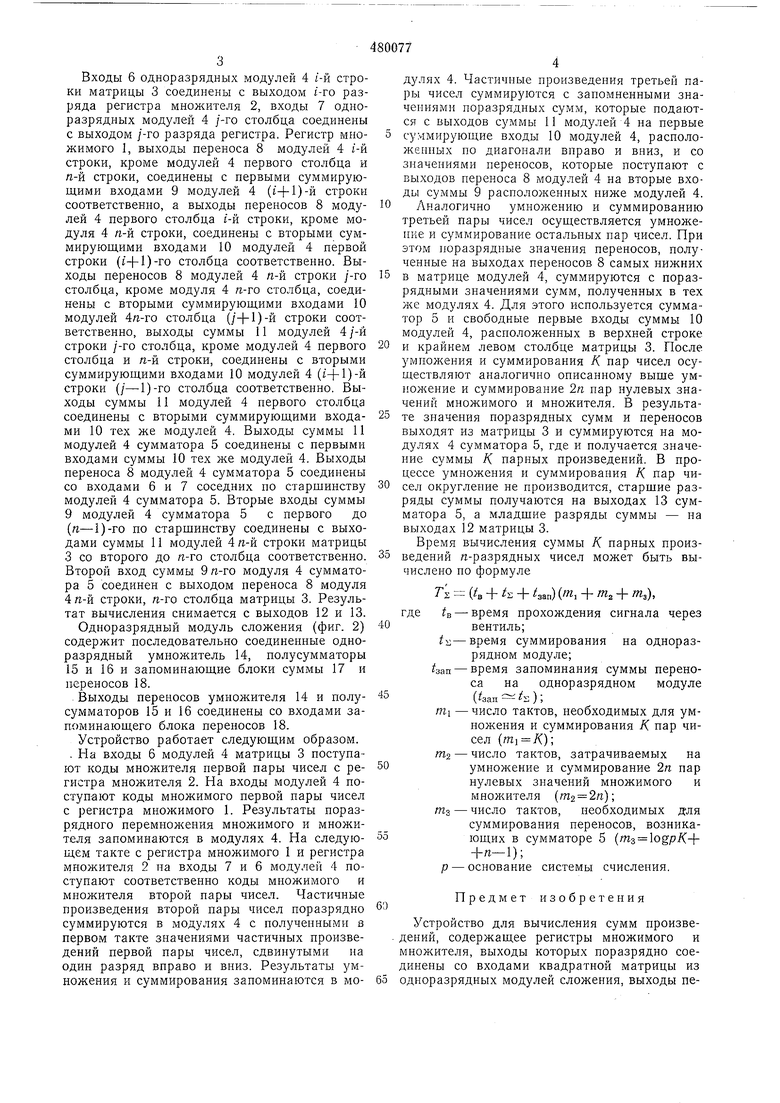

Входы 6 одноразрядных модулей 4 /-и строки матрицы 3 соединены с выходом t-ro разряда регистра множителя 2, входы 7 одноразрядных модулей 4 /-ГО столбца соединены с выходом /-ГО разряда регистра. Регистр множимого 1, выходы переноса 8 модулей 4 1-й строки, кроме модулей 4 первого столбца и /г-й строки, соединены с первыми суммирующими входами 9 модулей 4 (1+1)-й строки соответственно, а выходы переносов 8 модулей 4 первого столбца г-й строки, кроме модуля 4 п-и строки, соединены с вторыми суммирующими входами 10 модулей 4 первой строки (i+l)-ro столбца соответственно. Выходы переносов 8 модулей 4 /г-й строки /-го столбца, кроме модуля 4 п-го столбца, соединены с вторыми суммирующими входами 10 модулей 4«-го столбца (/Н-1)-й строки соответственно, выходы суммы 11 модулей 4/-и строки /-ГО столбца, кроме модулей 4 первого столбца и я-й строки, соединены с вторыми суммирующими входами 10 модулей 4 (i-}-)-H строки (/-1)-го столбца соответственно. Выходы суммы 11 модулей 4 первого столбца соединены с вторыми суммирующими входами 10 тех же модулей 4. Выходы суммы 11 модулей 4 сумматора 5 соединены с первыми входами суммы 10 тех же модулей 4. Выходы переноса 8 модулей 4 сумматора 5 соединены со входами 6 и 7 соседних по старщинству модулей 4 сумматора 5. Вторые входы суммы 9 модулей 4 сумматора 5 с первого до (п-1)-го по старщинству соединены с выходами суммы 11 модулей 4 я-й строки матрицы 3со второго до п-го столбца соответственно. Второй вход суммы 9 я-го модуля 4 сумматора 5 соединен с выходом переноса 8 модуля 4я-й строки, я-го столбца матрицы 3. Результат вычисления снимается с выходов 12 и 13. Одноразрядный модуль сложения (фиг. 2) содержит последовательно соединенные одноразрядный умножитель 14, полусумматоры 15 и 16 и запоминающие блоки суммы 17 и переносов 18. Выходы переносов умножителя 14 и полусумматоров 15 и 16 соединены со входами запоминающего блока переносов 18. Устройство работает следующим образом. - На входы 6 модулей 4 матрицы 3 поступают коды множителя первой пары чисел с регистра множителя 2. На входы модулей 4 поступ-ают коды множимого первой пары чисел с регистра множимого 1. Результаты поразрядного перемножения множимого и множителя запоминаются в модулях 4. На следующем такте с регистра множимого 1 и регистра множителя 2 на входы 7 и 6 модулей 4 поступают соответственно коды множимого и множителя второй пары чисел. Частичные произведения второй пары чисел поразрядно суммируются в модулях 4 с получепными в первом такте значениями частичных произведений первой пары чисел, сдвинутыми на один разряд вправо и вниз. Результаты умножения и суммирования запоминаются в модулях 4. Частичные произведения третьей пары чисел суммируются с заномненными значениями поразрядных сумм, которые подаются с выходов суммы II модулей 4 на первые суммирующие входы 10 модулей 4, расположенных по диагонали вправо и вниз, и со значениями переносов, которые поступают с выходов переноса 8 модулей 4 на вторые входы суммы 9 расположенных ниже модулей 4. Аналогично умножению и суммированию третьей пары чисел осуществляется умножение и суммирование остальных пар чисел. При этом поразрядные значения переносов, полученные на выходах переносов 8 самых нижних в матрице модулей 4, суммируются с поразрядными значениями сумм, полученных в тех же модулях 4. Для этого используется сумматор 5 и свободные первые входы суммы 10 модулей 4, расположенных в верхней строке и крайнем левом столбце матрицы 3. После умножения и суммирования /С пар чисел осуществляют аналогично описанному выще умножение и суммирование 2я пар нулевых значений множимого и множителя. В результате значения поразрядных сумм и переносов выходят из матрицы 3 и суммируются на модулях 4 сумматора 5, где и получается значение суммы К парных произведений. В процессе умножения и суммирования К. пар чисел округление не производится, старщие разряды суммы получаются на выходах 13 сумматора 5, а младшие разряды суммы - на выходах 12 матрицы 3. Время вычисления суммы К парных произведений я-разрядных чисел может быть вычислено но формуле (4 + 2 + 4ап) (/«1 + «2 Н- /«з), где ts - время прохождения сигнала через вентиль; s-время суммирования на одноразрядном модуле; гзап - время запоминания суммы переноса на одноразрядном модуле (); mi - число тактов, необходимых для умножения и суммирования Я пар чисел (rai /C); ms - число тактов, затрачиваемых на умножение и суммирование 2я пар нулевых значений множимого и множителя (яга 2я); /Пз - число тактов, необходимых для суммирования переносов, возникающих в сумматоре 5 {mz ogpK- +П-1); р - основание системы счисления. Предмет изобретения Устройство для вычисления сумм произвееиий, содержащее регистры множимого и множителя, выходы которых поразрядно соединены со входами квадратной матрицы из одноразрядных модулей сложения, выходы переноса каждой строки матрицы, кроме последней строки и первого столбца, соединены с первыми суммирующими входами одноразрядных модулей сложения старшей строки одноименных столбцов, а выходы «сумма одноразрядных модулей сложения всех строк матрицы, кроме последней строки и первого столбца, соединены с вторыми суммирующими входами одноразрядных модулей сложения старшей строки и младшего столбца соответственно, и сумматор, состоящий из одноразрядных модулей сложения, первые суммирующие входы которых соединены с выходами «сумма одноразрядных модулей сложения последней строки матрицы, начиная со второго столбца, а второй суммирующий вход последнего одноразрядного модуля сложения сумматора соединен с выходом переноса одноразрядного модуля сложения последней строки и последнего столбца матрицы, отличаюцхееся тем, что, с целью повышения быстродействия, выход переноса каждого одноразрядного модуля сложения первого столбца всех строк, кроме последней, соединен с первым суммирующим входом соответствующего одноразрядного модуля сложения первой строки; выход переноса каждого одноразрядного модуля сложения последней строки всех столбцов, кроме последнего, соединен с вторым суммирующим входом соответствующего одноразрядного модуля сложения первого столбца всех строк, кроме первой, а выход «сумма каждого одноразрядного модуля сложения первого столбца всех строк матрицы и сумматора соединен с собственным вторым суммирующим входом.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения двоичных чисел | 1980 |

|

SU938282A1 |

| Устройство для вычисления сумм произведений | 1975 |

|

SU551643A2 |

| Матричное устройство для умножения чисел по модулю 2 @ -1 | 1985 |

|

SU1254471A1 |

| Вычислительное устройство | 1988 |

|

SU1647553A1 |

| СПОСОБ ОРГАНИЗАЦИИ УМНОЖЕНИЯ ЧИСЕЛ С ПЛАВАЮЩЕЙ ЗАПЯТОЙ, ПРЕДСТАВЛЕННЫХ В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 2012 |

|

RU2485574C1 |

| Устройство для умножения | 1981 |

|

SU1035600A1 |

| Конвейерное множительное устройство | 1981 |

|

SU1043642A1 |

| Матричный умножитель по модулю чисел Ферма | 1990 |

|

SU1783513A1 |

| Устройство для умножения с накоплением | 1982 |

|

SU1108087A1 |

| Матричное устройство для умножения | 1981 |

|

SU999044A1 |

J

73

/J

/J

Фиг 1

fQ

Фиг 2

Авторы

Даты

1975-08-05—Публикация

1973-08-21—Подача