N-й группы, старшие информационные выходы q-ro регистра частичных сумм Е-й группы (,...,У) подключены к входам q-ro регистра частичных сумм (6+1)-и группы, младшие информационные выходы которого подключены к входам q-ro регистра частичных сумм (N+1)-и группы, выходы которого подключены к входам соответствующего сумматора последней строки матрицы, выходы последнего регистра переноса t-й строки матрицы подключены к информационным входам N-ro . сумматора {t+2)-й строки матрицы, выходы последнего регистра переноса N-й группы подключены к информационньвл входам последнего сумматора последней строки матрицы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Конвейерное множительное устройство | 1980 |

|

SU903866A1 |

| Устройство для умножения целых чисел в р-кодах Фибоначчи | 1986 |

|

SU1345190A1 |

| Устройство для умножения с накоплением | 1986 |

|

SU1310810A1 |

| Устройство для умножения с накоплением | 1982 |

|

SU1108087A1 |

| Устройство для вычисления сумм произведений | 1980 |

|

SU905814A1 |

| Вычислительное устройство | 1988 |

|

SU1647553A1 |

| Матричное вычислительное устройство | 1982 |

|

SU1034032A1 |

| Устройство для умножения двух @ -разрядных чисел | 1988 |

|

SU1575174A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU938282A1 |

| Матричное вычислительное устройство | 1988 |

|

SU1541599A1 |

КОНВЕЙЕРНОЕ МНОЖИТЕЛЬНОЕ УСТРОЙСТВО, содержащее матрицу.сумматоров размерностью N х К(Ы -К t где И - разрядность операндов, у - целое натуральное число, М N/J), N групп по М регистров переноса, N групп по М регистров частичных сумм N+2 регистров множителя, N+2 регистров множимого, каждый из которых содержит М подрегистров, буферный регистр, содержащий М подрегистров, причем выходы j-ro подрегистра буферного регистра (,..., М) соединены с информационными входами соответствующих сумматоров первой строки матрицы, входы подрегистров.первого регистра множимого соединены с соответствующими разрядами первой информационной шины устройства,выходы подрегистров последнего регистра множимого соединены с соответствую щими разрядсЦкш первой информационной шины устройства, выходы подрегистра i-го регистра множимого (,..., N4-1) поразрядно соединены с входами j-ro подрегистра

Изобретение относится к вычислительной технике и может быть применено при построении арифметических устройств высокопроизводительных ЦВ Известно устройство умножения двух п-разрядных чисел, содержащее матрицу из элементов И, п-разрядный регистр множимого, {2п-1)-разрядный с матор;, (2п-1)-разрядный блок элементов ИЛИ и п-разрядный регистр множителя Щ . Недостатком этого устройства является низкое быстродействие, так как каждая последующая пара операндов йожет вводиться в устройство только после окончания времени умножения предыдущих п-раэрядных операндов вследствие последовательного выполнения операции умножения. Известно также конвейерное устройство умножения, содержащее матри цу сумматоров, строки которой разви ты на группы, по два сумматора в группе, .объединенных шинами перенос регистр множимого и множителя, буферный регистр, регистры переноса и частичных сумм 2 . ( Недостатком этого устройства TSIK же является низкое быстродействие, так как частота ввода операндов в устройство ограничена временем работы йдной группы из двух сумматоро работающих последовательно. Наиболее близким к изобретению по технической сущности является устройство, содержащее матрицу сумматоров размерностью NX M(N где п - разрядность сомножителей, ), Первая строка матрицы содер жит N сумматоров, каждая последующа строка содержит М сумматоров, послед ний столбец содержит N-1 сумматоров каждый предыд5щий столбец матрицы со держит N сумматоров, N+3 регистров множителя, М регистров множимого. каждый из которых разбит на N подре гистров, буферный регистр, который разбит на N подрегистров, причем выходы j-ro буферного подрегистра (,...,N) соединен с входом соответствукицего сумматора первой строки, входы первых подрегистров множимого соединены с соответствукяцими разрядами первой информационной шины и выходами соответствующих подрегистров множимого последней строки, выходы {i,j) -го подрегистра множимого (.../N,,...,М)поразрядно соединены с входами (i+l,j}-ro подрегистра множимого, входы буферных подрегистров соединены с соответствукяцими выходами .N старших сумматоров последней строки матрицы, выходы которых также подключены к выходной шине устройства, выходы i-rp регистра Множителя поразрядно соединены с входг1ми (i+l)-ro регистра множителя (,...,N+3) и управляющими входами соответствующих N младших сумматоров матрицы, выход переноса j-ro сумматора каждой строки ,...,N) соединен с входом регистра запоминания частичного переноса, выход которого соединен с входом (j+l)-ro сумматора этой же строки, выходы частичных сумм (i,j)-го сумматора подключены к входам регистров частичных сумм, выходы которых подключены к входам (i+l,j)-ro сумматора матрицы 33. Недостатком известного устройства является его низкое быстродействие, так как промежуточные результаты умножения формируются последовательным прохождением частичных сумм по всем cTpoKciM матрицы сумматоров. Цель изобретения - повышение быстродействия. Цель достигается тем, что в конвейерное множительное устройство, содерЖЁЦцее матрицу сумматоров размер; ностью N X , где п - разрядность операндов, jf - целое натуральное число, ), N групп по М регистров переноса, N групп по М регистров частичных сумм, N+2 регистров множителя, N+2 региетров множимого, каждый из которых содержит М подрегистров, буферный регистр, соержащий М подрегистров, причем выходы j-го подрегистра буферного регистра (,...,M) соединены с информационными входами соответствующих сумматоров первой строки матрицы, входы подрегистров первого регистра множимого соединены.с соответствующими разрядами первой информационной шины устройства, выходы подрегистров последнего регистра множимого соединены с соответствующими разрядами первой информационной шины устройства, выходы j-ro подрегистра 1-го регистра множимого ,,.,, N+1) поразрядно соединены с входами j-ro подрегистра (i+l)-ro регистра множимого, входы подрегистров буферного регистра соединены с выходами соответствующих старших сумматоров последней строки матрицы, выходы которых, кроме того, подключены к выходной шине устройства, выходы i-ro регистра множителя поразрядно сое;а1Инены с входами (1+1)-го регистра множителя, выходы к-го регистра множителя (,...,N+2) соединены с управляющими входами соответствующих млсшших сукматоров.матрицы, входы первого регистра множителя соединены с соответствующют разрядами второй информационной шины устройства, введена (N+1)-я.группа регистров частичных сумм, содержащая () регистров а в матрицу сумматоров дополнительно введена(N+1)-я строка сумматоров,содержащая (IHJf-t-1) сумматоров,причем выходы j-ro сумматора Е-и строки матрицы ( ..rN)пордзрядир подключены к входам соответствующего регистра частичных сумм С-и группы, (N-9) разрядов (} 2, где m - целое натуральное число) старшего информационного выхода р-го регистра частичных сумм t -и группы подключены к входу р-го регистра частичных сумм (+1)-й группы ( -И,... ,М) , - разрядов младшего информационного выхода р-го регистра частичных сумм 8-и группы подключены к старшему информационному (p-l)-ro сумматора (С+2)-гй строки матрицы, старшие информацибнные выходы рто регистра частичных сумм N-й группы поразрядно соединены с входеми соответствующих регистров частичных сумм (Ы+1)-й группы, выходы которых подключены к входам соответствующих сумматоров последней строки матрицы, к другим входаоя которых подключены младшие информационные выходы соответствующих ре-, гистров частичных сумм N-й группы/ старшие информационные выходы регистра частичных сумм S-и группы (,...,у) подключены к входам q-fo регистра частичных сумм (Р+1)-й группы, младшие информационные вы-ходы которого подключены к входам .q-ro регистра частичных сумм (Ы+1)-й группы, выходы которого подключена

к входай соответствующего сумматора последней строки матрицы, выходы последнего регистра переноса t-й стро.ки матрицы подключены к информационным входам N-ro сумматора (Ь-ь2)-й строки матрицы, выходы последнего регистра переноса N-й группы подключены, к информационным входам последнего сумматора последней строки матрицы.

0

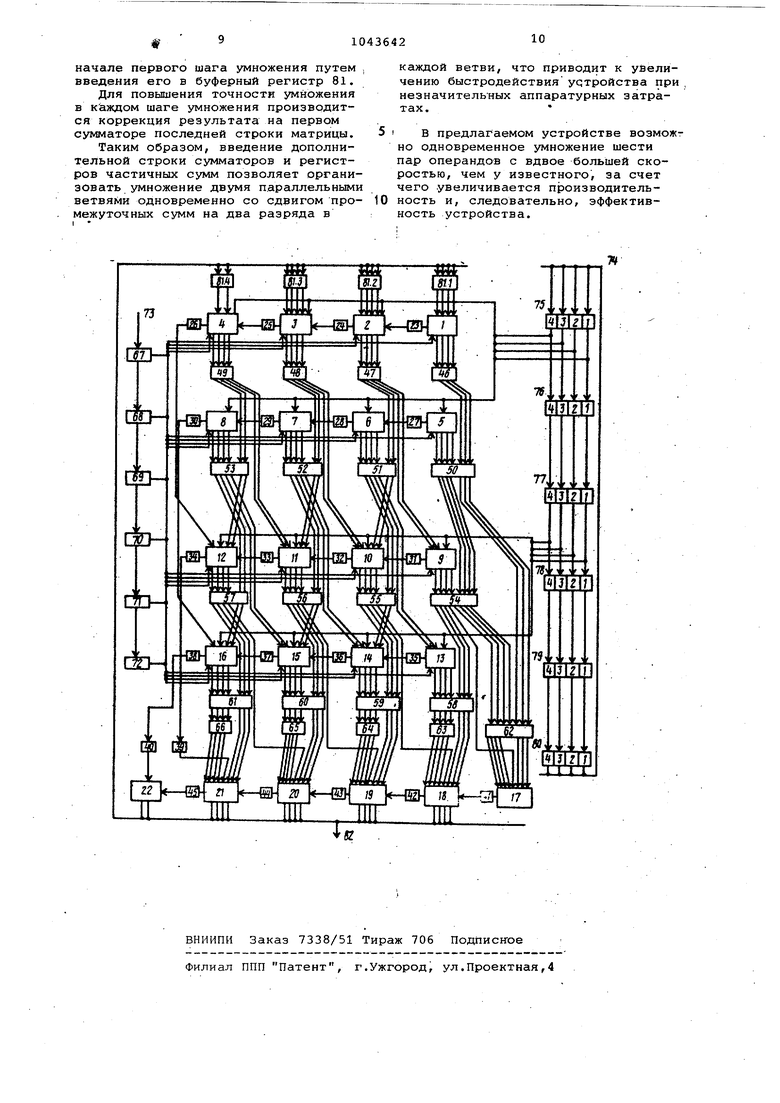

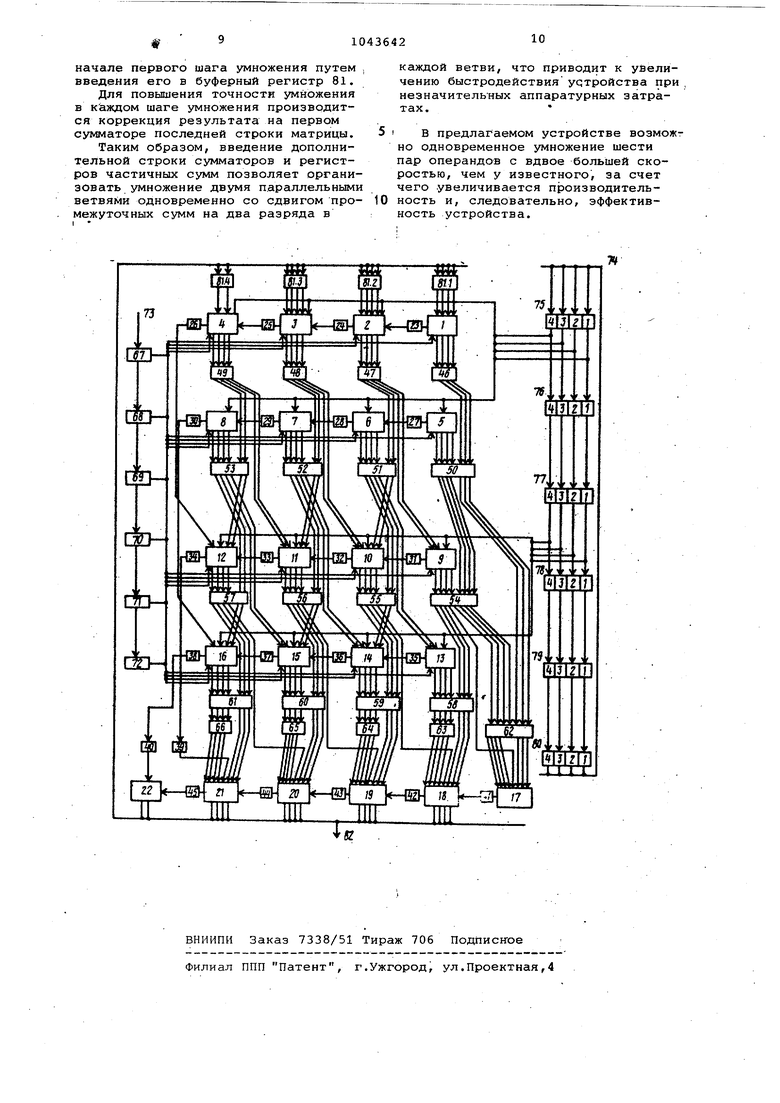

На чертеже представлена струК- с тура предлагаемого устройства.

Конвейерное множительное устройство содержит матрицу сумматоров 122, регис-рры 23-45 переноса, регистры 46-66 частичной суммы, регистры

5 67-72 множителя, информационные шины 73 и 74, регистры 75-80 множимого, буферный регистр 81 и выходную шину 82. Peгиqтpы 75-80 множимого

содержат N подрегистров, буферный

0 регистр содержит М подрегистров, В . устройстве входы подрегистров 75.175.4 множимого соединены с соответствухяцими разрядами информационной шины 74 и соответствующими выходами

5 подрегистров 80.1-80.4 множимого. Выходы подрегистров 75..4 множимого поразрядно соединены с входами соответствующихподрегистров 76.176.4 множимого, выходы которых пораз0рядно соединены с входами соответствующих подрегистров 77.1-77.4 множимого, выходы которых поразрядно соединены с входами соответствующих подрегистров 78.1-78.4 множимого,

5 выходы которых поразрядно соединены с входами соответствующих подрегистров -79.1-79.4 множимого, выходы которых поразрядно соединены с входами соответствующих подрегистров 80.180.4 множимого. Входы буферных под0регистров 81.1-81.4 соединены с соответствующими выходами сумматоров 19-22, выходы сумматоров 18-22 подключены к выходной шине 82 устройства. Входы регистра 67 множителя под5ключены к информационной шине 73 устройства. Выходщ регистра 67 множителя поразрядно соединены с входами регистра б8 множителя, выходы которого поразрядно подключены к

0 входу регистра 69 -множителя, выходы которого поразрядно соединены с входами регистра 70 множителя, выхо. ды которого поразрядно соединены с входами регистра 71 множителя, вы5ходы которого поразрядно соединены с входами регистра 72 множителя. Выходы регистров множителя соединены с управляющими входс1ми сумматоров 1-16 матрицы. Выходы буферных

0 подрегистров 81.1-81.4 соединены с информационньани входами соответствующих сумматоров 1-4 матрицы, выходы сумматоров 1-16 подключены к входам соответствующих регистров 46-61 частичных сумм. Старшие информационные выходы регистров 58-61 подключены к входам соответствующих регистров 63-66 частичных сумм, выходы которы соединены со старшими информационны ми входами соответствующих сумматоров 18-21 матрицы. разрядов регист рЪв частичной суммы соединены с входами соответствующих сумматоро 9-11 матрицы. разрядов старшего ин формационного выхода регистров 51-5 частичных сумм подключены к входам соответствующих сумматоров 13-15 матрицы. N- разрядов регистров 4749 и N- разрядов старших информационных выходов регистров 51-53 частич ных сумм через соответствующие им ре гистры 51-53 и55-57 подключены к входам сумматоров 10-12 и 14-16 матрицы соответственно. Младшие разряды старших информационных выходов регистров 54-57 частичных сумм соединены с соответствующими разрядами младших информационных входов соответствукядих сумматоров. 17-20 матрицы Выход регистра 46 -частичной суммы по ключен к младшему информационному входу регистра 50 частичной суммы, младший информационный выход которого подключен к младшему информационному входу регистра 62 частичной суммы, младший информационный выход которого подключен к младшему информационному входу сумматора 17 матрицы. Старший информационный выход регистра 50 частичной суммы под ключей к младшему информационному входу регистра 54 ч-астично суммы, младший информационный выход которого соединен со старшим информационным входом регистра 62 частичной суммы, старший информационный выход которого соединен с старшим информа ционным входом сумматора 17 матрицы Выходы регистров 26 и 30 переносов соединены с входами соответствующих сумматоров 12 и 16 матрицы. Выходы регистров 34 и 38 переносов через соответствующие им регистры 39 и 40 переносов соединены с входами сумматоров 21 и 22 матрицы. Выходы регистров 67-72 множителя подключены к управляющим входам соответствующих сумматоров 1-16 матрицы. Выходы подрегистров 75.1-75.4 соединены с входами соответствующих им сумматоров 1-4 и 5-8 матрицы. Выходы подрегистров 77.1-77.4 множимого соединены с входами соответствующих им сумматоров 9-12 и 13-16 матрицы. В основу работы устройства заложе конвейерный способ умножения методом поэтапного сложения сдвинутых вправо на два разряда частичных сумм произведения стробируемых соответствующими разрядами множителя. Устройство работает следующим образом. Первый шаг. Первым тактовым сигналом по входным шинам 73 и 74.1 в регистры 67 и 75.1 соответственно принимаются младшие четыре разряда кода множителя и. множимого, при этом множимое с выхода регистра 75.1 подается на вход сумматрров 1 и 5 одновременно, на стробирующий вход которых с выхода регистра 67 подаются соответствующие младшие два разряда кода множителя, причем так, что четный разряд - на вход сумматора 5, а нечетный - на .вход сумматора 1. На сумматоре 1 происходит сложение содержимого регистра 75.1 с содержимым буферного регистра 81.1, равного нулю в начале первого шага умножения. По окончании времени суммирования вторым тактовьом импульсом результат суммирования ,и перенос запоминаются в соответствующих регистрах 46,50 и 23,27. Во входные регистры принимаются следукадие разряды группы разрядов кода сомножителей, так что. в ре.гистры 67 принимаются младшие четыре разряда кода множителя второй пары операндов, а содержимое зтого регистра, соответствующее предыдущему такту, принимается регистром 68. В регистр-75.1 поступают младшие четыре разряда кода множимого второй пары, а в регистр 75.2 - вторая группа разрядов множимого первой пары. С выхода регистра 15,2 код множимого подается, на вход сумматоров 2 и 6. На сумматоре происходит сложение с содержимым буферного регистра 81.2, равно.го нулю в начале первого шага умножения. На стробирующий вход сумматоров 2 и 6 с выхода регистра 68 подаются соответствующие младшие нечетный и четный разряды множителя. Содержимое регистра 75.1, соответствующее предыдущему такту, принимается регистром 76.1 для хранения. По окончании времени суммирования третьим тактовым сигналом результаты суммирования запоминаются в соответствующих регистрах 47,59 и 24,28 . частичных сумм и переносов. Содержимое регистров 46 и 50 принимается соответственно регистрами 50 и 62. 8третьем такте фронт распространения результата достигает сумматоров 3,7, 9и 13. Содержимое регистра 76. 1 принимается регистром 17.If с выхода которого код множимого подается на вход сумматоров 9 и 13, где происходит сложение с двумя младшими разрядами регистров 47 и 51 соответственно, два старших разряда которых запоминаются соответственно в регистрах 51 и 55. Этим обеспечивается сдвиг на два разряда () вправо частичных сумм произведения. В этом же такте в регистр 69 принимается

содержимое регистра 68, а в последНИИ принимается содержимое регистра 67.

В регистр 67 поступают младшие четыре разряда кода множителя третьей пары операндов, первые четыре разряда кода множимого которой прини-маются, в регистр 75.1. В регистр 75.2 поступает вторая группа разрядов кода множимого второй пары, а э регистр 75.3 - третья группа первой пары, с. выхода которого код множи-. мого поступает на вход сумматоров 3 и 7, на стробирующие входы которых с выходарегистра.69 подаются младшие нечетный и четный разряды кода множителя соответственно, а два нечетных и четных разряда поступают соответственйо на стробирующие входы сумматоров 9 и 13. По четвертому тактовому сигналу . результаты суммирований сумматоров 3, и 7 и 9, и 13 запоминаются в ссютветствующих регистрах 48,52, 54 и 58 частичных сумм и регистрах 25,29, 31 и 35 переносов. На сумматоре 17 . происходит коррекция ошибки, возникающей из-за умножения со сдвигом на два разряда. Для этого на вход сумматора 17 подаются результаты сложения на сумматорах 1 и 2, задержанных регистрами 50,62 и 54, и младший разряд результата сложениясумматора 9 через регистр 54. Таким образом, на коррекцию ошибки дополнительное время не затрачивается.

Во входной регистр 67 принимается младшие четыре разряда кода множителя четвертой пары операндов, в реги-стр 75.1 - младшие четыре разряда кода множимого этой же пары операндов, а в регистр 75.4 - последние четыре разряда кода множимого, первой пары операндов. Происходит дальнейшее продвижение кодов сомножителей соответственно по. цепям регистров 75-78 и 67-70.

В Четвертом такте в работу устрой: ства включаются сумматоры 4, 8, 10 и 14. На cjTuiMaTopax происходит суммирование последней группы разрядов кода множимого первой пары операндов, стробируемых четным и не.четным разрядами множителя, подаваемь1ми с выхода регистра 70, два старших четных и нечетных «разряда которого поступают на стробирующие входы суммалоров 10 и 14 соответственно. На информационные входы сумматоров 10 и 14 с выхода регистра 78.2 подается код множимого. Происходит суммирование кода множимого с двумя старшими разрядами результата суммирова-г ния на сумматорах 2,6, задержанных в регистрах 51 и 55 и с двумя младшими разрядами результата суммирования сумматоров 3 и 7. В этом же такте в регистр 67 принимается первая

группа разрядов кода множителя четвертой пары операндов, а в регистр 75.1 - первая группа разрядов кода множимого этой же пары. Происходит дальнейшее продвижение кодов сомножителей -по соответствующим цепям регистров 67-72 и75-80.

По пятому тактовому сигналу результаты суммирования на сумматорах 10 и 14 запоминаются в регистрах 55

0 и 59. С выхода регистра 55 младший разряд старшей информационной группы результата поступает на вход сумматора 18, где происходит форми- рование первой группы разрядов про5межуточного результата первого шага умножения, на другие входы этого сумматора поступают результаты суммирования на сумматорах 9 и 13, задержанные соответственно регистрами 54,58 и 63. Результат суммирования

0 на сумматоре 18 в следующем такте .может быть выведен во внешнюю шину 82 в случае необходимости..работы с удвоенной разрядной сеткой.

В этом же такте в регистр 75.1

5 принимается первая группа разрядов кода множимого пятой пары- операндов, а в регистр 67 -. первая группа разрядов кода множителя этой же. пары. Происходит дальнейшее продвижение

0 кодов сомножителей по цепям регистров 75-80 и 67-71.

ШестЬ|М тактовым сигналом в устройство вводится код сомножителей шестой пары операндов. На сумматоре 19

5 начинается формирование второй группы разрядов промежуточного результата первого шага умножения. На вход этого сумматора подается младший разряд результата суммирования сумматора 11 через регистр 56 и результаты сумми0рования на сумматорах.10 и 14, задержанные в соответствующих регистрах 55 и 59. Осуществляется дальнейшее продвижение кодов сомножителей по цепям регистров -75-80 и 67-72.

5

Седьмым тактовьм сигналом результат .суммирования сумматора 19 заносится в буферный регистр 81.1, а содержимое регистра 80.1 принимается в регистр 75.1. Одновременно с этим

0 по входной шине 73 в регистр 67 принимается вторая группа разрядов кода множителя первой пары операндов. Начинается второй шаг умножения.

Второй, третий и четвертые шаги

5 выполняются аналогично.

В любом шаге умножения может быть произведена коррекция со стороны множимого путем введения дополнения

0 его на свободные входы сумматоров 5-8 второй строки матрицы. Кроме того, эти же сумматоры могут быть использованы для сложения результата- . умножения с третьим операндом, ко5торое подается на вход устройства в

начале первого шага умножения путем , введения его в буферный регистр 81.

Для повышения точности умножения в каждом шаге умножения производится коррекция результата на первом сумматоре последней строки матрицы.

Таким образом, введение дополнительной строки сумматоров и регистров частичных сумм позволяет организовать умножение двумя параллельными ветвями одновременно со сдвигом промежуточных сумм на два разряда в

каждой ветви, что приводит к увеличению быстродействия уртройства при незначительных аппаратурных затратах.

5 I в предлагаемом устройстве возможт но одновременное умножение шести пар операндов с вдвое большей скоростью, чем у известного, за счет чего увеличивается производительность и, следовательно, эффективность устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для умножения двух празрядных чисел | 1977 |

|

SU623204A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-09-23—Публикация

1981-07-30—Подача