(5) МАТРИЧНОЕ УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричное вычислительное устройство | 1982 |

|

SU1034032A1 |

| Матричный умножитель по модулю чисел Ферма | 1990 |

|

SU1783513A1 |

| Устройство для умножения | 1979 |

|

SU911514A1 |

| Устройство для умножения | 1989 |

|

SU1770960A1 |

| Устройство для умножения с накоплением | 1986 |

|

SU1310810A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU938282A1 |

| Матричное вычислительное устройство | 1983 |

|

SU1149245A1 |

| Устройство для умножения с накоплением | 1982 |

|

SU1108087A1 |

| Устройство для умножения | 1989 |

|

SU1714592A1 |

| Матричное вычислительное устройство | 1988 |

|

SU1541599A1 |

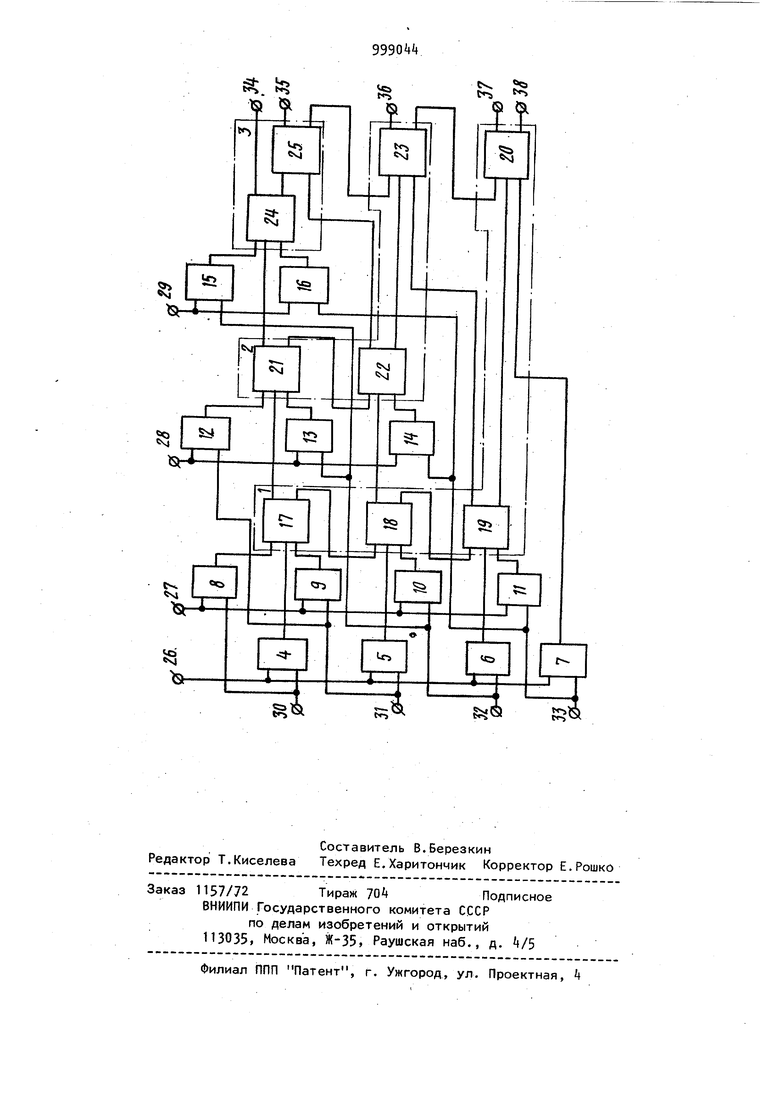

Изобретение относится к вычислительной технике и быть исполь-ч зрвано в специализированных вычислительных машинах. Известно устройство для умножения содержащее регистры множимого и мно жителя, выходы которых поразрядно со динены с входами квадратной матрицы из однородных модулей сложения, соединенных между собой с необходимым для умножения сдвигом tO. Известно матричное устройство для умножения, в котором используется квадратная матрица из п рядов элементов И и (п-1) рядов одноразрядных сумматоров, выходы переноса которых, кроме последних в столбце, соединены с первыми входами сумматоров старшей строки одноименных столбцов, а выходы суммы соединены с вторыми вхоцами сумматоров старшего столбца одноименной строки. К третьим входам Ьумматоров подключены выходы элементов И, первые входы i-ой строки которых (i 1,2,... ,п) соединены с .1-ым разрядом регистра множимого, а вторые входы j-го столбца (j 1,2, ...,п)-с j-ым разрядом регистра множителя, выходы элементов И первого, столбца подключены к вторым входам сумматоров второго столбца 23 . Недостатком этих устройств является большое количество оборудования. Наиболее близким к изобретению является матричное устройство для умножения, содержащее п групп элементов И и (п-1) сумматоров (п - разрядность операндов),первые входы элементов И каждой группы соединены с входом соответствующего разряда первого операнда, вторые входы К-ых элементов И каждой группы (,...,п) соединены с входом К-го разряда вто-рого операнда, выходы элементов И первой группы соединены с входами первой группы соответствующих разрядов первого сумматора, выход первого элемента И j-и группы (,...,п-1) - 399 соединен с первым входом первого раз ряда j-ro сумматора, выход суммы V-ro разряда W-ro сумматора (V 1, ... п-1; W 1,...,п-2) соединен с первым входом (V + 1)-го разряда (W 1)-го сумматора, второй вход V-ro разряда j-сумматора соединен с выходом (V + 1)-го элемента И (+) группы, второй вход первого разряда V-ro сумматора соединен с выходом пе реноса {V + 1)-го сумматора, выход переноса первого сумматора, выходы суммы первых разрядов всех сумматоро и всех разрядов (п-1)-го сумматора и выход первого элемента И п-ой группы соединен с выходами устройства СЗ. Недостатком этого устройства явля ется большое количество оборудования Цельюизобретения является сокращение количества оборудования. Для достижения поставленной цели в матричном устройстве для умножения содержащем п групп элементов И и (п-1) сумматоров (п - разрядность операндов), первые входы элементов И каждой группы соединены с входом соответствующего разряда первого операнда, вторые входы К-ых элементо И первой и второй групп (К 1,...,п соединены с входом К-го разряда второго операнда, второй вход 1-го элемента И т-й группы (,...,n; , ,.., n-m+2) соединен с входом (1+т - 2)-го разряда второго операнда, выходы элементов И .первой труппы соединены с входами первой группы со ответствующих разрядов первого сумматора, выход суммы р-го разряда q-ro сумматора (q-1,...,п-2; р 1, ..., n-q) соединен с первым входом р- го разряда (q + 1)-го сумматора, выход г-го элемента И S-й группы (S 2, ..., п; г. 2,... , n-S + 2) соединен с вторым входом (г-1)-го разряда (S-l)-ro сумматора, второй вход (n-i+l)-ro разряда 1-го сумматора соединен с выходом переноса (n-i)-ro разряда (i+1)-го сумматора (1 1,..., п-1), выходы суммы (n-tf +1)-ых разрядов t- ых сумматоров (t 2,..,, п-2)-и выходы суммы и пе реноса п-го разряда первого сумматоРО соединены с выходами устройства, выход первого элемента И S-- ой групп соединен с входом переноса (S-l)-ro сумматора. На чертеже приведена структурная схема матричного устройства для умножения двух четырехразрядных двоичных чисел. Устройство содержит сумматоры 1-3, элементы И 4-16.Сумматор 1 составляют одноразрядные сумматоры 17-20 , сумматор 2 составляют одноразрядные сумматоры 21 и 23, сумматор 3 составляют одноразрядные сумматоры 24 и 25- На входы 26-29 подается значение первого операнда, на входы 30-33 - значение второго С выходов 3-1-38 снимается операнда. значение результата (, произведения ). Выходы элементов И 4-7, предназначенных для образования первого час- тичного произведения, подключены к входам одноразрядных сумматоров 17-20. Второе частичное произведение образуется элементами И 8-11, выходы которых подключены к входам сумматоров 17-19- Третье и четвертое укороченное частичное произведение образуется элементами И12-14,15-16 соотвественно, выходы которых подключены к входам сумматоров 21, 22 и 24. Выходы суммы сумматоров 17. 18 и 21 подключены к входам сумматоров 21, 22и 24, соответственно, а выходы переноса ко входам сумматоров 18, 19 и 22, соответственно. . Выходы суммы сумматоров 19 и 22 подключены ко входам сумматоров 23 и 23 соответственно, а выходы переноса - к входам сумматоров 20 и 23, соответственно. Выход суммы сумматора 24 является выходом нулевого разряда произведения, который исполь зуется для округления результата, а выход переноса соединен с входом сумматора 25. Выходы сумматоров 25, 23и 20 являются выходами первого, .второго и третьего разрядов произведения. Выходом четвертого разряда произведения является вь1ход переноса сумматора 20. Выход переноса суммаjopa 25 подключен к входу сумматора 23, выход переноса которого соединен с входом сумматора 20. Выходы элементов И 8, 12 и 15.подключены к входам сумматоров 17, 21 и 24, соответственно. Устройство реализует метод сокращенного умножения, сущность которого заключается в следующем. Умножение начиноется со старшего разряда множителя , затем отбрасывается по-ледняя цифра множимого и производится умножение укороченного мнох(имого на (п-1)-й разряд множителя. Частичные произведения складываются. Полученны результат корректируется, т.е. к noлученной сумме добавляется округленное произведение отброшенной цифры на (п-О-й разряд. Затем вновь отбра сывается очередная цифра множимого и производится умножение на (п-2)-й разряд, результат прибавляется к сум ме произведений и корректируется и т.д. Применение этого метода позволя ет вычислять только п значащих цифр произведения, учитывал при этом единицы переноса из младших разрядов. Устройство позволяет сократить количество используемых элементов. Так количество элементов И снижается с п в известном устройстве до n(n--i; в данном устройстве, сумматоров с (п-1) до а количество /t(n--l) + n-i). 2 Формула изобретения Матричное устройство для умножения, содержащее п групп элементов И и (п-1)сумматоров (п-разрядность операндов), первые-входы элементов И каждой- группы соединены со входом соответствующего разряда первого операнда, вторые входы К-ых элементо И первой и второй групп (К 1,,..,п соединены со входом К-го разряда второго операнда, второй вход 1-го элемента И т-ой группы (,...,n; 1 1,.., ,n--m+2) соединен с входом 9 (1+т-2)-го разряда второго операнда, выходы элементов И первой группы соединены со входами первой группы соответствующих разрядов первого сумматора, выход суммы р-го разряда q-ro сумматора (,...,п-2; ,..., n-q) соединен с первым входом р-го разряда (q+1)-ro сумматора, выход г-го элемента И S-й группы (,...,п; ,...,n-S+2) соединен с вторым входом (r-l)-ro разряда (S-l)-ro сумматора, второй вход (п- + 1)-го разряда j-го сумматора соединен с выходом переноса ()-ro разряда (К1)-го сумматора (1 1,. ... , п-1), выходы суммы разрядов (п-1)-го сумматора, выходы суммы (п-1+1)-ых разрядов t-ых сумматоров (t 2,..., п-2) и выходы суммы и переноса п-го разряда первого сумматора соединены с выходами устройства, отличающееся, тем, что, с целью сокращения количества оборудования, выход первого элемента И S-й группы соединен со входом переноса (S-l)-ro сумматора. Источники информации, принятые во внимание при экспертизе 1.Патент США № , кл. 235-164, опублик. 1975. 2.Преснухин Л.Н. и др. Цифровые вычислительные машины. М., Высшая школа, 197, с.23. 3.Карцев М.А. и Брик В.А. Вычислительные системы и синхронная арифметика, М., Радио и связь, 1981, с. 180-182, рисЛЛЛ. (прототип).

:5

i

Авторы

Даты

1983-02-23—Публикация

1981-03-27—Подача