Изобретение относится к цифровой выч лительной технике. В основном авт. св. № 48О077 описано устройство вычисления сумм про изведений, содержащее регистры множимо и множителя, сумматор и матрицу модулей, выход которой соединен со входом сумматора, а входы подключены к выход регистров множимого и множителя 1J. Время вычисления суммы К парных произведений И - разрядных чисел может быть вычислено по формуле: + iaanK l i s) где: te - время прохождения сигнала через вентиль, ij,- время суммирования на одно разрядном модуле J запоминания суммы и переноса на одноразрядном модуле (t.,on- tr т - количество тактов, необходимых для умножения и суммирования К пар чисел (т К } ; количество тактов, затрачиваемых на умножение и суммирование 2ппар нулевых значений множимого и множителя ( ) i ж о- количество тактов, необходимых для суммирования переносов, возникающих в сумматоре 4 (mj-Sog k-n-i) Р - основание системы счисления, Недостатком этого устройства является малое быстродействие, обусловленное тем, что в устройстве затрачивается дополнительно (inj + inj 3h-teo pk-i) тактов для получения окончательного результата в сумматоре. Количество дополнительных тактов может превышать число основных (.К) тактов и при многократном обращении к устройству (например, в задаче перемножения матриц) непроизводительное время может достигать большой величины. Цель изобретения - повышение быстродействия устройства. Это достигается тем, что в устройств введен блок анализа, входы которого подкгаочены к выходам суммы всех столбцов, кроме первого, и к выходам переноса матрицы модулей, а выход подключен к управлющему входу сумматора.

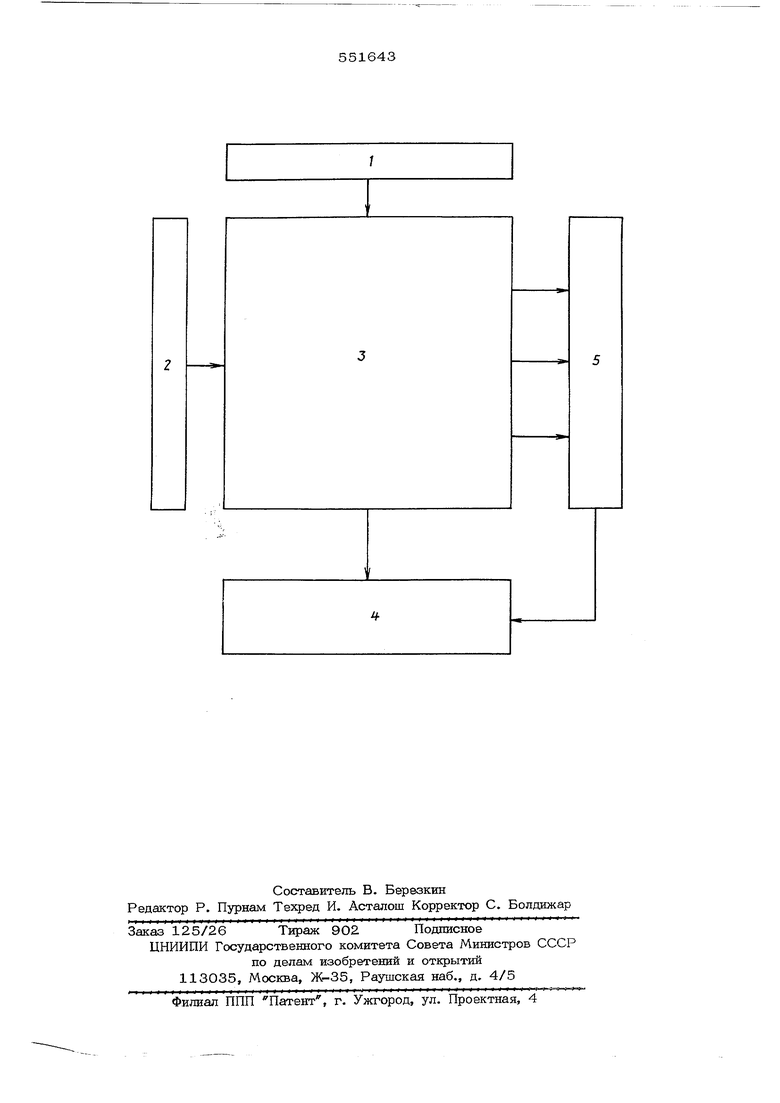

Схема предлагаемого устройства пред- ставлена на чертеже и содержит регистры мномого 1 и множителя 2, матрицу модулей 3, сумматор 4 и блок анализа 5.

Первые и вторые входы матрицы модулей 3 соединены с выходами соответственно регист ра множимого 1 и регистра множителя 2, а выход матрицы модулей 3 соединен со входом сумматора 4. Блок анализа 5 подключен выходом к управляющему входу сумматора 4, а входами - к выходам перено- са матрицы модулей 3, и выходами сумм, кроме первого столбца, матрицы модулей 3

Предлагаемое устройство работает следующим образом.

В качестве модулей в матрице 3 могут быть использованы одноразрядные трехвхо- довые сумматоры с запоминанием суммы и переноса и с одноразрядной схемой умножения на одном из входов. На первые входы матрицы модулей 3 поступают коды множимого первой пары чисел с регистра множимого 1. На вторые входы матрицы модулей 3 поступают коды множителя первой пары чисел с регистра множителя 2. Результаты поразрядного перемножения множимого и множителя запоминаются в матрице модулей 3. На следующем такте с регистра множимого 1 и регистра множителя 2 на первые и вторые входы матрицы модулей 3 поступают соответственно коды множимого и множителя второй пары чисел. Частичное произведение второй пары чисел поразрядно суммируется в матрице модулей 3 с полученными в первом такте значениями частичного произведения первой пары чисел,сдви- нутыми на один разряд вправо и вниз. Результаты умножения и суммирования запоминаются в матрице модулей 3, Аналогично осуществляется умножение и суммирование остальных пар чисел. При этом поразрядные значения сумм и старших разрядов и переноса старшего разряда, полученные на выходе матрицы модулей 3, суммируются с помощью сумматора 4.

После умножения и суммирования К пар чисел осуществляют умножение и суммирование нулевых значений множимого и множителя, в результате чего значения поразрядных сумм и переносов выходят из матрицы модулей 3 и суммируются в сумматоре 4. Количество нулевых тактов определяется с помощью блока анализа 5, который анализирует состояние триггеров суммы и переноса матрицы моделей 3. Когда все триггеры переноса и триггеры суммы, кроме первого столбца матрицы модулей 3, находятся в нулевом состоянии, схема анализа 5 выдает сигнал на управляющий вход сумматора 4. После прохождения сквоного переноса в сумматоре 4 получается результат вычислений суммы парных произведений, причем младшие разряды этого результата устанавливаются на выходах первого столбца матрицы модулей 3, а старшие разряды результата получаются в сумматоре 4.

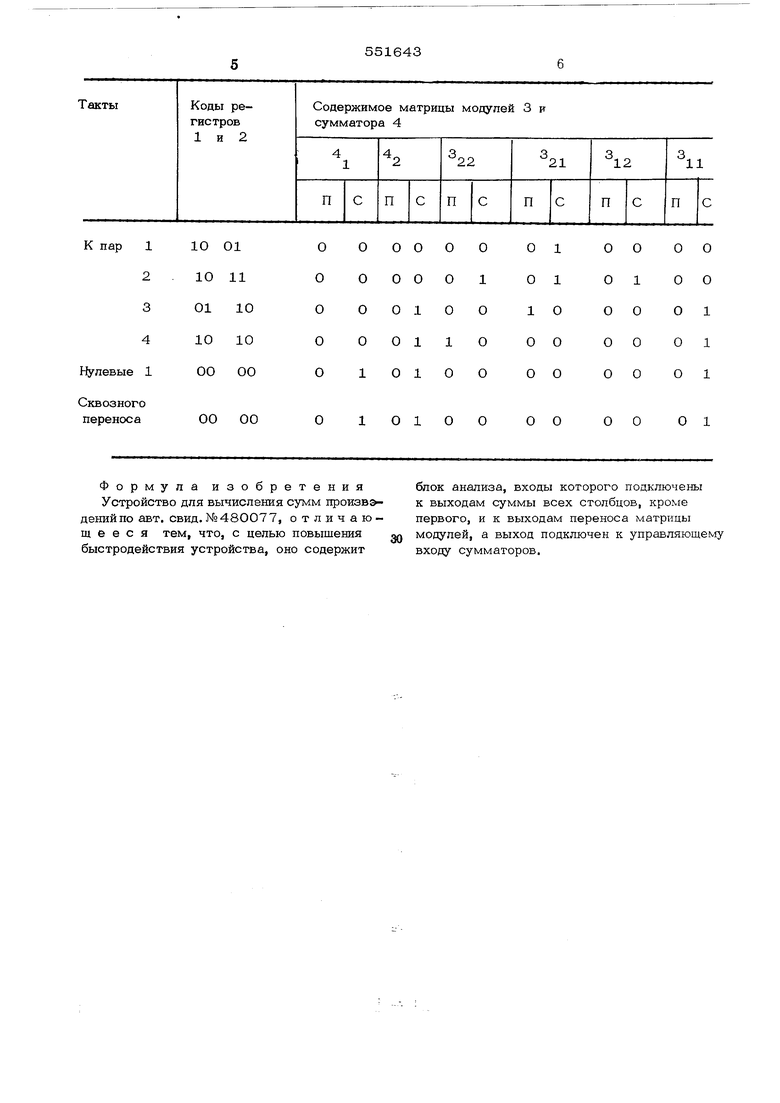

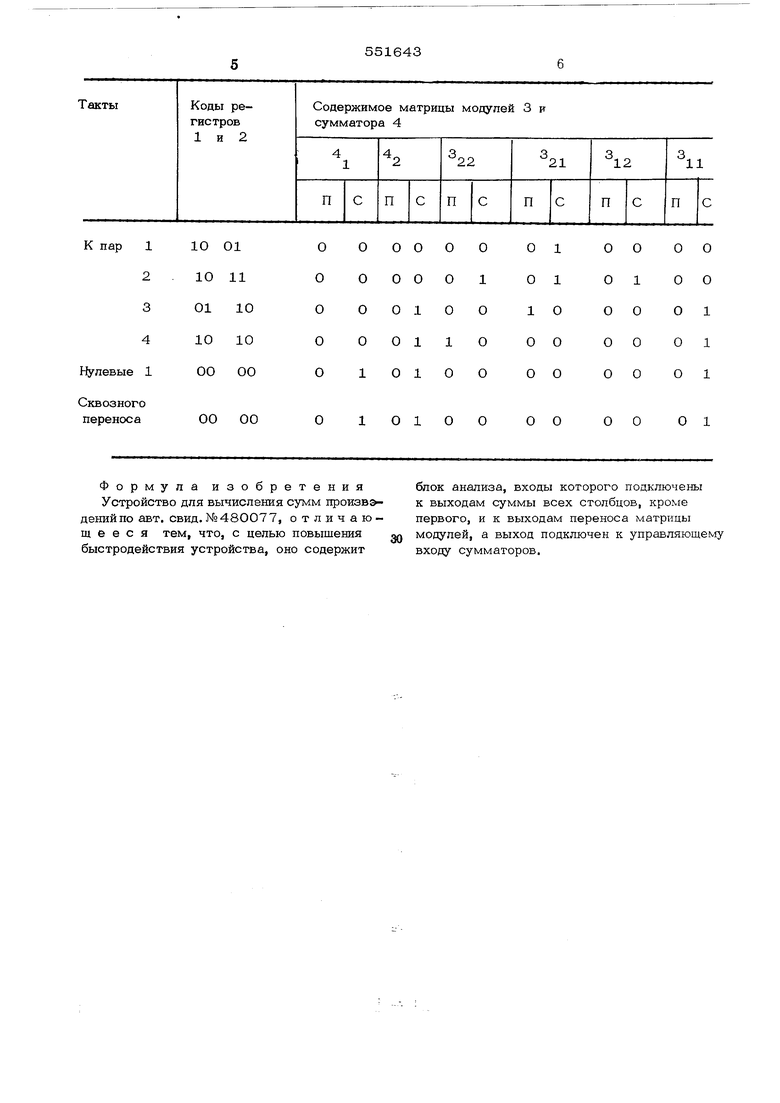

Для иллюстрации работы предлагаемого устройства рассмотрим пример вычисления суммы парных произведений чисел, представленных в двоичном коде:

Х 0,10x0,01 + 0,10x0,11 + 0,01x0,01 0,10 хО,10. Результаты вычислений сведены в таблицу, в которой использованы еле

дуюшие обозначения: П и С - коды на выходе соответственно переноса и суммы матрицы модулей 3. Искомый результат (0,1101 13/16/) получен за 6 тактов, из которых один такт затрачен на вьтод информации из матрицы модулей 3, после чего с блока анализа 5 выдается сигнал на управляющий вход сумматора 4, и один такт затрачен на сквозной перенос в сумматоре 4.

В предлагаемом устройстве существенно повысилось быстродействие по сравнению с быстродействием известных устройст за счет сокращения холостых тактов. Предлагаемое устройство может применяться при решении задач векторной алгебры, общее время решения которых зависит от быстродействия данного устройства.

Формула изобретенияблок анализа, входы которого подключены

Устройство для вычисления сумм произв -к выходам суммы всех столбцов, кроме

денийпо авт. свид. №480077, отличаю-первого, и к выходам переноса матрицы

щ е е с я тем, что, с целью повышения модулей, а выход подключен к управляющему

быстродействия устройства, оно содержитвходу сумматоров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления сумм произведений | 1973 |

|

SU480077A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU938282A1 |

| Устройство для умножения | 1980 |

|

SU960805A1 |

| Устройство для вычисления сумм произведений | 1975 |

|

SU550637A1 |

| Вычислительное устройство | 1988 |

|

SU1647553A1 |

| УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249845C1 |

| Устройство для вычисления сумм произведений | 1975 |

|

SU561963A2 |

| Устройство для умножения | 1982 |

|

SU1038937A1 |

| СПОСОБ ОРГАНИЗАЦИИ УМНОЖЕНИЯ ЧИСЕЛ С ПЛАВАЮЩЕЙ ЗАПЯТОЙ, ПРЕДСТАВЛЕННЫХ В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 2012 |

|

RU2500018C1 |

| СПОСОБ ДЕЛЕНИЯ ЦЕЛЫХ ДВОИЧНЫХ ЧИСЕЛ БЕЗ ОСТАТКА НАЧИНАЯ С МЛАДШИХ РАЗРЯДОВ | 2012 |

|

RU2498393C1 |

Авторы

Даты

1977-03-25—Публикация

1975-10-30—Подача